High-Speed PAM Signal Generation and BER Measurement

... (a) Function for varying data phase between channels with high accuracy (b) High-quality waveforms (low Jitter, low waveform distortion, high-speed Rise and Fall times) To reduce the PAM signal Jitter, the phase of the data between the multiple PPGs used to generate the PAM signal must have the exac ...

... (a) Function for varying data phase between channels with high accuracy (b) High-quality waveforms (low Jitter, low waveform distortion, high-speed Rise and Fall times) To reduce the PAM signal Jitter, the phase of the data between the multiple PPGs used to generate the PAM signal must have the exac ...

a CMOS 80 MHz Monolithic 256 24(18) Color Palette RAM

... permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect dev ...

... permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect dev ...

IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)

... transistor logic (PTL)-based AND gate to control the discharge of transistor N1. Since the two inputs to the AND logic are mostly complementary (except during the transition edges of the clock), the output node Z is kept at zero most of the time. When both input signals equal to “0” (during the fall ...

... transistor logic (PTL)-based AND gate to control the discharge of transistor N1. Since the two inputs to the AND logic are mostly complementary (except during the transition edges of the clock), the output node Z is kept at zero most of the time. When both input signals equal to “0” (during the fall ...

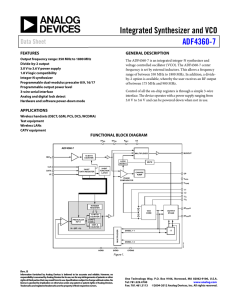

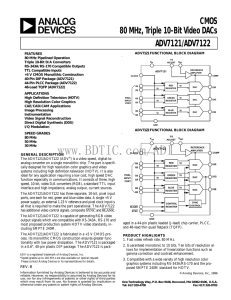

ADV7122 数据手册DataSheet 下载

... most proposed production system HDTV video standards, including SMPTE 240M. The ADV7121/ADV7122 is fabricated in a +5 V CMOS process. Its monolithic CMOS construction ensures greater functionality with low power dissipation. The ADV7121 is packaged in a 0.6", 40-pin plastic DIP package. The ADV7122 ...

... most proposed production system HDTV video standards, including SMPTE 240M. The ADV7121/ADV7122 is fabricated in a +5 V CMOS process. Its monolithic CMOS construction ensures greater functionality with low power dissipation. The ADV7121 is packaged in a 0.6", 40-pin plastic DIP package. The ADV7122 ...

Direct Measurement

... Measurements: 1. Make Measurements several Times 2. Make Measurements on Several Instruments 3. Make successive Measurements on different parts of instruments (different parts of ruler) ...

... Measurements: 1. Make Measurements several Times 2. Make Measurements on Several Instruments 3. Make successive Measurements on different parts of instruments (different parts of ruler) ...

lecture_13_Analog_to_Digital_convertorETEC6416

... • Normally, many data acquisition systems have more than one ADC channels. • PIC16F877a have 11 Analog channels and it can accept 11 analog sources to be digitized but only one input channel can be digitized at a time. ...

... • Normally, many data acquisition systems have more than one ADC channels. • PIC16F877a have 11 Analog channels and it can accept 11 analog sources to be digitized but only one input channel can be digitized at a time. ...

Cypress` CapSense Successive Approximation Algorithm

... physical sensor itself is typically a copper trace constructed on a PCB. Sensors can be any conductive material. For example, one could use indium tin oxide (ITO) and print the pattern on a transparent substrate. Figure 1. Capacitive Sensor ...

... physical sensor itself is typically a copper trace constructed on a PCB. Sensors can be any conductive material. For example, one could use indium tin oxide (ITO) and print the pattern on a transparent substrate. Figure 1. Capacitive Sensor ...

VLSI Design Homework 2

... 【Target: Layout practice with more complicated circuits】 【Description】: In Homework 2, you have learned the basic layout skills, and several simple logical gates are drawn with their netlists being extracted for simulation. In Homework 3, more complicated circuits are drawn with the concept of modul ...

... 【Target: Layout practice with more complicated circuits】 【Description】: In Homework 2, you have learned the basic layout skills, and several simple logical gates are drawn with their netlists being extracted for simulation. In Homework 3, more complicated circuits are drawn with the concept of modul ...

AC Characteristics of MM74HC High-Speed CMOS

... Typically, small signal gains for a MM74HC gate is greater than 1000 and, if input signals spend appreciable time between logic states, noise on the input or power supply will cause the output to oscillate during this transition. This oscillation could cause logic errors in the user’s circuit as wel ...

... Typically, small signal gains for a MM74HC gate is greater than 1000 and, if input signals spend appreciable time between logic states, noise on the input or power supply will cause the output to oscillate during this transition. This oscillation could cause logic errors in the user’s circuit as wel ...

HMC854LC5

... 5. PACKAGE WARP SHALL NOT EXCEED 0.05mm DATUM -C6. ALL GROUND LEADS MUST BE SOLDERED TO PCB RF GROUND. ...

... 5. PACKAGE WARP SHALL NOT EXCEED 0.05mm DATUM -C6. ALL GROUND LEADS MUST BE SOLDERED TO PCB RF GROUND. ...

Images SI Stepper Motor Controller Datasheet

... input is made low, Stepper Motor will advance to 1001 state instead of 0001 on next falling edge of external Step Clock in Slave Mode or next internally generated clock cycle in Free Running Mode. If current state of Stepper Motor is 0001 i,e 1 Phase Drive & H/F input is made low, Stepper Motor will ...

... input is made low, Stepper Motor will advance to 1001 state instead of 0001 on next falling edge of external Step Clock in Slave Mode or next internally generated clock cycle in Free Running Mode. If current state of Stepper Motor is 0001 i,e 1 Phase Drive & H/F input is made low, Stepper Motor will ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.