TPS543C20 4 Vin to 16 Vin, 40-A Stackable, Synchronous Step

... IOUT ≥ 20 A/phase among stackable devices, defined as the ratio of the current IOUT ≤ 20 A/phase difference between devices to ...

... IOUT ≥ 20 A/phase among stackable devices, defined as the ratio of the current IOUT ≤ 20 A/phase difference between devices to ...

MAX9157 Quad Bus LVDS Transceiver General Description Features

... voltage transition time = 1ns (20% to 80%). Input common-mode voltage VCM = 1.2V to 1.8V, DE_ = high, RE_ = low, TA = -40°C to +85°C, unless otherwise noted. Typical values are at VCC = 3.3V, |VID| = 0.2V, VCM = 1.2V, and TA = +25°C.) (Notes 3 and 5) ...

... voltage transition time = 1ns (20% to 80%). Input common-mode voltage VCM = 1.2V to 1.8V, DE_ = high, RE_ = low, TA = -40°C to +85°C, unless otherwise noted. Typical values are at VCC = 3.3V, |VID| = 0.2V, VCM = 1.2V, and TA = +25°C.) (Notes 3 and 5) ...

PAM8303C Description Pin Assignments

... capacitor is the leakage path from the input source through the input network (CI, RI + RF) to the load. This leakage current creates a DC offset voltage at the input to the amplifier that reduces useful headroom, especially in high gain applications. For this reason, a low-leakage tantalum or ceram ...

... capacitor is the leakage path from the input source through the input network (CI, RI + RF) to the load. This leakage current creates a DC offset voltage at the input to the amplifier that reduces useful headroom, especially in high gain applications. For this reason, a low-leakage tantalum or ceram ...

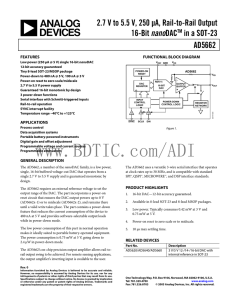

2.7 V to 5.5 V, 250 µA, Rail-to-Rail Output nano AD5662

... goes low, it enables the input shift register, and data is transferred in on the falling edges of the following clocks. The DAC is updated following the 24th clock cycle unless SYNC is taken high before this edge, in which case the rising edge of SYNC acts as an interrupt and the write sequence is i ...

... goes low, it enables the input shift register, and data is transferred in on the falling edges of the following clocks. The DAC is updated following the 24th clock cycle unless SYNC is taken high before this edge, in which case the rising edge of SYNC acts as an interrupt and the write sequence is i ...

MAX1190 Dual 10-Bit, 120Msps, 3.3V, Low-Power ADC General Description

... The MAX1190 features parallel, CMOS-compatible threestate outputs. The digital output format can be set to two’s complement or straight offset binary through a single control pin. The device provides for a separate output power supply of 1.7V to 3.6V for flexible interfacing with various logic famil ...

... The MAX1190 features parallel, CMOS-compatible threestate outputs. The digital output format can be set to two’s complement or straight offset binary through a single control pin. The device provides for a separate output power supply of 1.7V to 3.6V for flexible interfacing with various logic famil ...

UCC28521 数据资料 dataSheet 下载

... where, DMAX is a dimensionless ratio VDX is the voltage at D_MAX in volts This pin can also be used to set DMAX to 0 by setting VDX less than 0.7 V. ...

... where, DMAX is a dimensionless ratio VDX is the voltage at D_MAX in volts This pin can also be used to set DMAX to 0 by setting VDX less than 0.7 V. ...

2.5 Signal Sources Word Document | GCE AS/A

... an electronic system can be constructed from individual components, e.g. time delays and pulse generators or ‘clock’s. In this section we will spend some time looking at how external variations in light or temperature can be converted into a suitably changing electrical signal that can be processed ...

... an electronic system can be constructed from individual components, e.g. time delays and pulse generators or ‘clock’s. In this section we will spend some time looking at how external variations in light or temperature can be converted into a suitably changing electrical signal that can be processed ...

RF2878 3V LOW NOISE AMPLIFIER/ 3V PA DRIVER AMPLIFIER Features

... Moving to another application, consider the schematic for 350MHz LNA. Noise figure in this case=1.75dB. In contrast to above linear driver, bias resistor is set at 1000 to limit current. In the specifications next to schematic, see that input return loss is somewhat degraded at 2.8dB. The absence o ...

... Moving to another application, consider the schematic for 350MHz LNA. Noise figure in this case=1.75dB. In contrast to above linear driver, bias resistor is set at 1000 to limit current. In the specifications next to schematic, see that input return loss is somewhat degraded at 2.8dB. The absence o ...

EE6303 Click here to

... was "very large-scale integration" (VLSI). The development started with hundreds of thousands of transistors in the early 1980s, and continues beyond several billion transistors as of 2007. In 1986 the first one megabit RAM chips were introduced, which contained more than one million transistors. Mi ...

... was "very large-scale integration" (VLSI). The development started with hundreds of thousands of transistors in the early 1980s, and continues beyond several billion transistors as of 2007. In 1986 the first one megabit RAM chips were introduced, which contained more than one million transistors. Mi ...

LTM8029 - 36VIN, 600mA Step-Down μModule Converter with 5μA Quiescent Current

... 5μA of quiescent current. The LTM8029 can accept an input as high as 36VIN and operates at low input voltages due to its off-time skipping capability. Burst Mode operation maintains high efficiency at low output currents while keeping the output ripple low. The RUN pin features an accurate threshold ...

... 5μA of quiescent current. The LTM8029 can accept an input as high as 36VIN and operates at low input voltages due to its off-time skipping capability. Burst Mode operation maintains high efficiency at low output currents while keeping the output ripple low. The RUN pin features an accurate threshold ...

FET Biasing - Dr Ali El

... The problem is that how long does the transfer characteristics have to be draw? We have to analyze the input loop parameter relationship. As RS become smaller, the linear characteristics will be in narrow slope therefore needs to consider the extend of transfer characteristics for example of vol ...

... The problem is that how long does the transfer characteristics have to be draw? We have to analyze the input loop parameter relationship. As RS become smaller, the linear characteristics will be in narrow slope therefore needs to consider the extend of transfer characteristics for example of vol ...

PAM8404 Description Pin Assignments

... capacitor should face the amplifier input in most applications as the DC level is held at VDD/2, which is likely higher than the source DC level. Please note that it is important to confirm the capacitor polarity in the application. If the corner frequency is within the audio band, the capacitors sh ...

... capacitor should face the amplifier input in most applications as the DC level is held at VDD/2, which is likely higher than the source DC level. Please note that it is important to confirm the capacitor polarity in the application. If the corner frequency is within the audio band, the capacitors sh ...

M CMOS-MEMS R

... transduction is achieved measuring electrical frequency responses with high peaks (up to 20 dB or more) and large phase shifts (up to 160º) around the resonance frequency. Measurements showing soft/hard-spring effect and hysteretic performance due to nonlinearities are also reported as well as the d ...

... transduction is achieved measuring electrical frequency responses with high peaks (up to 20 dB or more) and large phase shifts (up to 160º) around the resonance frequency. Measurements showing soft/hard-spring effect and hysteretic performance due to nonlinearities are also reported as well as the d ...