* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Q.1 What is the lowest positive integer whose Least significant digit

Survey

Document related concepts

Wien bridge oscillator wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Integrating ADC wikipedia , lookup

Schmitt trigger wikipedia , lookup

Regenerative circuit wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Operational amplifier wikipedia , lookup

Two-port network wikipedia , lookup

RLC circuit wikipedia , lookup

Phase-locked loop wikipedia , lookup

Index of electronics articles wikipedia , lookup

Opto-isolator wikipedia , lookup

Integrated circuit wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Transcript

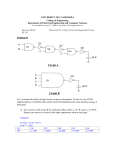

Q.1 What is the lowest positive integer whose Least significant digit when moved to Most significant position the new number is 3/5(or 3/4th) of original. (110) Q.2 Some question on rotational speed of big wheel and small wheel. Q.3 Some question on Big endian integers. Q.4 To draw state transition diagram of combinational circuit counting number of ‘consecutive ones pairs’ in continuous input stream. Counting is mod 4 i.e returns to 00 after counting 11. (011110… has three pairs of consecutive ones). Q.5 Ckt diag for Xor using only inverters and pass transistors. Q.6 Combinational ckt to output 2’s complement of continuous input stream. Q.7 To find maximum clock periods of four circuit of two cascaded D-f/fs having different directions of clock and different position of buffers for delay. Also to find out which circuit won’t work reliably as shift register. Q.8 If in a RISC system a pair of stmt is replaced by a single stmt, to reduce number of stmt, it increases clock period by 10%. If such pairs of stmts occurs 20% of time in source code and only 80% of these are of particular type to be replaced did the performance actually improved. Q.9 True and false (ten) o LFSR’s can’t generate all zero’s pattern. o For each mealy M/C there is Moore and M/C and vice versa. Q.10 not remembered.