* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download ece2201_lab6_modified

Surge protector wikipedia , lookup

Audio power wikipedia , lookup

Standing wave ratio wikipedia , lookup

Phase-locked loop wikipedia , lookup

Integrating ADC wikipedia , lookup

Analog television wikipedia , lookup

Superheterodyne receiver wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Oscilloscope wikipedia , lookup

Power MOSFET wikipedia , lookup

Voltage regulator wikipedia , lookup

Tektronix analog oscilloscopes wikipedia , lookup

Oscilloscope types wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Power electronics wikipedia , lookup

Index of electronics articles wikipedia , lookup

Current source wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Wilson current mirror wikipedia , lookup

Regenerative circuit wikipedia , lookup

Schmitt trigger wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Two-port network wikipedia , lookup

Radio transmitter design wikipedia , lookup

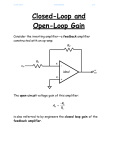

Negative-feedback amplifier wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Current mirror wikipedia , lookup

Oscilloscope history wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Operational amplifier wikipedia , lookup

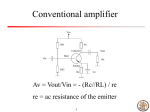

NOTE: Originally written by Prof. J. McNeill Modified 2/21/05 by S. J. Bitar (Parts L1 & L2: RB1 changed to 3k, RC changed to 20k, CL changed to 500pF) ECE 2201 LAB 6 - BJT Applications PRELAB P1. DC CURRENT SOURCE The circuit of Figure P6-1 can be used to create a DC current IOUT. Determine values for resistors RB1, RB2, and RE, (choose the closest standard values from your lab kit) to meet the following conditions: The output current IOUT ≈ 4mA The emitter voltage VE = -13V (that is , a 2V drop across RE) To avoid -dependent biasing: the BJT base current causes no more than a 100mV voltage drop in the Thevenin equivalent resistance of the RB1/RB2 network (assume ≥ 100) To avoid excessive power consumption: the current in the RB1/RB2 network is ≤ 2mA. Assume that VOUT is connected to a voltage that will allow the BJT to operate in the active region VCC = +15V CBP1 0.1µF IOUT VOUT RB1 + VBE - RB2 Q1 2N3904 VE RE CBP2 0.1µF VEE = -15V Figure P6-1. 1 P2. EMITTER FOLLOWER OUTPUT RESISTANCE In the circuit of Figure P6-2, the series resistor RS models the high output resistance (10kΩ) of a signal source that will be required to drive a low resistance (1kΩ) load. Determine the value of the small-signal output resistance Rout “looking into” the output node vOUT. (assume = 100). Assume CC is a short at signal frequencies. NOTE: Remember when looking for small signal impedance at a node, the only operating independent source should be the test source vx applied to the node being analyzed. All other independent sources should be suppressed (set equal to 0); short for independent voltage sources (such as vs in this case) and open for independent current sources (such as IBIAS in this case). VCC = +15V CBP 0.1µF 1 RS 10k Ω Q2 2N3904 Rout CC VS VOUT IBIAS 4m A CBP 0.1µF 2 VEE = -15V Figure P6-2. 2 P3. DIFFERENTIAL AMPLIFIER Find the DC operating point of the differential amplifier circuit of Figure P6-3 (assume = 100). In particular, find the DC values of the following: The DC output voltages VOUT1, VOUT2 The DC emitter voltage VE The DC collector currents IC3, IC4 The DC base currents IB3, IB4 VCC = +15V CBP 0.1µF 1 RC1 51k Ω RC1 51k Ω VOUT2 VOUT1 Q3 2N3904 IC3 IC4 IB3 Q4 2N3904 IB4 VE IBIAS 200µ A CBP 0.1µF 2 VEE = -15V Figure P6-3 3 EE2201 - LAB 6 BJT Applications: Amplifier Bandwidth Limitations DC Current Source Emitter Follower (Unity Gain Buffer) Differential Amplifier Operational Amplifier (Op-amp) PURPOSE: The purpose of this laboratory assignment is to investigate single-stage and multi-stage applications of the NPN and PNP bipolar junction transistors (BJT). Upon completion of this lab you should be able to: Measure the bandwidth of a BJT linear amplifier, and relate the bandwidth to component values (R and C) that set the bandwidth limit Plot frequency response data to produce a magnitude Bode plot for an amplifier transfer function Construct a DC current source for use in biasing an emitter follower and differential pair Use a BJT in the emitter follower configuration to act as a unity gain buffer Use a BJT differential pair to provide gain for differential signals Construct a simple op-amp from a cascaded differential pair (input stage), common emitter amplifier (high gain stage), and emitter follower (output stage) . MATERIALS: ECE Lab Kit DC Power Supply DVM Function Generator Oscilloscope NOTE: Be sure to record ALL results in your laboratory notebook. Terminal designation reminder for BOTH 2N3904 (NPN BJT) AND 2N3906 (PNP BJT): COLLECTOR BASE EMITTER (TOP VIEW) 4 AMPLIFIER BANDWIDTH LIMITATION L1. Build the amplifier circuit shown in Fig. 6-1. This is the common emitter with emitter degeneration from lab 5. Add a 500pF load capacitance on the output node. L2. Adjust the function generator to obtain a sine wave amplitude of approximately 100mV peak at vin. In this part of the lab, you will be changing the frequency to determine the bandwidth (3-dB frequency) and measure the slope of the magnitude “roll-off” above the 3-dB frequency. VCC = +15V RB2 43k Ω + +15V CBP 0.1µF 1 RC 20k Ω VOUT IC CB 100µF Vin Q1 2N3904 + Vs+ (0.1V)sin2f t- CL 500pF VE RB1 3k Ω FUNCTION GENERATOR RE 1k Ω Figure 6-1 L3. Display vIN on oscilloscope channel 1; set the horizontal time scale to show a few cycles of the sine wave. Use AC coupling and a vertical scale of 50mV per division, and adjust the function generator amplitude until the peak level of the signal is ≈ 0.1V (peak-to-peak level of ≈ 200mV). Start with a frequency of 100Hz. L4. Display vOUT on oscilloscope channel 2. Use AC coupling and a vertical scale of 0.5V/div and adjust the vertical position so that 0V (ground) is at the center of the screen. 5 L5. Measure the amplitude of the input and output voltages over the range of frequencies shown in the table below. At higher frequencies, you may need to “zoom in” on the output (increase vertical resolution) as the output amplitude decreases above the 3-dB frequency. Calculate the gain magnitude |av| at each frequency. Also, express the gain in decibels (dB) which for a voltage ratio is 20 log |av| . Nominal Frequency Actual Frequency (measured) |vout| (measured) |vin| (measured) |av| |vout| / |vin| (calculated) |av| [dB] 100 Hz 200 Hz 500 Hz 1 kHz 2 kHz 5 kHz 10 kHz 20 kHz 50 kHz 100 kHz 200 kHz L6. In your lab notebook, plot your measured data in two ways: On linear axes: |av| vs. frequency On log-log axes: |av| in dB as vs. log frequency Since the frequency and gain vary over a wide range, the log-log plot is much more informative for presenting information about the transfer function. L7. Determine the bandwidth (3-dB frequency) f3-dB, the frequency at which the output magnitude is 3-dB down from its maximum value (or, equivalently, equal to 1/√2 times its maximum value). In your lab notebook, compare the measured f3-dB to the predicted value of 1/2RCCL. 6 UNITY GAIN BUFFER APPLICATION: EMITTER FOLLOWER THE PROBLEM: DRIVE LOW RL LOAD FROM HIGH RS SOURCE It is required to drive a 1kΩ load resistor from a source with an output impedance of 10kΩ, as shown in Figure 6-2. The goal is for vOUT = vS. Two approaches will be considered in this section. RS 10k Ω VOUT ? RL 1k Ω VS Figure 6-2 PLAN A: THE DIRECT APPROACH L8. Build the circuit shown in Fig. 6-3. Set the function generator so vS = (2V)sin2(1kHz)t, a 1kHz sine wave with 2V peak amplitude. Display vS on oscilloscope channel 1 and vOUT on channel 2; use DC coupling and a vertical scale of 1V per division. Set the horizontal time scale to show a few cycles of the sine wave. L9. Measure the “gain” |vout|/|vs|. How well does this circuit meet the goal of vOUT = vS? Explain any difficulty in your lab notebook. RS 10k Ω VOUT RL 1k Ω VS Figure 6-3 7 PLAN B: EMITTER FOLLOWER L10. Build the emitter follower circuit of Figure 6-4. The emitter follower is biased by the current source you designed in prelab part P1. VCC = +15V CBP 0.1µF 1 RS 10k Ω RP2 1k Ω VB2 Q2 2N3904 + VS VBE2 - VCC = +15V RB1 + CB 100µF 4 mA Q1 2N3904 + RB2 VE2 EMITTE R FOLLOWER VBE1 - VE1 YOUR CURREN T SOURC E DESIG N FROM PRELAB P1 VOUT RL 1k Ω RE CBP 0.1µF 2 VEE = -15V Figure 6-4. Note that resistor RP2 is solely for protection of Q2, to limit current if vOUT is shorted to ground or –15V. During normal operation the voltage drop across RP2 should be small enough so that the emitter follower transistor Q2 is always in the active region. 8 DC BIAS: CURRENT SOURCE L11. Verify your current source design by measuring the following values: the voltage VE1 at the emitter of Q1, the base-emitter voltage drop VBE1, and the voltage drop across resistor RE. In your lab notebook, calculate the DC emitter current for Q1 and compare to the design value of ≈ 4mA from prelab part P1. EMITTER FOLLOWER OPERATION L12. Set the function generator so vS = (2V)sin2(1kHz)t, a 1kHz sine wave with 2V peak amplitude. Display vB2 (the base of Q2, not the input) on oscilloscope channel 1 and vE2 (the emitter of Q2, not the output) on channel 2; use DC coupling and a vertical scale of 1V per division. Set the horizontal time scale to show a few cycles of the sine wave. In your lab notebook, record the waveforms at vS and vE2. You should see the emitter voltage “following” the base voltage, offset by the VBE = 0.7V drop of Q2’s base-emitter junction. EMITTER FOLLOWER SMALL SIGNAL GAIN L13. Display the input vS on oscilloscope channel 1 and the output vOUT on channel 2; use DC coupling and a vertical scale of 1V per division. Set the horizontal time scale to show a few cycles of the sine wave. Measure |vout|/|vs|. How well does this circuit meet the goal of vOUT = vS? In your lab notebook, compare the performance of the circuits in Plan A vs. Plan B.. 9 DIFFERENTIAL PAIR L14. Modify your circuit (use the same current source configuration, changing resistors to provide a DC current of 200µA) to build the differential amplifier shown in Figure 6-5. VCC = +15V RC1 51k Ω C BP 0.1µF 1 RS1 1k Ω VS RC2 51k Ω OUT1 V Vin OUT2 V Q1 2N3904 Q2 2N3904 RS2 10 Ω E V VCC = +15V 200 µ A RB1 20k Ω C BP 0.1µF 2 Q3 2N3904 RB2 2k Ω RE 10k Ω VEE = -15V Figure 6-5 DC BIAS LEVEL L15. With the signal input set to zero, measure the DC operating conditions: DC voltages VOUT1, VOUT2, and the voltage VE at the differential pair emitters. Also, calculate the DC collector currents IC1 and IC2 by measuring the voltage drop across resistors RC1 and RC2. Record these results in your lab notebook and compare to the values from your analysis in prelab P3. (Note: VOUT1 and VOUT2 may not be equal, due to mismatches in transistors Q1 and Q2) SMALL SIGNAL MODEL PARAMETER CALCULATION L16. From the DC collector currents IC1 and IC2, calculate the incremental emitter resistance re for the small signal model. Calculate RC/2re, the predicted small-signal gain from vin to either output. You will use this to check the small-signal gain you measure in part L21. 10 INPUT ATTENUATOR L17. Since the gain of this amplifier is large, it is necessary to make a very small input voltage (a few millivolts peak-to-peak) to avoid clipping at the output. Resistors RS1 and RS2 form a 100:1 attenuator, so a 0.5V peak sine wave at the function generator produces a 5mV peak (10mV peak-to-peak) sine wave at Vin. Since the 10mV peak-to-peak signal amplitude at the amplifier input Vin is too small to measure directly on the oscilloscope, you’ll measure it indirectly by measuring the amplitude of Vs at the function generator output, and dividing by the attenuation ratio of the voltage divider network (measure RS1 and RS2 to get the correct actual values for the voltage divider expression). DIFFERENTIAL PAIR OPERATION L18. Adjust the function generator to produce a 0.5V peak (1V peak-to-peak) sine wave at 1kHz. This should produce a 10mV peak-to-peak sine wave at Vin. Display vS and vOUT1 on oscilloscope channel 1 and 2. Use DC coupling, set both channels to 2V/div, and adjust the vertical position so that 0V (ground) is near the bottom of the screen. Verify the 180° phase shift (inversion of the sine wave) from input to output vOUT1. L19. Now, change channel 2 to vOUT2. You should see the same amplitude output, but in phase with the input. L20. Change scope channel 1 to vOUT1, so that both outputs are displayed on the scope. You should see two output sine waves, approximately the same amplitude, 180° out of phase, riding on approximately the same DC bias level. SMALL SIGNAL GAIN L21. Measure the input signal peak-to-peak signal amplitude vin(p-p), and the peak-to-peak amplitudes vout1(p-p) and vout2(p-p) of each output. To get an accurate measurement, you may want to go to AC coupling and “zoom in” to a finer vertical scale. Calculate the small signal gain from the input to each differential output. In your lab notebook, compare the measured gains to the prediction in L17. Measurement note: you will have to determine the input amplitude vin(p-p) indirectly as described in L17. LARGE SIGNAL BEHAVIOR L22. While observing the differential outputs on the scope, gradually increase the input signal amplitude until clipping is observed. Note the smooth transition to clipping (limiting) behavior, as well as the symmetric clipping at each output (due to the “balancing” action of the differential pair. In your lab notebook, record the maximum and minimum output voltages at each output. Compare the limits to the theoretical predictions of VCC and VCCIBIASRC. 11 OPERATIONAL AMPLIFIER L23. Build the op-amp circuit shown in Figure 6-6. This is a fairly complicated circuit – be careful and double-check your wiring. Note the use of the 2N3906, a PNP transistor, in the common emitter stage. OPEN LOOP OPERATION L24. Adjust the function generator to provide a 100mV peak, 100Hz sine wave. Apply the sine wave to the open-loop op-amp as shown in Figure 6-7. Display vS on channel 1 at 100mV/div; display vOUT on channel 2 at 5V/div. Use DC coupling and adjust both channels so that ground (0V) is at the center of the display. Adjust the time scale to show a few cycles of the sine wave. You should see vOUT to be a square wave, due to the high openloop gain of the op-amp. Record the scope waveforms in your lab notebook. VIN+ VOUT VS VIN- Figure 6-7 CLOSED LOOP OPERATION L25. Build the closed-loop op-amp circuit shown in Figure 6-8. Adjust the function generator to provide a 100mV peak, 100Hz sine wave for vs. Apply the sine wave to the closed-loop opamp as shown in Figure 6-8. Display vS on channel 1 at 50mV/div; display vOUT on channel 2 at 0.5V/div. Use DC coupling and adjust both channels so that ground (0V) is at the center of the display. Adjust the time scale to show a few cycles of the sine wave. Measure the gain from vS to vout. Compare to the predicted gain (RA+RB)/RA. Record your results in your lab notebook. VIN+ VOUT VS VINRB 100k Ω RA 10k Ω Figure 6-8 12 Figure 6-6 13