* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download 8085 Architecture & Its Assembly language programming

Survey

Document related concepts

Parallel port wikipedia , lookup

Power over Ethernet wikipedia , lookup

Network tap wikipedia , lookup

Asynchronous Transfer Mode wikipedia , lookup

Low Pin Count wikipedia , lookup

Direct memory access wikipedia , lookup

Deep packet inspection wikipedia , lookup

Zero-configuration networking wikipedia , lookup

Serial digital interface wikipedia , lookup

Real-Time Messaging Protocol wikipedia , lookup

Cracking of wireless networks wikipedia , lookup

Transcript

Dr A Sahu

Dept of Comp Sc & Engg.

IIT Guwahati

• PCI Devices

• NIC Cards

–Specific to 82573 (Intel NIC)

–How transmit works

–How receive work

• Network Device Driver

16 doublewords

31

0 31

Status

Command

Register

Register

Cache

Header Latency

Line

BIST

Type

Timer

Size

0 Dwords

Device

Vendor

ID

ID

Class Code

Revision

Class/SubClass/ProgIF

ID

1- 0

3- 2

Base Address 1

Base Address 0

5- 4

Base Address 3

Base Address 2

7- 6

Base Address 5

Base Address 4

9- 8

CardBus CIS Pointer

11 - 10

Expansion ROM Base Address

13 - 12

reserved

15 - 14

Subsystem

Device ID

reserved

Subsystem

Vendor ID

capabilities

pointer

MaximumMinimum Interrupt Interrupt

Latency Grant

Pin

Line

accessed using a large variety of processor

instructions (mov, add, or, shr, push, etc.)

and virtual-to-physical address-translation

memory

space

(4GB)

accessed only by using the processor’s

special ‘in’ and ‘out’ instructions

(without any translation of port-addresses)

i/o space

(64KB)

PCI

configuration

space

(16MB)

i/o-ports 0x0CF8-0x0CFF dedicated to accessing PCI Configuration Space

PCI Configuration Space Address Port (32-bits)

31

CONFADD

( 0x0CF8)

E

N

23

reserved

16 15

bus

(8-bits)

11 10 8 7

device

(5-bits)

function doubleword

(3-bits)

(6-bits)

2 0

00

Enable Configuration Space Mapping (1=yes, 0=no)

PCI Configuration Space Data Port (32-bits)

31

CONFDAT

( 0x0CFC)

0

• Step one: Output the desired longword’s

address (bus, device, function, and dword)

with bit 31 set to 1 (to enable access) to the

Configuration-Space Address-Port

• Step two: Read the designated data from the

Configuration-Space Data-Port

• Already discussed PCI-probes pciprobes.c

– Lect 29..Showing vram, pciprobe.cpp

How ‘transmit’ works

List of Buffer-Descriptors

descriptor0

descriptor1

descriptor2

descriptor3

0

0

0

0

We setup each data-packets that we want to be

transmitted in a ‘Buffer’ area in ram

We also create a list of buffer-descriptors and inform

the NIC of its location and size

Then, when ready, we tell the NIC to ‘Go!’ (i.e., start

transmitting), but let us know when these

transmissions are ‘Done’

Buffer0

Buffer1

Buffer2

Buffer3

Random Access Memory

• Memory-information registers

– TDBA(L/H) = Transmit-Descriptor Base-Address

Low/High (64-bits)

– TDLEN = Transmit-Descriptor array Length

– TDH = Transmit-Descriptor Head

– TDT = Transmit-Descriptor Tail

• Transmit-engine control registers

– TXDCTL = Transmit-Descriptor Control Register

– TCTL = Transmit Control Register

• Notification timing registers

– TIDV = Transmit Interrupt Delay Value

– TADV = Transmit-interrupt Absolute Delay Value

0x00

TDBA

base-address

0x10

0x20

TDLEN

(in bytes)

TDH (head)

0x30

0x40

0x50

0x60

TDT (tail)

0x70

0x80

= owned by hardware (nic)

= owned by software (cpu)

Circular buffer (128-bytes minimum)

31

0

30

29

0

28

0

15

0

27

0

14

0

0

13

0

26

0

12

25

24

23

22

0

G

R

A

N

0

0

11

10

FRC HTHRESH

FRC

0

DPLX

SPD

(Host

Threshold)

9

8

21

20

19

18

17

16

WTHRESH

(Writeback Threshold)

7

6

I

L

0O0

S

00

5

A

S

D

E

4

3

2

1

0

L

PTHRESH

R

0

00 00

(Prefetch

S Threshold)

T

“This register controls the fetching and write back of transmit descriptors.

The three threshhold values are used to determine when descriptors are

read from, and written to, host memory. Their values can be in units of

cache lines or of descriptors (each descriptor is 16 bytes), based on the

value of the GRAN bit (0=cache lines, 1=descriptors). When GRAN = 1,

all descriptors are written back (even if not requested).” --Intel manual

Recommended for 82573: 0x01010000 (GRAN=1, WTHRESH=1)

31

30

29

R

R

R

=0

=0

=0

15

28

27

MULR

14

26

TXCSCMT

13

12

25

24

23

UNO

RTX

RTLC

R

11

COLD (lower 4-bits)

(COLLISION DISTANCE)

EN = Transmit Enable

PSP = Pad Short Packets

CT = Collision Threshold (=0xF)

COLD = Collision Distance (=0x3F)

10

0

=0

9

22

SW

XOFF

8

21

20

19

18

17

16

COLD (upper 6-bits)

(COLLISION DISTANCE)

7

6

5

4

I

S

CT

L

TBI

(COLLISION

ASDV THRESHOLD)

SPEED

L

O

mode

S

U

3

P

S

P

2

1

R0 0E

N

=0

0

R

=0

SWXOFF = Software XOFF Transmission

RLTC = Retransmit on Late Collision

UNORTX = Underrun No Re-Transmit

TXCSCMT = TxDescriptor Minimum Threshold

MULR = Multiple Request Support

82573L

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

Tx

Phy

DF PB

DMA

Tx LS R Pwr

Reserved

RO

Tx

R

R

IAME

PAR PAR

Dyn R

ANE Config ITCE

Flow =0 Down

DIS

=0

=0 EN EN LS(=0)

GE =0

=0

En

15

14

13

12

11

10

9

8

7

6

5

4

3

SPD R EE ASD R R R

R R R R R

TxConfigWord

BYPS =0 RST CHK =0 =0 =0

=0 =0 =0 =0 =0

2

16

1

0

0 0

ANE = Auto-Negotiation Enable

TxConfig = Transmit Configuration Control bit

TxConfigWord = Transmit Configuration Word

This register has two meanings, depending on the state of the ANE bit

(i.e., setting ANE=1 enables the hardware auto-negotiation machine).

Applicable only in SerDes mode; program as 0 for internal-PHY mode.

82573L

7

6

IDE

VLE

5

DEXT

4

reserved

=0

3

2

1

0

RS

IC

IFCS

EOP

EOP = End Of Packet (1=yes, 0=no)

IFCS = Insert Frame CheckSum (1=yes, 0=no) – provided EOP is set

IC = Insert CheckSum (1=yes, 0=no) as indicated by CSO/CSS fields

RS = Report Status (1=yes, 0=no)

DEXT = Descriptor Extension (1=yes, 0=no) use ‘0’ for Legacy-Mode

VLE = VLAN-Packet Enable (1=yes, 0=no) – provided EOP is set

IDE = Interrupt-Delay Enable (1=yes, 0=no)

3

reserved

=0

2

LC

1

EC

0

DD

DD = Descriptor Done

this bit is written back after the NIC processes the descriptor

provided the descriptor’s RS-bit was set (i.e., Report Status)

EC = Excess Collisions

indicates that the packet has experienced more than the

maximum number of excessive collisions (as defined by

the TCTL.CT field) and therefore was not transmitted.

(This bit is meaningful only in HALF-DUPLEX mode.)

LC = Late Collision

indicates that Late Collision has occurred while operating in

HALF-DUPLEX mode. Note that the collision window size

is dependent on the SPEED: 64-bytes for 10/100-MBps, or

512-bytes for 1000-Mbps.

31

?

30

0

29

28

0

27

0

26

0

25

24

23

22

21

20

19

GIO

Master

EN

0 0 0 0 0 0

0

18

17

16

0 0 0

some undocumented functionality?

15

14

13

12

11

0 0 0 0 0

10

PHY

reset

9

8

ASDV

7

6

I

S

L

SPEED

L

O

S

U

5

4

0

TX Function

OFF

ID 0

FD = Full-Duplex

LU = Link Up

TXOFF = Transmission Paused

SPEED (00=10Mbps,01=100Mbps, 10=1000Mbps, 11=reserved)

ASDV = Auto-negotiation Speed Detection Value

3

2

1

0

L

F

0U D

82573L

31

30

29

25

24

23

22

PHY

VME R TFCE RFCE RST R

RST

=0

=0

R

R

R R

=0

=0

=0

15

28

14

R R

=0

=0

27

13

26

12

11

10

R FRC FRC R

=0 DPLX SPD =0

FD = Full-Duplex

GIOMD = GIO Master Disable

SLU = Set Link Up

FRCSPD = Force Speed

FRCDPLX = Force Duplex

9

8

SPEED

21

=0

7

R

=0

6

S

L

U

20

19

ADV

D3

WUC

R

5

18

17

D/UD

status

=0

4

3

=0

R R

=0

=0

2

1

GIO

R

M

0

0

=1 D =0

R R R

=0

16

0

F

D

SPEED (00=10Mbps, 01=100Mbps, 10=1000Mbps, 11=reserved)

ADVD3WUP = Advertise Cold Wake Up Capability

D/UD = Dock/Undock status

RFCE = Rx Flow-Control Enable

RST = Device Reset

TFCE = Tx Flow-Control Enable

PHYRST = Phy Reset

VME = VLAN Mode Enable

82573L

• Total size normally can vary from 64 bytes up

to 1536 bytes (unless ‘jumbo’ packets and/or

‘undersized’ packets are enabled)

• The NIC expects a 14-byte packet ‘header’ and

it appends a 4-byte CRC check-sum

0

destination MAC address

(6-bytes)

6

source MAC address

(6-bytes)

12

Type/length

(2-bytes)

14

the packet’s data ‘payload’ goes here

(usually varies from 56 to 1500 bytes)

Cyclic Redundancy

Checksum (4-bytes)

List of Buffer-Descriptors

descriptor0

descriptor1

descriptor2

descriptor3

0

0

0

0

Buffer0

Buffer1

Buffer2

We setup memory-buffers where we want received

packets to be placed by the NIC

We also create a list of buffer-descriptors and inform

the NIC of its location and size

Then, when ready, we tell the NIC to ‘Go!’ (i.e., start

receiving), but to let us know when these receptions

have occurred

Buffer3

Random Access Memory

31

R

=0

30

29

0

28

27

FLXBUF

0

15

B

A

M

14

R

=0

13

MO

26

25

SE

CRC

BSEX

12

24

23

22

21

R

PMCF

DPF

R

=0

11

10

DTYP

9

8

RDMTS

20

19

18

17

CFI

CFI EN VFE

=0

7

6

I

S

L

OLBML

S

U

5

4

3

16

BSIZE

2

1

0

E

LPE MPE UPE SBP

0 0N

R

=0

EN = Receive Enable

DTYP = Descriptor Type

DPF = Discard Pause Frames

SBP = Store Bad Packets

MO = Multicast Offset

PMCF = Pass MAC Control Frames

UPE = Unicast Promiscuous En BAM = Broadcast Accept Mode BSEX = Buffer Size Extension

MPE = Multicast Promiscuous En BSIZE = Receive Buffer Size

SECRC = Strip Ethernet CRC

LPE = Long Packet reception Ena VFE = VLAN Filter Enable

FLXBUF = Flexible Buffer size

LBM = Loopback Mode

CFIEN = Canonical Form Indicator Enable

RDMTS = Rx-Descriptor Minimum Threshold Size

CFI = Cannonical Form Indic

• Memory-information registers

– RDBA(L/H) = Receive-Descriptor Base-Address Low/High (64bits)

– RDLEN = Receive-Descriptor array Length

– RDH = Receive-Descriptor Head

– RDT = Receive-Descriptor Tail

• Receive-engine control registers

– RXDCTL = Receive-Descriptor Control Register

– RCTL = Receive Control Register

• Notification timing registers

– RDTR = Receive-interrupt packet Delay Timer

– RADV = Receive-interrupt Absolute Delay Value

0x00

RDBA

base-address

0x10

0x20

RDLEN

(in bytes)

RDH (head)

0x30

0x40

0x50

RDT (tail)

0x60

0x70

= owned by hardware (nic)

0x80

= owned by software (cpu)

Circular buffer (128-bytes minimum)

31

30

29

28

27

26

25

R

R

R

R

R

R

R

=0

=0

=0

=0

=0

=0

=0

24

G

R

A

N

23

22

21

R

R

=0

=0

1

--------0

20

FRC HTHRESH

FRC

0

DPLX

(HostSPD

Threshold)

17

16

0

R R

=0

18

SDP1 SDP0

ADV WTHRESH

DATA DATA

D3 --------- --------(Writeback

Threshold)

WUC

D/UD

0

status

GRAN (Granularity): 1=descriptor-size, 0=cacheline-size

15 14

13

12

11

10

9

8

7

6

R R 0

=0 =0

19

=0

5

4

3

2

1

0

A

L

PTHRESH

S

R

0

0 0

D (Prefetch

S Threshold)

E

T

Prefetch Threshold – A prefetch operation is considered when the number of valid, but

unprocessed, receive descriptors that the ethernet controller has in its on-chip buffer drops below

this threshold.

Host Threshold - A prefetch occurs if at least this many valid descriptors are available in host

memory

Writeback Threshold - This field controls the writing back to host memory of already processed

receive descriptors in the ethernet controller’s on-chip buffer which are ready to be written back to

host memory

7

6

PIF

5

4

IPCS TCPCS UDPCS

3

2

VP

IXSM

1

EOP

0

DD

DD = Descriptor Done (1=yes, 0=no) shows if nic is finished with descriptor

EOP = End Of Packet (1=yes, 0=no) shows if this packet is logically last

IXSM = Ignore Checksum Indications (1=yes, 0=no)

VP = VLAN Packet match (1=yes, 0=no)

USPCS = UDP Checksum calculated in packet (1=yes, 0=no)

TCPCS = TCP Checksum calculated in packet (1=yes, 0=no)

IPCS = IPv4 Checksum calculated on packet (1=yes, 0=no)

PIF = Passed In-exact Filter (1=yes, 0=no) shows if software must check

7

RXE

6

5

IPE

TCPE

4

3

reserved reserved

=0

=0

2

SEQ

1

SE

0

CE

RXE = Received-data Error (1=yes, 0=no)

IPE = IPv4-checksum error

TCPE = TCP/UDP checksum error (1=yes, 0=no)

SEQ = Sequence error (1=yes, 0=no)

SE = Symbol Error (1=yes, 0=no)

CE = CRC Error or alignment error (1=yes, 0=no)

• The 82573L has several dozen statistical

counters which automatically operate to keep

track of significant events affecting the

ethernet controller’s performance

• Most are 32-bit ‘read-only’ registers, and they

are automatically cleared when read

• Your module’s initialization routine could read

them all (to start counting from zero)

• The statistical counters all have addressoffsets in the range 0x04000 – 0x04FFF

• You can use a very simple program-loop to

‘clear’ each of these read-only registers

// Here ‘io’ is the virtual base-address

// of the nic’s i/o-memory region

{

int

r;

// clear all of the Pro/1000 controller’s statistical counters

for (r = 0x4000; r < 0x4FFF; r += 4) ioread32( io + r );

}

0x4000 CRCERRS

0x400C RXERRC

0x4014SCC

0x4018ECOL

0x4074GPRC

0x4078BPRC

0x407CMPRC

0x40D0

0x40D4

0x40F0MPTC

0x40F4BPTC

CRC Errors Count

Receive Error Count

Single Collision Count

Excessive Collision Count

Good Packets Received

Broadcast Packets Received

Multicast Packets Received

TPR

Total Packets Received

TPT

Total Packets Transmitted

Multicast Packets Transmitted

Broadcast Packets Transmitted

my_isr()

my_fops

ioctl

my_ioctl()

open

my_open()

read

my_read()

write

my_write()

release

my_release()

module_init()

module_exit()

• Network interface driver similar to mounted

block devices

• A Special block devices registers its disk and

methods with kernel and Transmit and

Receive block on request

• Socket Read/Write system call

• Network driver receive Asyn packet from

Outside world

• Ask to push incoming packet towards kernel

• Many administrative works

– Setting up address, modify transmission param,

maintaining traffic, error statistics

• Network subsystem completely protocol

independent

– Software (IP) and Hardware (Eth, Ring)

• Linux loop back driver

• At drivers/net/loopback.c

• It simulates conversations with real remote

hosts in order to demonstrate the task of

writing network drivers

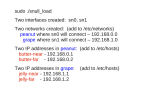

• Suppose two interfaces in system sn0, sn1 interfaces

• Loopback: it really don’t send/simulate

• But to send actually: toggle LSBit of third octet of both

src & dest address

– It changes both the network number and host number of

class C IP number

– The net effect is packet sent to network interface sn0

appears on sn1

• Snullnet0: network connected to sn0 interface,

Snullnet1:network connected to sn1 interface

– Must have 24 bit masks

• local0, local1: IP address assigned: must differs in the

Lsbit of their in 3rd and 4th octet

• Snull interface correspond to Ethernet class

• It emulates Ethernet

• Kernel offers some generalized support of

Ethernet devices

• Ethernet is strong: plip (interface used for

printer): declares itself as Ethernet device

• Watch packets: tcpump

• Snull works only wit IP Packets

– Modify src,dst,chksu in the IP headers: without

checking wheather it actually conve IP infos

• Loopback.c, plip.c, e100.c are examples of

network drivers : /drivers/net/

• Device registration:

– Alloc net devices (Request for resources and offer

facilities)

• Struct net_devices *snull_dev[2] ; //linux/netdevice.h

• snull_dev[0]=alloc_netdev(sizeof(struct snull_priv),

“sn%d”,snull_init);

• Alloac_etherdev(int sizeof_priv); /wrapper to

alloc_netdev

– After initialization complete register the devices

• register_netdev(snull_dev[i]); // return 1 if fails

• Snull uses alloc_netdev, it have a separate

initialization function

• Ether_setup(dev);//it assign some field

– dev->open=snull_open;

– dev->close=snull_release;

– set_config, hard_start_txmit, do_ioctl, get_stats,

rebuild_header, tx_timeout, watchdog_timeo,

– flag|=IFFNOARP;

– Features|=NETIF_F_NO_CSUM

– hard_header_cache=NULL//disable caching

• Private data pointers: priv with al netdevices

• Strcut snull_priv *priv=nedev_priv(dev);

Strcu snull_priv {

struct net_devices_stats stats;

int status;

strcut snull_packet *ppool;

struct snul_packet *rx_queue;

int rx_enabled, tc_packele;

u8 *tx_packetdata;

struct sk_bff *skb;

spinlock_t lock;

};

• Initialization

priv=netdriv_priv(dev);

memset(priv,0,sizeof(strcutn null_priv));

spin_lock_init(&priv->lock);

snull_rx_inits(dev,1); //enable revice interrupts

• Cleanup (snull_dev[i]){

unregister_netdev(snull_dev[i]);

snull_teardown_pool(snull_dev[i]);

free_netdev(snull_dev[i]);

}

• Tearown_pool: flush packet pool and bufffer

of private data

• Global Information

– name: name of device

– State: state of device

– net_device *next; // ptr to next dev in global list

– init_funtion: An init fun called by reg_netdev();

• Hardware Information

• Interface Information

• Device methods

• Low level hardware information

• Base_address: io_base address of network interface

• Char irq: dev->irq, the assigned interrupt

number..ifconfig

• Char if_port: the port is in use on multiport

device..10base

• Char dma; // dma allcoated by the device for ISA bus

• Device memory information: address of shared

memory used by the devices

– Rmem (rx mem) , mem (tx_mem)

– rmem_start, rmem_end, mem-start, mem_end;

• Init setup most of the information But device

specific setup information need to setup later on

• Non ethernet interface can use helper functions

– fc_setup, ltalk_setup, fddi_setup

– Fiber channel, local talk, fiber dis data ineterface, token

ring, hihh perf parllel interface (hppi_setup)

• Non default interface filed

– Hard_headerlen,MTU (max tx unit=1500 oct ),

tx_queue_len (ether=1000, pipl=10), short type, char

adresslen; char dev_addeess[Max_add_len],

breadcast[max_ad_len]

• Flags bt sets: Mask bits, loopback, debug, noarp,

multicast

• Special hardware capability the device has: DMA

• Fundamental method

– Open, Stop, Hard_start_xmit

– Hard_header, Rebuild_header

– Tx_timeout, Net_device_stats, Set_config

• Optional methods

– Poll, poll_controller, do_ioctl, set_multicastlist

– Set_mac_address,change_mtu, header_cache,

header_cache_update, hard_header_parse

• Utilities fileds (not methods)

– Trans_start, last_rx, watchdog_timeo, *priv,

mc_list, mc_count, xmit_lock, xmit_lock_owner

int snull_open(struct net_device *dev) {

/* request_region( ), request_irq( ), Assign the hardware address of the

board: use "\0SNULx", where

* x is 0 or 1. The first byte is '\0' to avoid being a multicast

* address (the first byte of multicast addrs is odd). */

memcpy(dev->dev_addr, "\0SNUL0", ETH_ALEN);

if (dev = = snull_devs[1])

dev->dev_addr[ETH_ALEN-1]++; /* \0SNUL1 */

netif_start_queue(dev);

return 0;

}

int snull_release(struct net_device *dev) {

/* release ports, irq and such -- like fops->close */

netif_stop_queue(dev); /* can't transmit any more */

return 0;

}

int snull_tx(struct sk_buff *skb, struct net_device *dev){

int len; char *data, shortpkt[ETH_ZLEN];

struct snull_priv *priv = netdev_priv(dev);

data = skb->data; len = skb->len;

if (len < ETH_ZLEN) {

memset(shortpkt, 0, ETH_ZLEN);

memcpy(shortpkt, skb->data, skb->len);

len = ETH_ZLEN;

data = shortpkt;

}

dev->trans_start = jiffies; /* save the timestamp */

/* Remember the skb, so we can free it at interrupt time */

priv->skb = skb;

/* actual deliver of data is device-specific, and not shown here */

snull_hw_tx(data, len, dev); return 0;

}

void snull_rx(struct net_device *dev, struct snull_packet *pkt) {

struct sk_buff *skb; struct snull_priv *priv = netdev_priv(dev);

/* * The packet has been retrieved from the transmission * medium. Build an skb around it, so

upper layers can handle it */

skb = dev_alloc_skb(pkt->datalen + 2);

if (!skb) {

if (printk_ratelimit( ))

printk(KERN_NOTICE "snull rx: low on mem - packet dropped\n");

priv->stats.rx_dropped++;

goto out;

}

memcpy(skb_put(skb, pkt->datalen), pkt->data, pkt->datalen);

/* Write metadata, and then pass to the receive level */

skb->dev = dev;

skb- >protocol = eth_type_trans(skb, dev);

skb->ip_summed = CHECKSUM_UNNECESSARY; /* don't check it */

priv->stats.rx_packets++;

priv->stats.rx_bytes += pkt->datalen;

netif_rx(skb);

out: return; }