* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download poster_rani_indicon2014

Buck converter wikipedia , lookup

Signal-flow graph wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Electrical ballast wikipedia , lookup

Stray voltage wikipedia , lookup

Alternating current wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Current source wikipedia , lookup

Flexible electronics wikipedia , lookup

Negative feedback wikipedia , lookup

Surge protector wikipedia , lookup

Mains electricity wikipedia , lookup

Regenerative circuit wikipedia , lookup

Videocassette recorder wikipedia , lookup

Potentiometer wikipedia , lookup

Integrated circuit wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Two-port network wikipedia , lookup

Opto-isolator wikipedia , lookup

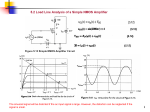

IEEE Indicon 2014, 11-13 Dec, 2014, Pune, India, Paper No. 1098 (Poster session: Thursday, 13th Dec, 0900-1300) A JFET-based Circuit for Realizing a Precision and Linear Floating Voltage-controlled Resistance Rani Holani, P. C. Pandey, and Nitya Tiwari Indian Institute of Technology Bombay Abstract—A JFET-based circuit for realizing a precision and Circuit description linear floating voltage-controlled resistance (VCR) is presented for use in analog multipliers and programmable analog circuits and as a resistance mirror. It uses a matched JFET pair along with an op amp based negative feedback for realizing a precision resistance and a feedback of the source and drain voltages to the gate for realizing a linear floating resistance. The circuit operation is validated through circuit simulation and practical testing. Operation Background Voltage controlled-resistance (VCR) applications ◦ Modulators & demodulators ◦ Programmable analog circuits ◦ Analog multipliers ◦ Volume controllers • Matched transistors Q1, Q2 in triode region • Q1 channel resistance stabilized against parameter variations using negative feedback (op amp A1) • Linearity extended by source-drain bootstrapped gates • Q2: Floating resistor with terminals X and Y Equations JFET (or MOSFET) based grounded VCR + RDS = vDS/iD = 1/[k(vGS − vP − vDS /2] vDS << vGS −VP D vDS + G vGS • Linear only for tens of mV of vDS • Imprecision due to temperaturedependent & piece-to-piece variations • Not useable as floating VCR. S − − i1 = − v1/R1 ▪ vG1 = (vC + v2)/2 ▪ vG2 = (vC + vX + vY)/2 iX = (vX − vY)/[v2/(− v1/R1)], 0 ≥ vC ≥ 2VC & │vX − vY │≤ min(−vC , vC − VP) RXY = [v2/(− v1)] R1 Features • Voltage controlled: by v1 or v2 • Current controlled: by current source i1 in place of v1 and R1 • Floating VCR: neither X nor Y needs to be grounded • Resistance mirror: vC applied for controlling multiple X-Y terminal pairs Simulation results JFET-based floating VCR (Senani, 1994) iX R4 R5 + − M1 R3 A1 + vC + − X vXY vG − iY R1 R2 Y Source-drain bootstrapped gate: vD & vS superimposed on the control voltage • Floating VCR with an extended range of linearity • Imprecision due to temperaturedependent & pieceto-piece variations Precision grounded VCR (Clarke, 1977) vREF iX + − D S R1 vC + − i1 M1 + v G M2 − G − A1 + iY X vXY Y Self tracking ckt using matched JFET pair & op amp based negative feedback to compensate for variations in the device parameters • Not useable as a floating VCR • Useable only for small terminal voltages Simulation using LTspice IV for examining the effect of variation in device parameters (JFET pair U441, op amp LT1366 with ±15 V, v2 = 1.0 V, R1 = 1000 Ω, vY = 0, variable vX) A) Operation of A1-Q1 selftracking: Effect of variation in VP and IDSS on vC, with v1 as input B) Operation of full ckt: Effect of variation in vXY, VP and IDSS on RXY • Single device: large change with vXY & device parameter variations • Proposed ckt: < 5% change with vXY, variation, no dependence on device parameters Experimental results Ckt components: JFET pair U441, op amp LT1366 with ±15 V, R2 = R3 = 1 MΩ, R4 = R5 = R6 = R7 = 12 kΩ, R8 = 6 kΩ (12 kΩ ║ 12 kΩ). • Test condition: v1 = −1 V, v2 = 1 V, R1 = 1 kΩ, observed vC = −3.68 V, variable vX, vY = 0. Result: RXY = 1033 Ω with −2.7% to 2.0% change for vXY of ± 1 V. • Test condition: v1 = −0.5 V, v2 = 1 V, R1 = 1 kΩ, observed vC = −4.85 V, variable vX, vY = 0. Proposed circuit A JFET-based circuit for precision & linear floating VCR & resistance mirror, using the features of selftracking & source-drain bootstrapped gate circuits. Result: RXY = 2039 Ω with −4.2% to 2.2% change for vXY of ± 1 V. Conclusion Precision & linear operation of the proposed floating VCR circuit validated using simulation and practical testing. Applications: voltage or current-controlled time-varying resistance, a resistance mirror for controlling resistances across a set of ports.