* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Combination Locks

Survey

Document related concepts

Electrical substation wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Fault tolerance wikipedia , lookup

Flexible electronics wikipedia , lookup

Light switch wikipedia , lookup

Power electronics wikipedia , lookup

Regenerative circuit wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Buck converter wikipedia , lookup

Integrating ADC wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Two-port network wikipedia , lookup

Crossbar switch wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Schmitt trigger wikipedia , lookup

Transcript

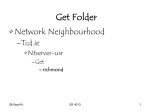

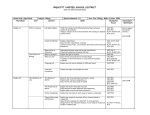

13 Combination Locks This circuit uses 4013 D-type bistable flip-flops (D stands for data). Each flipflop has a data input and a clock input. The voltage applied to the input is transferred to the Q output at the instant when the clock input goes from 0 to 1. (We say these flip-flops are “edge-triggered”.) Switches 1, 2, 3 and 4 are the switches which form the code and any number of “wrong” switches can be connected, in parallel, at the point shown. Note that there is also a second output which is always the complement of the Q output; that is, if Q is 1 the other output is at 0; if Q = 0 its complement is 1 (these outputs are not used in this circuit). + “wrong” switches 1 220n rst D rst Q D cl 10M 4 rst Q Q 1µ 3 2 D rst Q Q D Q Q cl cl Q 10k cl 100k - 1 Improved version One disadvantage of the first circuit is that if a “right” button is pushed at the wrong time, it simply does nothing. In the circuit shown below if one of the “right” buttons is pushed at the wrong time, the whole circuit is reset (again, with a delay, if you include the 1µ capacitor). The flip-flops are 4013 and the AND gates are a 4081. + 1 2 rst D 3 rst Q D 4 rst D Q rst Q D Q 10k 10M 4013 Q 4013 Q 4013 Q 4013 Q cl cl cl cl 1µ - N.B.In both these circuits it is a good idea to connect the switches to the board using screw connectors rather than soldering them as this makes it easier to change the combination. © David hoult 2001 2