* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Week-7

Josephson voltage standard wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Power electronics wikipedia , lookup

Power MOSFET wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Schmitt trigger wikipedia , lookup

Operational amplifier wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Wilson current mirror wikipedia , lookup

Charlieplexing wikipedia , lookup

Surge protector wikipedia , lookup

Electrical ballast wikipedia , lookup

Rectiverter wikipedia , lookup

Topology (electrical circuits) wikipedia , lookup

RLC circuit wikipedia , lookup

Opto-isolator wikipedia , lookup

Current source wikipedia , lookup

Two-port network wikipedia , lookup

Principles of Computer Engineering:

Lecture 3: Kirchhoff’s Laws

Kirchhoff’s Voltage Law (KVL)

“The algebraic sum of all voltages around any closed path

in a circuit is zero” (positive for a voltage rise, negative for

a voltage drop.

+

v3

–

–

v2

+

+

v1 v2 v3 0

v1

v1 v2 v3 0

–

v1 v2 v3

Correct your lab manual p32

Kirchhoff’s Current Law (KCL)

“The algebraic sum of all currents at any node (junction) in

a circuit is zero” (positive for a current leaving a node,

negative for coming a node) or restate as

“ The sum of currents flowing into a junction is equal to

the sum of currents flowing out a junction

i1

i2

i1 i2 i3 0

i1 i2 i3 0

i3

i1 i2 i3

Sum the current at each node

Node a:

i1 + i 4 - i2 - i5 = 0

Node b:

i2 + i3 – i1 - ib - ia= 0

Node c:

ib – i3 – i4 - ic = 0

Node d:

i5 + ia + ic = 0

Note: no connection dot ●

in the centre of the

diagram

Sum the voltage around each designated

path in the circuit

Path a

-v1 + v2 + v4 – vb – v3 = 0

Path b

-va + v3 + v5 = 0

Path c

vb – v4 – vc – v6 – v5 = 0

Path d

-va – v1 + v2 - vc + v7 – vd = 0

Resistors

Components which resist or reduce the flow of current in a circuit are called

resistances, the unit of resistance is the ohm (Ω). They are used in circuits

to control or limit the amount of current flow in a wire ,and to be a current-to

voltage convertor.

Resistors in series: R total =R1+R2+R3+R4

Resistors in parallel:

1/Rtotal = 1/R1 +1/R2 +1/R3 +1/R4

The total resistor of a parallel resistor network is always

dominated by, and is less than, the smallest resistor.

All components connected in series have the same current flowing through them.

Is = Ir = Id = Ii = Ispk = Iu = If

All components connected in parallel have the same

voltage across them

Circuit Analysis: Example 1

Combining series and parallel resistors accordingly to simplify

circuits and determine equivalent resistances

Circuit Analysis: Example 2

Circuit Analysis: Example 3

Summary

Introduced Kirchoff’s Laws

Resistor network simplification

Simple circuit analysis

Principles of Computer Engineering:

Labs Experiment 3: Kirchoff’s Laws

Overview

Build a simple resistor network and measure the voltages at

each node

Use results to verify Kirchoff’s Voltage Law

Calculate the currents through each node and compare to

Kirchoff’s Current Law

Resistors Colour Codes

Resistor Colour Codes

Identify the following resistors based on their colour codes

{1kΩ, 2.2kΩ, 3.9kΩ, 4.7kΩ & 5.6kΩ}

Measure them and calculate actual error %

Populate table with expected colour for each value

Resistor

Value

Colour

Band 1

Colour

Band 2

Colour

Band 3

Tolerance

%

1000Ω

Brown

Black

Red

5

2200Ω

Red

Red

Red

5

3900Ω

Orange

White

Red

5

4700Ω

Yellow

Violet

Red

5

5600Ω

Green

Blue

Red

5

Measured

Value

Error

%

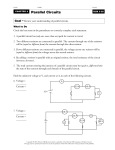

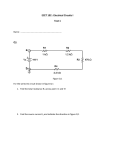

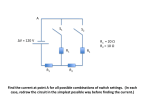

Test Resistor Network (KVL)

Build the circuit below

Use N0 as your reference node (0V)

Test the voltages at each node using DVM

Component

Voltage[V]±1%

V1

VR1

VR2

VR3

VR4

VR5

Check each of three loops that KVL is preserved

Loop 1 =>

– V1 + VR1 + VR2 = 0 or equivalently V1 = VR1 + VR2

Loop 2 =>

– VR2 + VR3 + VR4 = 0 or equivalently VR2 = VR3 + VR4

Loop 3 =>

– VR4 + VR5 = 0

or equivalently VR4 = VR5

Test Resistor Network (KCL)

Calculate the currents passing in each loop from voltages

measured previously.

DO NOT MEASURE CURRENTS DIRECTLY

Verify KCL at each node within error margins

Verify KCL at the two nodes (N2 and N3)

Current #

Current [A]

±__%

I1

I2

I3

I4

I5

Node 2 =>

– I1 + I2 + I3 = 0

or equivalently

I1 = I2 + I3

Node 3 =>

– I3 + I4 + I5 = 0

or equivalently

I3 = I4 + I5

Summary

Build resistor network and test

Measure voltages at each node

Calculate currents passing through each node

Verify both KVL and KCL

Consider sources of errors in this experiment

Put all your results and notes into your logbook!

Any questions?