* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download ICM7216B,D

Variable-frequency drive wikipedia , lookup

Utility frequency wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Scattering parameters wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Control system wikipedia , lookup

Linear time-invariant theory wikipedia , lookup

Buck converter wikipedia , lookup

Oscilloscope wikipedia , lookup

Integrating ADC wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Oscilloscope history wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Schmitt trigger wikipedia , lookup

Phase-locked loop wikipedia , lookup

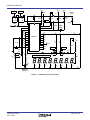

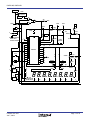

ICM7216B, ICM7216D OBSOLETE PRODUCT NO RECOMMENDED REPLACEMENT contact our Technical Support Center at www.intersil.com/tsc DATASHEET FN3166 Rev.4.00 Jan 7, 2004 8-Digit, Multi-Function, Frequency Counters/Timers The ICM7216B is a fully integrated Timer Counters with LED display drivers. They combine a high frequency oscillator, a decade timebase counter, an 8-decade data counter and latches, a 7-segment decoder, digit multiplexers and 8segment and 8-digit drivers which directly drive large multiplexed LED displays. The counter inputs have a maximum frequency of 10MHz in frequency and unit counter modes and 2MHz in the other modes. Both inputs are digital inputs. In many applications, amplification and level shifting will be required to obtain proper digital signals for these inputs. Features, All Versions The ICM7216B can function as a frequency counter, period counter, frequency ratio (fA /fB) counter, time interval counter or as a totalizing counter. The counter uses either a 10MHz or 1MHz quartz crystal timebase. For period and time interval, the 10MHz timebase gives a 0.1s resolution. In period average and time interval average, the resolution can be in the nanosecond range. In the frequency mode, the user can select accumulation times of 0.01s, 0.1s, 1s and 10s. With a 10s accumulation time, the frequency can be displayed to a resolution of 0.1Hz in the least significant digit. There is 0.2s between measurements in all ranges. • Internally generated decimal points, interdigit blanking, leading zero blanking and overflow indication The ICM7216D functions as a frequency counter only, as described above. All versions of the ICM7216 incorporate leading zero blanking. Frequency is displayed in kHz. In the ICM7216B, time is displayed in s. The display is multiplexed at 500Hz with a 12.2% duty cycle for each digit. The ICM7216B and ICM7216D are designed for common cathode displays with typical peak segment currents of 12mA. In the display off mode, both digit and segment drivers are turned off, enabling the display to be used for other functions. • Functions as a frequency counter (DC to 10MHz) • Four internal gate times: 0.01s, 0.1s, 1s, 10s in frequency counter mode • Directly drives digits and segments of large multiplexed LED displays (common anode and common cathode versions) • Single nominal 5V supply required • Highly stable oscillator, uses 1MHz or 10MHz crystal • Display off mode turns off display and puts chip into low power mode • Hold and reset inputs for additional flexibility Features, ICM7216B • Functions also as a period counter, unit counter, frequency ratio counter or time interval counter • 1 cycle, 10 cycles, 100 cycles, 1000 cycles in period, frequency ratio and time interval modes • Measures period from 0.5s to 10s Features, ICM7216D • Decimal point and leading zero banking may be externally selected Part Number Information PART NUMBER TEMP. RANGE (oC) PACKAGE PKG. NO. ICM7216BlPl -25 to 85 28 Ld PDIP E28.6 ICM7216DlPl -25 to 85 28 Ld PDIP E28.6 FN3166 Rev.4.00 Jan 7, 2004 Page 1 of 18 ICM7216B, ICM7216D Pinouts ICM7216B (PDIP) COMMON CATHODE TOP VIEW 28 INPUT A CONTROL INPUT 1 INPUT B 2 27 HOLD INPUT FUNCTION INPUT 3 26 OSC OUTPUT DIGIT 1 OUTPUT 4 25 OSC INPUT DIGIT 3 OUTPUT 5 24 EXT OSC INPUT DIGIT 2 OUTPUT 6 23 DECIMAL POINT OUTPUT DIGIT 4 OUTPUT 7 22 SEG g OUTPUT VSS 8 21 SEG e OUTPUT DIGIT 5 OUTPUT 9 20 SEG a OUTPUT DIGIT 6 OUTPUT 10 19 SEG d OUTPUT DIGIT 7 OUTPUT 11 18 VDD DIGIT 8 OUTPUT 12 17 SEG b OUTPUT RESET INPUT 13 16 SEG c OUTPUT RANGE INPUT 14 15 SEG f OUTPUT ICM7216D (PDIP) COMMON CATHODE TOP VIEW CONTROL INPUT 1 MEASUREMENT IN PROGRESS 2 FN3166 Rev.4.00 Jan 7, 2004 28 INPUT A 27 HOLD INPUT DIGIT 1 OUTPUT 3 26 OSC OUTPUT DIGIT 3 OUTPUT 4 25 OSC INPUT DIGIT 2 OUTPUT 5 24 EXT OSC INPUT DIGIT 4 OUTPUT 6 23 DECIMAL POINT OUTPUT VSS 7 22 SEG g OUTPUT DIGIT 5 OUTPUT 8 21 SEG e OUTPUT DIGIT 6 OUTPUT 9 20 SEG a OUTPUT DIGIT 7 OUTPUT 10 19 SEG d OUTPUT DIGIT 8 OUTPUT 11 18 VDD RESET INPUT 12 17 SEG b OUTPUT EX. DECIMAL POINT INPUT 13 16 SEG c OUTPUT RANGE INPUT 14 15 SEG f OUTPUT Page 2 of 18 ICM7216B, ICM7216D Functional Block Diagram EXT OSC INPUT OSC INPUT 3 OSC SELECT 8 DIGIT DRIVERS DECODER OSC OUTPUT 8 DIGIT OUTPUTS (8) REFERENCE COUNTER 103 RANGE CONTROL LOGIC RANGE SELECT LOGIC 104 OR 105 RANGE INPUT 100Hz 5 STORE AND RESET LOGIC RESET INPUT 6 CONTROL LOGIC CONTROL INPUT MAIN 103 COUNTER EN CL INPUT A INPUT B (NOTE 1) 4 INPUT CONTROL LOGIC DP LOGIC OVERFLOW 4 4 4 4 4 4 4 DATA LATCHES AND STORE OUTPUT MUX 4 D INPUT CONTROL LOGIC DECODER LOGIC 7 SEGMENT DRIVER 8 SEGMENT OUTPUTS (8) Q FUNCTION INPUT (NOTE 1) EXT DP INPUT (NOTE 2) CL MAIN FF MEASUREMENT IN PROGRESS OUTPUT (NOTE 2) FN CONTROL LOGIC 6 HOLD INPUT NOTES: 1. Function input and input B available on ICM7216B only. 2. Ext DP input and MEASUREMENT IN PROGRESS output available on ICM7216D only. FN3166 Rev.4.00 Jan 7, 2004 Page 3 of 18 ICM7216B, ICM7216D Absolute Maximum Ratings Thermal Information Maximum Supply Voltage (VDD - VSS) . . . . . . . . . . . . . . . . . . 6.5V Maximum Digit Output Current . . . . . . . . . . . . . . . . . . . . . . . 400mA Maximum Segment Output Current. . . . . . . . . . . . . . . . . . . . . 60mA Voltage On Any Input or Output Terminal (Note 3). . . . . . . . . . . (VDD +0.3V) to (VSS -0.3V) Thermal Resistance (Typical, Note 4) Operating Conditions JA (oC/W) PDIP Package . . . . . . . . . . . . . . . . . . . Maximum Junction Temperature JC (oC/W) 55 N/A PDIP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150oC o Maximum Storage Temperature Range . . . . . . . . . . -65 C to 150oC Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300oC Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . -25oC to 85oC CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. NOTES: 3. The ICM7216 may be triggered into a destructive latchup mode if either input signals are applied before the power supply is applied or if input or outputs are forced to voltages exceeding VDD to VSS by more than 0.3V. 4. JA is measured with the component mounted on an evaluation PC board in free air. Electrical Specifications VDD = 5.0V, VSS = 0V, TA = 25oC, Unless Otherwise Specified PARAMETER TEST CONDITIONS MIN TYP MAX UNITS - 2 5 mA ICM7216B Operating Supply Current, IDD Display Off, Unused Inputs to VSS Supply Voltage Range (VDD -VSS), VSUPPLY INPUT A, INPUT B Frequency at fMAX 4.75 - 6.0 V Maximum Frequency INPUT A, Pin 28, fA(MAX) Figure 6, Function = Frequency, Ratio, Unit Counter 10 - - MHz Function = Period, Time Interval 2.5 - - MHz Maximum Frequency INPUT B, Pin 2, fB(MAX) Figure 7 2.5 - - MHz Minimum Separation INPUT A to INPUT B Time Interval Function Figure 1 250 - - ns 10 - - MHz - - 100 kHz 2000 - - S Maximum Oscillator Frequency and External Oscillator Frequency, fOSC Minimum External Oscillator Frequency, fOSC Oscillator Transconductance, gM VDD = 4.75V, TA = 85°C Multiplex Frequency, fMUX fOSC = 10MHz - 500 - Hz Time Between Measurements fOSC = 10MHz - 200 - ms Input Low Voltage, VINL - - 1.0 V Input High Voltage, VlNH 3.5 - - V 100 400 - k - - 20 A - 15 - mV/s Input Voltages: Pins 2, 13, 25, 27, 28 Input Resistance to VDD Pins 13, 24, RIN VIN = VDD -1.0V Input Leakage Pins 27, 28, 2, IILK Input Range of Change, dVlN /dt Supplies Well Bypassed Digit Driver: Pins 4, 5, 6, 7, 9, 10, 11, 12 Low Output Current, IOL VOUT = VSS +1.3V 50 75 - mA High Output Current, IOH VOUT = VDD -2.5V - -100 - A High Output Current, IOH VOUT = VDD -2.0V -10 - - mA Leakage Current, ISLK VOUT = VDD -2.5V - - 10 A Segment Driver: Pins 15, 16, 17, 19, 20, 21, 22, 23 Multiplex Inputs: Pins 1, 3, 14 FN3166 Rev.4.00 Jan 7, 2004 Page 4 of 18 ICM7216B, ICM7216D Electrical Specifications VDD = 5.0V, VSS = 0V, TA = 25oC, Unless Otherwise Specified (Continued) PARAMETER MIN TYP MAX UNITS Input Low Voltage, VINL - - VDD 2.0 V Input High Voltage, VlNH VDD 0.8 - - V 100 360 - k - 2 5 mA 4.75 - 6.0 V 10 - - MHz 10 - - MHz Input Resistance to VDD, RIN TEST CONDITIONS VlN = VDD -2.5V ICM7216D Operating Supply Current, IDD Display Off, Unused Inputs to VSS Supply Voltage Range (VDD -VSS), VSUPPLY INPUT A Frequency at fMAX Maximum Frequency INPUT A, Pin 28, fA(MAX) Figure 6 Maximum Oscillator Frequency and External Oscillator Frequency, fOSC - - 100 kHz 2000 - - S fOSC = 10MHz - 500 - Hz fOSC = 10MHz - 200 - ms Minimum External Oscillator Frequency, fOSC Oscillator Transconductance, gM VDD = 4.75V, TA = 85°C Multiplex Frequency, fMUX Time Between Measurements Input Voltages: Pins 12, 27, 28 Input Low Voltage, VINL - - 1.0 V Input High Voltage, VINH 3.5 - - V 100 400 - k - - 20 A - - mA Input Resistance to VDD, Pins 12, 24, RIN VIN = VDD -1.0V Input Leakage, Pins 27, 28, IILK Output Current, Pin 2, IOL VOL = +0.4V 0.36 Output Current, Pin 2, IOH VOH = VDD -0.8V 265 - - A Input Rate of Change, dVlN /dt Supplies Well Bypassed - 15 - mV/s 50 75 - mA - A Digit Driver: Pins 3, 4, 5, 6, 8, 9, 10, 11 Low Output Current, IOL VOUT = +1.3V High Output Current, IOH VOUT = VDD -2.5V - 100 High Output Current, IOH VOUT = VDD -2.0V 10 15 Leakage Current, ISLK VOUT = VDD -2.5V - - 10 A Input Low Voltage, VlNL - - VDD 2.0 V Input High Voltage, VINH VDD 0.8 - - V 100 360 - k Segment Driver: Pins 15, 16, 17, 19, 20, 21, 22, 23 mA Multiplex Inputs: Pins 1, 13, 14 Input Resistance to VDD, RlN FN3166 Rev.4.00 Jan 7, 2004 VIN = VDD -1.0V Page 5 of 18 ICM7216B, ICM7216D Timing Diagram 40ms INTERNAL STORE 30ms TO 40ms 60ms FUNCTION: TIME INTERVAL INTERNAL RESET 40ms UPDATE 190ms TO 200ms UPDATE PRIMING MEASUREMENT INTERVAL MEASUREMENT IN PROGRESS (INTERNAL ON 7216B) INPUT A PRIMING EDGES INPUT B 250ns MIN MEASURED INTERVAL (FIRST) MEASURED INTERVAL (LAST) NOTE: 5. If range is set to 1 event, first and last measured interval will coincide. FIGURE 1. WAVEFORMS FOR TIME INTERVAL MEASUREMENT (OTHERS ARE SIMILAR, BUT WITHOUT PRIMING PHASE) Typical Performance Curves 30 20 4.5 VDD 6V fA (MAX) FREQUENCY UNIT COUNTER, FREQUENCY RATIO MODES -20oC 25oC ISEG (mA) FREQUENCY (MHz) 15 10 fA (MAX) fB (MAX) PERIOD, TIME INTERVAL MODES 20 85oC 10 5 TA = 25oC 0 3 0 4 5 6 VDD-VSS (V) FIGURE 2. fA(MAX), fB(MAX) AS A FUNCTION OF SUPPLY FN3166 Rev.4.00 Jan 7, 2004 0 1 2 VDD-VOUT (V) FIGURE 3. TYPICAL ISEG vs VDD-VOUT Page 6 of 18 3 ICM7216B, ICM7216D Typical Performance Curves (Continued) 200 200 TA = 25oC -20oC VDD = 5V VDD = 5.5V 25oC 50 IDIGIT (mA) IDIGIT (mA) 150 85oC 100 VDD = 4.5V 100 50 50 0 VDD = 5V 0 0 1 2 3 0 1 VOUT (V) FIGURE 4. TYPICAL IDIGIT vs VOUT Description 2 3 VOUT (V) FIGURE 5. TYPICAL IDIGIT vs VOUT . TABLE 1. MULTIPLEXED INPUT FUNCTIONS INPUTS A and B FUNCTION INPUTS A and B are digital inputs with a typical switching threshold of 2V at VDD = 5V. For optimum performance the peak-to-peak input signal should be at least 50% of the supply voltage and centered about the switching voltage. When these inputs are being driven from TTL logic, it is desirable to use a pullup resistor. The circuit counts high to low transitions at both inputs. (INPUT B is available only on lCM7216B). FUNCTION INPUT (Pin 3, lCM7216B Only) Note that the amplitude of the input should not exceed the device supply (above the VDD and below the VSS) by more than 0.3V, otherwise the device may be damaged. RANGE INPUT, Pin 14 Frequency D1 Period D8 Frequency Ratio D2 Time Interval D5 Unit Counter D4 Oscillator Frequency D3 0.01s/1 Cycle D1 0.1s/10 Cycles D2 1s/100 Cycles D3 10s/1K Cycles Multiplexed Inputs The FUNCTION, RANGE, CONTROL and EXTERNAL DECIMAL POINT inputs are time multiplexed to select the function desired. This is achieved by connecting the appropriate Digit driver output to the inputs. The function, range and control inputs must be stable during the last half of each digit output, (typically 125s). The multiplexed inputs are active low for the common cathode lCM7216B and lCM7216D. CONTROL INPUT, Pin 1 Noise on the multiplex inputs can cause improper operation. This is particularly true when the unit counter mode of operation is selected, since changes in voltage on the digit drivers can be capacitively coupled through the LED diodes to the multiplex inputs. For maximum noise immunity, a 10k resistor should be placed in series with the multiplexed inputs as shown in the application circuits. External DP INPUT (Pin 13, ICM7216D Only) DIGIT D4 Display Off D4 and Hold Display Test D8 1MHz Select D2 External Oscillator Enable D1 External Decimal Point Enable D3 Decimal point is output for same digit that is connected to this input. Table 1 shows the functions selected by each digit for these inputs. FN3166 Rev.4.00 Jan 7, 2004 Page 7 of 18 ICM7216B, ICM7216D COUNTED TRANSITIONS 50ns MIN INPUT A 4.5V 0.5V tr = tf = 10ns 50ns MIN FIGURE 6. WAVEFORM FOR GUARANTEED MINIMUM fA(MAX) FUNCTION = FREQUENCY, FREQUENCY RATIO, UNIT COUNTER 9. MEASURED INTERVAL 250ns MIN INPUT A OR 4.5V INPUT B 0.5V 250ns MIN tr = tf = 10s FIGURE 7. WAVEFORM FOR GUARANTEED MINIMUM fB(MAX) AND fA(MAX) FOR FUNCTION = PERIOD AND TIME INTERVAL Function Input The six functions that can be selected are: Frequency, Period, Time Interval, Unit Counter, Frequency Ratio and Oscillator Frequency. This input is available on the lCM7216B only. The implementation of different functions is done by routing the different signals to two counters, called “Main Counter” and “Reference Counter”. A simplified block diagram of the device for functions realization is shown in Figure 8. Table 2 shows which signals will be routed to each counter in different cases. The output of the Main Counter is the information which goes to the display. The Reference Counter divides its input by 1, 10, 100 and 1000. One of these outputs will be selected through the range selector and drive the enable input of the Main Counter. This means that the Reference Counter, along with its associated blocks, directs the Main Counter to begin counting and determines the length of the counting period. Note that Figure 8 does not show the complete functional diagram (See the Functional Block Diagram). After the end of each counting period, the output of the Main Counter will be latched and displayed, then the counter will be reset and a new measurement cycle will begin. Any change in the FUNCTION INPUT will stop the present measurement without updating the display and then initiate a new measurement. This prevents an erroneous first reading after the FUNCTION INPUT is changed. In all cases, the 1-0 transitions are counted or timed. INTERNAL CONTROL INTERNAL CONTROL 100Hz INPUT SELECTOR INPUT A CLOCK INPUT B REFERENCE COUNTER 1 INTERNAL CONTROL INTERNAL OR EXTERNAL OSCILLATOR INTERNAL CONTROL 100 1000 RANGE SELECTOR ENABLE INPUT SELECTOR INPUT A 10 CLOCK MAIN COUNTER FIGURE 8. SIMPLIFIED BLOCK DIAGRAM OF FUNCTIONS IMPLEMENTATION TABLE 2. 7216B INPUT ROUTING FUNCTION MAIN COUNTER REFERENCE COUNTER TABLE 2. 7216B INPUT ROUTING (Continued) FUNCTION MAIN COUNTER REFERENCE COUNTER Frequency (fA) Input A 100Hz (Oscillator 105 or 104) Unit Counter (Count A) Input A Not Applicable Period (tA) Oscillator Input A Oscillator 100Hz (Oscillator 105 or 104) Ratio (fA /fB) Input A Input B Osc. Freq. (fOSC) Time Interval (AB) Oscillator Input A Input B FN3166 Rev.4.00 Jan 7, 2004 Page 8 of 18 ICM7216B, ICM7216D Frequency - In this mode input A is counted by the Main Counter for a precise period of time. This time is determined by the time base oscillator and the selected range. For the 10MHz (or 1MHz) time base, the resolutions are 100Hz, 10Hz, 1Hz and 0.1Hz. The decimal point on the display is set for kHz reading. Period - In this mode, the timebase oscillator is counted by the Main Counter for the duration of 1, 10, 100 or 1000 (range selected) periods of the signal at input A. A 10MHz timebase gives resolutions of 0.1s to 0.0001s for 1000 periods averaging. Note that the maximum input frequency for period measurement is 2.5MHz. Frequency Ratio - In this mode, the input A is counted by the Main Counter for the duration of 1, 10, 100 or 1000 (range selected) periods of the signal at input B. The frequency at input A should be higher than input B for meaningful result. The result in this case is unitless and its resolution can go up to three digits after decimal point. Time Interval - In this mode, the timebase oscillator is counted by the Main Counter for the duration of a 1-0 transition of input A until a 1-0 transition of input B. This means input A starts the counting and input B stops it. If other ranges, except 0.01s/1 cycle are selected the sequence of input A and B transitions must happen 10, 100 or 1000 times until the display becomes updated; note this when measuring long time intervals to give enough time for measurement completion. The resolution in this mode is the same as for period measurement. See the Time Interval Measurement section also. Unit Counter - In this mode, the Main Counter is always enabled. The input A is counted by the Main Counter and displayed continuously. Oscillator Frequency - In this mode, the device makes a frequency measurement on its timebase. This is a self test mode for device functionality check. For 10MHz timebase the display will show 10000.0, 10000.00, 10000.000 and Overflow in different ranges. Range Input The RANGE INPUT selects whether the measurement period is made for 1, 10, 100 or 1000 counts of the Reference Counter. As it is shown in Table 1, this gives different counting windows for frequency measurement and various cycles for other modes of measurement. In all functional modes except Unit Counter, any change in the RANGE INPUT will stop the present measurement without updating the display and then initiate a new measurement. This prevents an erroneous first reading after the RANGE INPUT is changed. Control Input Unlike the other multiplexed inputs, to which only one of the digit outputs can be connected at a time, this input can be tied to different digit lines to select combination of controls. In this FN3166 Rev.4.00 Jan 7, 2004 case, isolation diodes must be used in digit lines to avoid crosstalk between them (see Figure 14). The direction of diodes depends on the device version, common anode or common cathode. For maximum noise immunity at this input, in addition to the 10K resistor which was mentioned before, a 39pF to 100pF capacitor should also be placed between this input and the VDD or VSS (See Figure 14). Display Off - To disable the display drivers, it is necessary to tie the D4 line to the CONTROL INPUT and have the HOLD input at VDD . While in Display Off mode, the segments and digit drivers are all off, leaving the display lines floating, so the display can be shared with other devices. In this mode, the oscillator continues to run with a typical supply current of 1.5mA with a 10MHz crystal, but no measurements are made and multiplexed inputs are inactive. A new measurement cycle will be initiated when the HOLD input is switched to VSS . Display Test - Display will turn on with all the digits showing 8s and all decimal points on. The display will be blanked if Display Off is selected at the same time. 1MHz Select - The 1MHz select mode allows use of a 1MHz crystal with the same digit multiplex rate and time between measurement as with a 10MHz crystal. This is done by dividing the oscillator frequency by 104 rather than 105. The decimal point is also shifted one digit to the right in period and time interval, since the least significant digit will be in s increment rather than 0.1s increment. External Oscillator Enable - In this mode, the signal at EXT OSC INPUT is used as a timebase instead of the on-board crystal oscillator (built around the OSC INPUT, OSC OUTPUT inputs). This input can be used for an external stable temperature compensated crystal oscillator or for special measurements with any external source. The on-board crystal oscillator continues to work when the external oscillator is selected. This is necessary to avoid hang-up problems, and has no effect on the chip's functional operation. If the on-board oscillator frequency is less than 1MHz or only the external oscillator is used, the OSC INPUT must be connected to the EXT OSC INPUT providing the timebase has enough voltage swing for OSC INPUT (See Electrical Specifications). If the external timebase is TTL level a pullup resistor must be used for OSC INPUT. The other way is to put a 22M resistor between OSC INPUT and OSC OUTPUT and capacitively couple the EXT OSC INPUT to OSC INPUT. This will bias the OSC INPUT at its threshold and the drive voltage will need to be only 2VP-P . The external timebase frequency must be greater than 100kHz or the chip will reset itself to enable the on-board oscillator. External Decimal Point Enable - In this mode, the EX DP INPUT is enabled (lCM7216D only). A decimal point will be displayed for the digit that its output line is connected to this input (EX DP INPUT). Digit 8 should not be used since it will override the overflow output. Leading zero blanking is effective for the digits to the left of selected decimal point. Page 9 of 18 ICM7216B, ICM7216D Hold Input Except in the unit counter mode, when the HOLD input is at VDD , any measurement in progress (before STORE goes low) is stopped, the main counter is reset and the chip is held ready to initiate a new measurement as soon as HOLD goes low. The latches which hold the main counter data are not updated, so the last complete measurement is displayed. In unit counter mode when HOLD input is at VDD , the counter is not stopped or reset, but the display is frozen at that instantaneous value. When HOLD goes low the count continues from the new value in the new counter. Table 3 shows the decimal point position for different modes of lCM7216 operation. Note that the digit 1 is the least significant digit. Table 3 is for 10MHz timebase frequency. Overflow Indication When overflow happens in any measurement it will be indicated on the decimal point of the digit 8. A separate LED indicator can be used. Figure 9 shows how to connect this indicator. RESET Input a f The RESET input resets the main counter, stops any measurement in progress, and enables the main counter latches, resulting in an all zero output. A capacitor to ground will prevent any hang-ups on power-up. b g e c DP d FIGURE 9. SEGMENT IDENTIFICATION AND DISPLAY FONT MEASUREMENT IN PROGRESS This output is provided in lCM7216D. It stays low during measurements and goes high for intervals between measurements. It is provided for system interfacing and can drive a low power Schottky TTL or one ECL load if the ECL device is powered from the same supply as lCM7216D. Overflow will be indicated on the decimal point output of digit 8. A separate LED overflow indicator can be connected as follows: DEVICE ICM7216B/D CATHODE ANODE D8 Decimal Point Decimal Point Position TABLE 3. DECIMAL POINT POSITIONS RANGE FREQUENCY PERIOD FREQUENCY RATIO TIME INTERVAL UNIT COUNTER OSCILLATOR FREQUENCY D2 D2 D1 D2 D1 D2 0.01s/1 Cycle 0.1s/10 Cycle D3 D3 D2 D3 D1 D3 1s/100 Cycle D4 D4 D3 D4 D1 D4 10s/1K Cycle D5 D5 D4 D5 D1 D5 Time Interval Measurement When in the time interval mode and measuring a single event, the lCM7216B must first be “primed” prior to measuring the event of interest. This is done by first generating a negative going edge on Channel A followed by a negative going edge on Channel B to start the “measurement interval”. The inputs are then primed ready for the measurement. Positive going edges on A and B, before or after the priming, will be needed to restore the original condition. Priming can be easily accomplished using the circuit in Figure 10 (next page). FN3166 Rev.4.00 Jan 7, 2004 Page 10 of 18 ICM7216B, ICM7216D SIGNAL A 2 INPUT A 2 INPUT B SIGNAL B VDD VDD PRIME N.O. 150K 1 1 1 1 10K 1N914 100K 0.1F VSS 10nF VSS DEVICE VSS TYPE 1 CD4049B Inverting Buffer 2 CD4070B Exclusive - OR FIGURE 10. PRIMING CIRCUIT, SIGNALS A AND B BOTH HIGH OR LOW Following the priming procedure (when in single event or 1 cycle range) the device is ready to measure one (only) event. When timing repetitive signals, it is not necessary to “prime” the lCM7216B as the first alternating signal states automatically prime the device. See Figure 1. During any time interval measurement cycle, the lCM7216B require 200ms following B going low to update all internal logic. A new measurement cycle will not take place until completion of this internal update time. Oscillator Considerations The oscillator is a high gain CMOS inverter. An external resistor of 10M to 22M should be connected between the OSCillator INPUT and OUTPUT to provide biasing. The oscillator is designed to work with a parallel resonant 10MHz quartz crystal with a static capacitance of 22pF and a series resistance of less than 35. For a specific crystal and load capacitance, the required gM can be calculated as follows: C O 2 2 g M = C IN C OUT R S 1 + -------- CL C IN C OUT where C L = --------------------------------- C IN + C OUT CO = Crystal Static Capacitance RS = Crystal Series Resistance CIN = Input Capacitance COUT = Output Capacitance = 2f The required gM should not exceed 50% of the gM specified for the lCM7216 to insure reliable startup. The OSCillator INPUT and OUTPUT pins each contribute about 5pF to CIN FN3166 Rev.4.00 Jan 7, 2004 and COUT . For maximum stability of frequency, CIN and COUT should be approximately twice the specified crystal static capacitance. In cases where non decade prescalers are used it may be desirable to use a crystal which is neither 10MHz or 1MHz. In that case both the multiplex rate and time between measurements will be different. The multiplex rate is f OSC f OSC f MUX = ------------------- for 10MHz mode and f MUX = ------------------- for the 4 3 2 10 2 10 6 2 10 1MHz mode. The time between measurements is ------------------- in f OSC 5 2 10 the 10MHz mode and ------------------- in the 1MHz mode. f OSC The crystal and oscillator components should be located as close to the chip as practical to minimize pickup from other signals. Coupling from the EXTERNAL OSClLLATOR INPUT to the OSClLLATOR OUTPUT or INPUT can cause undesirable shifts in oscillator frequency. Display Considerations The display is multiplexed at a 500Hz rate with a digit time of 244s. An interdigit blanking time of 6s is used to prevent display ghosting (faint display of data from previous digit superimposed on the next digit). Leading zero blanking is provided, which blanks the left hand zeroes after decimal point or any non zero digits. Digits to the right of the decimal point are always displayed. The leading zero blanking will be disabled when the Main Counter overflows. The lCM7216B and lCM7216D are designed to drive common cathode displays at peak current of 15mA/segment using displays with VF = 1.8V at 15mA. Resistors can be added in series with the segment drivers to limit the display current in very efficient displays, if required. The Typical Performance Curves show the digit and segment currents as a function of output voltage. To get additional brightness out of the displays, VDD may be increased up to 6.0V. However, care should be taken to see that maximum power and current ratings are not exceeded. The segment and digit outputs in lCM7216s are not directly compatible with either TTL or CMOS logic when driving LEDs. Therefore, level shifting with discrete transistors may be required to use these outputs as logic signals. Accuracy In a Universal Counter crystal drift and quantization effects cause errors. In frequency, period and time interval modes, a signal derived from the oscillator is used in either the Reference Counter or Main Counter. Therefore, in these modes an error in the oscillator frequency will cause an identical error in the measurement. For instance, an oscillator temperature coefficient of 20 PPM will cause a measurement ------------------o error of 20 PPM C ------------------o C Page 11 of 18 ICM7216B, ICM7216D In addition, there is a quantization error inherent in any digital measurement of 1 count. Clearly this error is reduced by displaying more digits. In the frequency mode the maximum accuracy is obtained with high frequency inputs and in period mode maximum accuracy is obtained with low frequency inputs (as can be seen in Figure 11). In time interval measurements there can be an error of 1 count per interval. As a result there is the same inherent accuracy in all ranges as shown in Figure 12. In frequency ratio measurement can be more accurately obtained by averaging over more cycles of INPUT B as shown in Figure 13. 0 0 FREQUENCY MEASURE 2 4 MAXIMUM NUMBER OF SIGNIFICANT DIGITS MAXIMUM NUMBER OF SIGNIFICANT DIGITS 1 0.01s 0.1s 1s 10s 1 CYCLE 10 CYCLES 102 CYCLES 103 CYCLES 6 1 10 103 FREQUENCY (Hz) MAXIMUM TIME INTERVAL FOR 103 INTERVALS 3 4 MAXIMUM TIME INTERVAL FOR 102 INTERVALS 5 6 MAXIMUM TIME INTERVAL FOR 10 INTERVALS 7 PERIOD MEASURE fOSC = 10MHz 8 2 8 105 1 107 102 10 103 104 105 106 107 108 TIME INTERVAL (s) FIGURE 11. MAXIMUM ACCURACY OF FREQUENCY AND PERIOD MEASUREMENTS DUE TO LIMITATIONS OF QUANTIZATION ERRORS FIGURE 12. MAXIMUM ACCURACY OF TIME INTERVAL MEASUREMENT DUE TO LIMITATIONS OF QUANTIZATION ERRORS 0 MAXIMUM NUMBER OF SIGNIFICANT DIGITS 1 RANGE 2 3 1 CYCLE 10 CYCLES 102 CYCLES 103 CYCLES 4 5 6 7 8 1 10 102 103 104 fA /fB 105 106 107 108 FIGURE 13. MAXIMUM ACCURACY FOR FREQUENCY RATIO MEASUREMENT DUE TO LIMITATION OF QUANTIZATION ERRORS FN3166 Rev.4.00 Jan 7, 2004 Page 12 of 18 ICM7216B, ICM7216D Test Circuit VDD VDD INPUT A FUNCTION GENERATOR VDD DISPLAY DISPLAY BLANK TEST 1MHz F P D8 FR D2 TI. D5 U.C. O.F. 10K D1 2 27 3 26 DP 4 25 e g 5 24 6 23 a 7 8 D4 D3 D4 28 1 INPUT B ICM7216A 22M D2 21 D3 d 9 20 D4 b 10 19 D5 c 11 18 f 12 17 D6 13 16 D7 14 15 D8 RESET D1 D5 EXT OSC INPUT TYPICAL CRYSTAL SPECS: F = 10MHz PARALLEL RESONANCE CL = 22pF RS = <35 VDD RANGE D1 8 LED OVERFLOW INDICATOR D2 1N914s 8 10k 6 D8 10MHz CRYSTAL D1 22 TEST 39pF TYP 39pF 10k FUNCTION GENERATOR FUNCTION 10k HOLD 100pF EXT OSC D2 D3 D4 a b c d e f g .01/1 4 .1/10 1/100 10/1K 8 DP D8 D8 D7 D6 D5 D4 D3 D2 D1 FIGURE 14. TEST CIRCUIT (ICM7216A SHOWN, OTHERS SIMILAR) Typical Applications The lCM7216 has been designed for use in a wide range of Universal and Frequency counters. In many cases, prescalers will be required to reduce the input frequencies to under 10MHz. Because INPUT A and INPUT B are digital inputs, additional circuitry is often required for input buffering, amplification, hysteresis, and level shifting to obtain a good digital signal. The lCM7216B can be used as a minimum component complete Universal Counter as shown in Figure 15. This circuit can use input frequencies up to 10MHz at INPUT A and 2MHz at INPUT B. If the signal at INPUT A has a very low duty cycle it may be necessary to use a 74LS121 monostable multivibrator or similar circuit to stretch the input pulse width to be able to guarantee that it is at least 50ns in duration. To measure frequencies up to 40MHz the circuit of Figure 16 can be used. To obtain the correct measured value, it is necessary to divide the oscillator frequency by four as well as the input frequency. In doing this the time between FN3166 Rev.4.00 Jan 7, 2004 measurements is also lengthened to 800ms and the display multiplex rate is decreased to 125Hz. If the input frequency is prescaled by ten, then the oscillator can remain at 10MHz or 1MHz, but the decimal point must be moved one digit to the right. Figure 17 shows a frequency counter with a 10 prescaler and an lCM7216A. Since there is no external decimal point control with the lCM7216B, the decimal point may be controlled externally with additional drivers as shown in Figure 17. Alternatively, if separate anodes are available for the decimal points, they can be wired up to the adjacent digit anodes. Note that there can be one zero to the left of the decimal point since the internal leading zero blanking cannot be changed. In Figure 18 additional logic has been added to count the input directly in period mode for maximum accuracy. In Figures 17 and 18, INPUT A comes from QC of the prescaler rather than QD to obtain an input duty cycle of 40%. Page 13 of 18 ICM7216B, ICM7216D VDD EXT DISPLAY DISPLAY OSC BLANK TEST ENABLE VDD INPUT A 10k 39pF TYP 100pF HOLD CONTROL SWITCHES 22M 1 28 2 27 3 26 D1 4 25 D3 5 24 D2 6 23 DP D4 7 22 g INPUT B 10k D1 F P D8 D2 F.R. T.I. D5 U.C. 8 D4 O.F. D3 FUNCTION 6 0.1F ICM7216B 100k 21 e 9 20 a 10 19 d D7 11 18 D8 12 17 b 13 16 c 14 15 RANGE D1 D2 10k D3 D6 D5 EXT OSC INPUT D4 SEC CYCLES D1 0.01 1.0 D2 0.1 10.0 D3 1.0 100.0 D4 10.0 1K VDD 8 SEGMENT DRIVERS f 8 D4 D3 8 a b c d e f g DP DIGIT DRIVERS D7 3 4 COMMON CATHODE LED DISPLAY D8 D1 1N914s VDD D6 8 D8 39pF D5 RESET D4 10MHz CRYSTAL D2 D1 D8 LED OVERFLOW INDICATOR FIGURE 15. 10MHz UNIVERSAL COUNTER FN3166 Rev.4.00 Jan 7, 2004 Page 14 of 18 ICM7216B, ICM7216D INPUT A J 3 P 1 CL K 2 C 1/ 74LS112 2 4 Q 6 Q 5 K 12 10 13 CL J 11 14 3k Q 9 Q 7 EXT OSC DISPLAY DISPLAY ENABLE OFF TEST VDD 10k 100pF 39pF 39pF HOLD 100k D1 28 1 2 27 D1 3 26 D3 4 25 D2 5 24 D4 6 23 22M DP g e 9 20 a D7 10 19 d D8 11 18 12 17 b 13 16 c 14 15 f D5 8 D6 RESET 8 ICM7216D LED OVERFLOW INDICATOR 22 8 VDD RANGE D1 D2 4 D3 COMMON CATHODE LED DISPLAY D4 D6 D2 a b c d e f g DP DP D8 D8 D7 D8 3 EXT OSC INPUT 10k a b c d e f g D4 1N914s 2.5MHz CRYSTAL 21 7 0.1F VDD VDD C 1/ 74LS112 2 P V+ 15 D5 D4 D3 D1 8 OVERFLOW INDICATOR FIGURE 16. 40MHz FREQUENCY COUNTER FN3166 Rev.4.00 Jan 7, 2004 Page 15 of 18 ICM7216B, ICM7216D VDD VDD INPUT B INPUT A CK1 CK2 QA QA QC VDD 3k 10k QC 30pF TYP 39pF HOLD 11C90 DP 1 28 2 27 3 26 4 25 e g 5 24 6 23 a 7 8 0.1F D8 F.R. D2 22M 22 D2 21 D3 9 20 D4 10 19 D5 c 11 18 f 12 17 D6 13 16 D7 14 15 D8 8 8 4 VSS 4 VDD 10k a b c d e f g 10MHz CRYSTAL D1 b 10k D1 ICM7216A 1N914 D7 d RESET P 10k 100pF 3k F DISPLAY TEST VDD CK1 CK2 74LS90 OR 11C90 VDD COMMON ANODE LED DISPLAY 1k DP RANGE D1 D2 D2 D3 D3 D4 D1 1k 2N2222 D4 40 DP D8 D8 D7 D6 D5 D4 D3 D2 D1 8 LED OVERFLOW INDICATOR FIGURE 17. 100MHz MULTIFUNCTION COUNTER FN3166 Rev.4.00 Jan 7, 2004 Page 16 of 18 ICM7216B, ICM7216D INPUT A 11C90 CK1 CK2 QA OC 3k 74LS00 VDD VDD VDD VDD 3k VDD 10k 10k 100pF 100k 10k VDD 1 28 2 27 3 26 4 25 e 5 24 g 6 23 a 7 V+ DP 8 0.1F 10k D1 13 CD4016 4 CONT 22 D2 21 D3 9 20 D4 b 10 19 D5 c 11 18 f 12 17 D6 13 16 D7 14 15 D8 8 1 CONT ICM7216A D8 5 D1 D3 10MHz CRYSTAL 8 4 1k 4 2N2222 VDD 10k a b c d e f g 10k 2N2222 22M d RESET 3 39pF HOLD FUNCTION SWITCH OPEN: FREQ. CLOSED: PERIOD 2 39pF TYP COMMON ANODE LED DISPLAY VSS RANGE D1 DP D2 D2 D3 D3 D4 D1 VSS 1k 1k 2N2222 D4 40 LED OVERFLOW D8 INDICATOR DP D8 D7 D6 D5 D4 D3 D2 D1 8 FIGURE 18. 100MHz FREQUENCY, 2MHz PERIOD COUNTER FN3166 Rev.4.00 Jan 7, 2004 Page 17 of 18 ICM7216B, ICM7216D Dual-In-Line Plastic Packages (PDIP) E28.6 (JEDEC MS-011-AB ISSUE B) N 28 LEAD DUAL-IN-LINE PLASTIC PACKAGE E1 INDEX AREA 1 2 3 INCHES N/2 SYMBOL -B- -C- SEATING PLANE A2 e B1 D1 A1 eC B 0.010 (0.25) M C A B S MAX NOTES - 0.250 - 6.35 4 0.015 - 0.39 - 4 A2 0.125 0.195 3.18 4.95 - B 0.014 0.022 0.356 0.558 - C L B1 0.030 0.070 0.77 1.77 8 eA C 0.008 0.015 0.204 0.381 - D 1.380 1.565 D1 0.005 - A L D1 MIN A E BASE PLANE MAX A1 -AD MILLIMETERS MIN C eB NOTES: 1. Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control. 2. Dimensioning and tolerancing per ANSI Y14.5M-1982. 35.1 39.7 5 - 5 0.13 E 0.600 0.625 15.24 15.87 6 E1 0.485 0.580 12.32 14.73 5 e 0.100 BSC 2.54 BSC - eA 0.600 BSC 15.24 BSC 6 3. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of Publication No. 95. eB - 0.700 - 17.78 7 L 0.115 0.200 2.93 5.08 4 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3. N 28 5. D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm). 6. E and eA are measured with the leads constrained to be perpendicular to datum -C- . 28 9 Rev. 1 12/00 7. eB and eC are measured at the lead tips with the leads unconstrained. eC must be zero or greater. 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm). 9. N is the maximum number of terminal positions. 10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm). © Copyright Intersil Americas LLC 2001-2004. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners. For additional products, see www.intersil.com/en/products.html Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at www.intersil.com/en/support/qualandreliability.html Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries. For information regarding Intersil Corporation and its products, see www.intersil.com FN3166 Rev.4.00 Jan 7, 2004 Page 18 of 18