* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download LVPECL terminations - A circuit approach

Power inverter wikipedia , lookup

Electrical ballast wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Three-phase electric power wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Power engineering wikipedia , lookup

Current source wikipedia , lookup

Stray voltage wikipedia , lookup

Voltage optimisation wikipedia , lookup

Voltage regulator wikipedia , lookup

Power MOSFET wikipedia , lookup

Distribution management system wikipedia , lookup

Schmitt trigger wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Electrical substation wikipedia , lookup

Mains electricity wikipedia , lookup

Alternating current wikipedia , lookup

Power electronics wikipedia , lookup

Buck converter wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Transmission line loudspeaker wikipedia , lookup

History of electric power transmission wikipedia , lookup

Two-port network wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

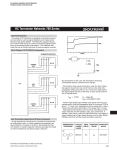

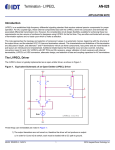

LVPECL terminations - A circuit approach Phillip Wissell - February 03, 2014 Introduction LVPECL is an established high-frequency differential signaling standard that dates back to the 1970s and earlier when high-speed IC technology was limited to NPN transistors only. Since only an active pull up could be implemented, external components are required to pull down the output passively. For DC-coupled LVPECL, these external components both bias the output driver into conduction and terminate the associated differential transmission line. However, the considerable circuit design flexibility available for achieving these two requirements when completing the output stage design can be a source of confusion for first time LVPECL users. They are often confronted with an array of termination options and no basis upon which to make a selection. This article approaches the topology and selection of component values in a systematic manner, beginning with the structure of the output driver and the standard VCC-2V bias and termination network. The characteristics and limitations of this termination are discussed in depth, and alternate T and PI terminations, which use fewer components and less power, are introduced and characterized. Additionally, the use of clock receivers with internal terminations and selection of bias resistors and coupling capacitors for AC terminations is covered. The LVPECL Driver A simplified LVPECL gate is typically implemented with an open emitter driver, as shown in Figure 1. Figure 1: Equivalent Schematic of an Open Emitter LVPECL driver. Three things can immediately be noted in Figure 1: 1. The output transistors are not turned on; therefore the driver will not produce an output. a. In order for Q and nQ to switch, each must be loaded with a dc path to ground. b. If the output is not to be used the Q and nQ pins can be floated to ensure the outputs are turned off, minimizing power and reducing noise. 2. The emitter currents of Q and nQ are determined by the selection of external pull down resistors. Different values for these resistors adjust for different VCCO voltages, power dissipation and p-p signal swing. 3. VCCO = VCC; Unlike LVCMOS, VCCO cannot be less than VCC to accommodate clock receivers using different supply voltages. As an example, VCC = 3.3V and VCCO = 2.5V will cause the output transistors to saturate, drastically reducing switching time. Differential-output LVPECL drivers are capable of operating at gigahertz frequencies, which requires that the associated LVPECL receivers are connected to the drivers through properly terminated transmission lines. Circuit designers can select terminations based on ease of component placement and power vs. performance tradeoffs, but should always verify signal integrity through simulations that include trace length and vias. DC-Coupled LVPECL Terminations Standard Termination Shown below in Figure 2 is the standard DC-coupled LVPECL termination. Figure 2: Standard LVPECL Termination. Referring to Figure 1, the nominal VTT voltage was set by applying Kirchoff's Voltage Law to the loop consisting of VCC (=VCCO), R1, Vbe of Q4 and Rterm when Q4 is at the logic low level and its emitter current is 2mA. VTT is a voltage branch put at the common node of the termination resistors to both satisfy KVL and ensure that the VTT voltage tracks VCC and VCCO. The benefit of VTT is that the driver output currents are unaffected by variations in the power supply voltage. This is particularly important for the logic low transistor; keeping it out of cutoff maintains the device's switching speed. The clear drawback of this termination scheme is that it requires a -2V regulator referenced to VCCO. Thevinin Equivalent Termination Thevinin Equivalent Termination In practice the VTT supply is often eliminated with the terminations of Figure 3 shown below, where both the VTT voltage and the 50-ohm termination resistor for each output are simultaneously realized by the Thevinin equivalents of two resistor bias strings. The separate terminations for Q and nQ allow for the option of Q and nQ to be routed separately on uncoupled transmission lines to different single ended loads. Figure 3: 3.3V and 2.5V Thevinin Equivalent LVPECL Terminations. There are five disadvantages of the Thevinin termination: 1. The bias string incurs its own power penalty in addition to the output driver emitter currents, about 80 mW per output pair on a 3.3V supply. 2. There is no remaining degree of freedom in the termination to accommodate variations in VCCO, temperature and device processing. 3. A fraction of the variations in VCCO are fed forward to the Thevinin equivalent VTT voltage by the bias voltage divider; 39% for VCCO=3.3V and 20% for VCCO=2.5V. Therefore control of the emitter currents, particularly for the logic low output, is not as effective as the standard VTT termination. 4. For a differential termination, only three resistors are actually required to realize one VTT voltage and two 50 ohm termination impedances. 5. For each of the Q and nQ signals, the two resistors connected to the clock receiver terminal add layout complexity and a performance penalty due to additional parasitic capacity over a single resistor. PI and T Shunt Terminations The disadvantages of the Thevinin termination can be either avoided or mitigated by the use of coupled transmission lines with the PI (aka Delta) or T (aka Y) resistor networks as shown in Figure 4. The common-mode impedance for the PI network is Rbias/2, and for the T network, Zo/2+RTT. The terminating impedance of the coupled transmission line for the PI network is Zdiff, which equals 2Zo and for the T network, is 2Zo directly. The common mode voltage across RTT has been named VTT by similarity to VTT = VCC-2.0V. Figure 4: T and PI LVPECL Termination Networks. The disadvantages of the Thevinin termination are addressed by these two networks as follows: 1. The power penalty of the Thevinin bias string is eliminated because the termination is powered directly from the driver currents. 2. The common mode impedance, and therefore negative feedback, can be adjusted to tradeoff driver current for variations in VCCO, temperature and device processing as shown below in Table 1. 3. The PI and T networks have better control of the emitter currents through common mode current feedback. Using as example the T network with RTT = 50 ohms and VCCO = 3.3V, the common mode feedback from VCCO to the VTT node is 66% (actually somewhat less due to the different operating points of the output transistors), this is 60% higher than that of the standard termination feed forward path. While this difference between the two terminations may not seem significant at first, it is significant when the relatively small voltage drop across the 50 ohm emitter resistor of the logic low transistor is considered. 4. Only three resistors are required, the minimum necessary to bias the two outputs and terminate the transmission line. For each network, the Q and nQ transmission lines must be coupled because each realizes a shunt termination. 5. Only one resistor terminal, and therefore associated parasitic capacity, is placed on each input terminal of the LVPECL receiver. Table 1 demonstrates how the PI and T terminations common-mode bias resistors can be adjusted to accommodate variations in VCCO and device processing. The IDT 853S006 was selected as a representative device whose LVPECL output is characterized for maximum and minimum logic 0 and logic 1 voltages across the industrial temperature range. Three cases are calculated: nominal VCCO voltage, the extreme corner case of -5% VCCO and minimum common mode output voltage over processing and temperature, and an intermediate case of only -5% VCCO. Table 1: Output Transistor Currents vs. T and PI Termination Bias Resistors The minimum bias current for a logic low, desirable for switching speed, is decreased proportionally to compensate for the increasingly lower probability of the two -5% VCCO cases. The bias resistors must decrease to accommodate the progressively lower emitter voltages of the output transistors as more variation in emitter voltages is introduced. Decreasing the bias resistors also increases the average bias current. Countering this trend is that decreasing the minimum Ibias, as expected, drops the average bias current. This effect is seen when comparing the 2.5V VCCO bias currents for the nominal and -5% cases. The average bias currents for the differential pair are calculated at the VCCO used for each case. In all cases the bias currents will increase when VCCO is +5%. The designer should select the resistor value bounded by these cases that best corresponds to the tolerances of their application. The PI Termination and Coupled Transmission Lines The PI Termination and Coupled Transmission Lines When incorporating the PI network of Figure 4 with a coupled transmission line, Zdiff is replaced with the equivalent impedance of a coupled transmission line terminated in Zdiff. This arrangement retains the advantages of using Rbias to set the driver Q and nQ bias currents independently and only one resistor parasitic per receiver terminal. Specific forms of the PI network are shown below in Figure 5. Figure 5: 3.3V and 2.5V External PI Terminations. This termination is most advantageous in board layout when terminating multiple LVPECL signals on a single package, such as a BGA. In fact this is the same advantage at the receiver as is afforded by LVDS. The Q and nQ outputs have only one Rbias resistor per transmission line, which makes it easy to place them on the same side of the PCB as the LVPECL driver, a significant signal integrity advantage. In some devices the LVPECL input stage integrates the 50-ohm differential termination resistors with the common-mode tap brought out to a package pin, typically labeled VT. When implementing the PI termination, the VT terminal is floated. The T Termination and Coupled Transmission Lines When incorporating the T network of Figure 4 with a coupled transmission line, the entire T network is placed at the LVPECL receiver end of the coupled transmission line. There is only one resistor parasitic per receiver terminal and the parasitic capacity associated with RTT does not affect differential mode signal integrity as it is located at the VTT common mode node. The T termination becomes preferred with large fan-out LVPECL devices, for example a 1:22 fan-out buffer where it may be difficult to fit all the pull-down bias resistors of the PI termination at the clock driver. Specific forms of the T network are shown below in Figure 6. For LVPECL devices with integrated 50-ohm differential termination resistors and a common-mode VT tap, the VT pin is pulled to ground through the external RTT resistor shown in these examples. Figure 6: 3.3V and 2.5V External T Terminations. LVPECL Bias for AC-Coupled Terminations Often LVPECL clock drivers must be AC coupled to a receiver of a different logic family with a different switching threshold voltage. The LVPECL output must still be dc biased but the use of blocking capacitors places the requirements to bias the receiver within its common-mode range and providing the transmission line termination impedance on the LVPECL receiver. The general external configuration for only the LVPECL driver is shown in Figure 7. Figure 7: General LVPECL Driver Bias for AC-Coupled Loads. The values for the Rbias resistors are to be taken from Table 1, which were calculated based on setting the output transistor emitter current at the switching threshold. The value of Cc is calculated based on the frequency of the clock and the magnitude of the impedance at the clock frequency. Coupling capacitor CC selection is based on the amount of parasitic reactance that the cap is allowed to introduce into the signal path. This maximum impedance is arbitrarily set at 0.2 ohms in order to calculate Table 2 (shown below) to associate standard cap values and their corresponding frequency ranges. Table 2: Standard Coupling Cap values vs. Clock Frequency. Conclusion LVPECL is an older technology that dates to when semiconductor processing had not yet matured to the point where high-performance P-type devices could be fabricated with high-performance N-type devices. Consequently the role of the P devices had to be handled with external passive elements. This requirement was exploited in LVPECL as well as the precursor to LVPECL, ECL, by merging the role of the passive pull-down function with that of a transmission line termination. Designers often have difficulty designing an appropriate LVPECL termination because the role of the termination in completing the output stage design is typically never reviewed. The intent of presenting LVPECL terminations from a circuit perspective is to show how the important factors, output transistor currents and minimizing component count and power, account for the LVPECL termination topologies and component values of common terminations. Contemporary semiconductor processing does produce high-performance P-type devices and the circuit consequences are the appearance of ground-referenced differential signaling families, such as HCSL and LVDS. These families eliminate the VTT requirement completely. More about Phillip Wissell.