* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Open Attachment

Index of electronics articles wikipedia , lookup

Spirit DataCine wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Digital electronics wikipedia , lookup

Power electronics wikipedia , lookup

Integrating ADC wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Radio transmitter design wikipedia , lookup

Phase-locked loop wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Mixing console wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Operational amplifier wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Schmitt trigger wikipedia , lookup

Current mirror wikipedia , lookup

Two-port network wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Opto-isolator wikipedia , lookup

Time-to-digital converter wikipedia , lookup

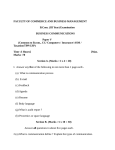

DEC Lab Quiz Roll No: (Q.1-5 each 2 marks & Q. 6-10 each 4 marks) Time: 30 mins Full Marks: 30 Name: 1. In a digital system there are 3 inputs A, B and C. The output should be high when atleast 2 inputs are high. The boolean expression for the output is ____AB+BC+CA_______________. 2. A 4 bit binary synchronous counter uses FFs with a propagation delay of 25ns. The maximum possible time required for change of state will be: (a) 25ns (b) 50ns (c) 75ns (d) 100ns (e) None of these 3. The initial state of a synchronous MOD-16 down counter is 0110. After 37 clock pulses, the state of the counter is __0001__________. 4. The minimum number of NAND gates required to implement a master slave FF is __9_____. 5. The IC number of 2 input AND gate is _IC 7408___________. 6. In ________________ condition Two input EX-OR gate behaves as an INVERTER.( one i/p must be high) 7. Shifting a register content to left by one bit position is equivalent to __MULTIPLICATION BY 2_________________. 8. The output of the following circuit is __0_________. 9. T h o u t 9.The Simplified result of Y(A,B,C,D)=m∑(0,1,2,3,5,9,13 )+ d∑m(14,16) is ....................(A’B’C+ C’D) 10. output of the 4 x 1 multiplexer shown in below figure is ___ Y X Y /X+Y__________________.