* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download click here - SMDP-VLSI

Audio power wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Public address system wikipedia , lookup

Signal-flow graph wikipedia , lookup

Multidimensional empirical mode decomposition wikipedia , lookup

Negative feedback wikipedia , lookup

Scattering parameters wikipedia , lookup

Current source wikipedia , lookup

Dynamic range compression wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Ground loop (electricity) wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Oscilloscope history wikipedia , lookup

Buck converter wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Schmitt trigger wikipedia , lookup

Regenerative circuit wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

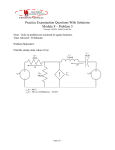

Two-port network wikipedia , lookup

DIFFERENTIAL AMPLIFIERS DIFFERENTIAL AMPLIFIER 1. VERY HIGH INPUT IMPEDENCE 2. VERY HIGH BANDWIDTH 3. DIFFERENTIAL INPUT 4. DC DIFFERENTIAL INPUT ACCEPTED 5. HIGH COMMON MODE REJECTION 6. SIGNAL INTEGRITY AT THE OUTPUT Let us start with a simple amplifier that can give us at the output a signal proportional to the difference between two signals, each with reference to a ground. In a MOSFET under small signal conditions the output current is proportional to the signal voltage across the gate and source. As is obvious any signal applied to the source needs to be preferably applied through a buffer to reduce loading, while that at the gate could be applied directly. It is evident from the circuit diagram that when we consider the output at transistor M2, vo2, we are looking at a cascade of CD amplifier followed by CG amplifier from vs1 to vo2 and CS amplifier from vs2 to v02. Similarly considering the output at transistor M1, vo1, we are looking at a cascade of CD amplifier followed by CG amplifier from vs2 to vo1 and CS amplifier from vs1 to v01. Assuming a total symmetrical circuit, it is sufficient to analyze the effect of any one signal input to analyze the total circuit. In analyzing the circuit we will use superposition theorem. Let us now look at the equivalent circuit and its analysis. We represent the current source ISS by its output impedance 1/go in the equivalent circuit. In the equivalent circuit vgs1 vgs2 vs1 vo1 gm1 vgs1 RL and vgs1 1 go gm1 vgs1 gm1 vgs2 vs1 Solving for vo1/vs1 from the above three equations we get gm1 1 vo1 go gm1 RL vs1 1 2gm1 go and gm1 g vo2 o gm1 RL vs1 1 2gm1 go Let us define the following: vo1 A11 ; vs1 vo1 A12 ; vs2 vo2 A21 vs1 and vo2 A22 vs2 For a symmetric network A11 = A22 and A12 = A21. We can then write vo1 A11 vs1 A12 vs2 and vo2 A21 vs1 A22 vs2 We can now recast the equations as v v vo1 Ad vs1 vs2 ACM s1 s2 2 v v vo2 Ad vs1 vs2 ACM s1 s2 2 where and A11 A12 gm1RL g R m1 L 2 2 1 2gm go go RL ACM A11 A12 2 Ad The signal (vs1 – vs2) is called the differential signal and the signal (vs1 + vs2) is called the Common Mode signal. This leads us to define a very important parameter defining a differential Amplifier, the Common Mode Rejection Ratio, CMRR. CMRR is defined as CMRR Ad ACM 1 2gm1 2 go gm1 g o Having evaluated the gains of differential and common mode gain an interesting fall out is what is popularly known as half circuit equivalent. This has been reduced to two half circuits to evaluate differential and common mode gain. These are Differential Common Mode Half Circuit Half Circuit Ad and A11 A12 gm1RL g R m1 L 2 2 1 2gm go go RL ACM A11 A12 2 The load Resistance used in a CMOS circuit could be each a PMOS transistor in saturation with a constant Gate to Source Voltage or Gate tied to Drain. In both these cases the load resistance is the same for M1 and M2. Let us now consider an nonsymmetric load on M1 and M2 and look at the outputs vo1 and vo2. For this circuit we will have g 1 gm go A11 m1 gm3 1 2 gm go g gm go A12 m1 gm3 1 2 gm go gm1 1 gm go A22 gd 1 2 gm go 3 g A21 m1 gd3 gm go 1 2g g m o This will give us the outputs vo1 and vo2 as vo1 Ad1 vs1 vs2 ACM1 vs1 vs2 2 vo2 Ad2 vs1 vs2 ACM2 A11 A12 where Ad1 and ACM1 A11 A12 2 ; ; vs1 vs2 Ad2 2 A22 A21 2 ACM2 A22 A21 Assuming that gm1 >> go, the values of Ad1, Ad2, ACM1 and ACM2 reduce to g Ad1 m1 2gm3 ; g Ad2 m1 2gd3 ; g ACM1 o 2gm3 ; g ACM2 o 2gd3 Now since we are interested only in single ended output (say) vo2, we will device a useful method to use the other output to our advantage. What we would like to do is to connect the output vo1 to the gate of M4. We will then get the most commonly used single ended differential amplifier structure overleaf. Solving for the circuit assuming gm1 , gm3 >> go, gd1, gd3 we obtain the differential and common mode gain as Ad gm1 gd1 gd3 Giving us and go gd1 ACM 2 g g g m 3 d 1 d 3 gm1 gm3 CMRR 2 go gd1 In our discussions so far we had considered NMOS input devices with PMOS load devices. It is equally likely that we may use PMOS input transistors and NMOS load transistors. The relative advantages of the NMOS input differential Amplifier and PMOS input Differential Amplifier will be seen as we go down the course. NMOS input pair: M5 Common Mode Input Range Lowest common mode input voltage at gate of M1(M2) v G1(min) = V SS + v GS3 + v SD1 - v SG1 for saturation, the minimum value of v SD1 = v SG1 - |V T1 | Therefore, v G1(min) = V SS + v GS3 - |V T1 | or ISS VG1 min VSS VTO3 | VTO1 | v G1(max) = V or DD - v SD5 - v SG1 VG1 max VDD VSD5 ISS | VTO1 | Thermal Noise 16 k T 2 veq th ' 3 2 K P I1 W1 L1 1 2 1 KN' W3 L3 2 1 ' K W L P 1 1 To reduce thermal noise we choose KN' W3 L3 1 K' W L P 1 1 and large value of gm1. Assume that V DD = 3V and that V SS = -3V. Using K’N = 2K’P 18 A/V2, 0.8V <VTO3 , VT1< 1.2V, find the common mode range for worst case conditions. Assume that ISS = 100A, W1/L1 = W2/L2 = 5, W3/L3 = W4/L4 = 1, and vSD5 = 0.2V. ISS VG1 min VSS VTO3 | VTO1 | 100 3 1.2 0.8 0.25V 18 VG1 max VDD VSD5 ISS | VTO1 | 100 3 0.2 1.2 0.6V 5 x9 The input common mode range is -0.25V to 0.6V. Slew Rate: This defines the rate at which the load capacitor charged. In other words it defines the rate dv/dt at the output. Slew rate is a measure of the output to follow the input signal. This is normally associated with large signal property. Under large signal, only one of M1 or M2 will be ON and the charging current will be I5. This gives a slew rate CL(VDD- VSS)/I5. Parasitic elements in the Differential Amplifier: CT = tail capacitor (common mode only) CM = mirror capacitor = Cdg1 + Cdb1 + Cgs3 + Cgs4 + Cdb3 COUT = output capacitor » Cbd4 + Cbd2 + Cgd2 + CL Noise Sources in Differential Amplifiers: Noise can be normally modeled as a current source in parallel to iD. This current source represents two sources of noise, thermal noise and flicker noise. The mean square current noise source is defined as 8kT gm 1 (KF) ID 2 in f 2 3 f Cox L where f Bandwidth at frequency f KF Flicker Noise Coefficien t gmbs gm The mean square noise reflected to the gate giving mean square voltage noise at the gate 2 veq 8kT 1 (KF) f 2 ' gm 3gm f Cox WLK in2 The total output noise current, is obtained by summing each of the noise current contributions. 2 2 2 2 2 2 2 2 2 2 2 ito gm v g v g v g v g v 1 eq1 m1 eq2 m3 eq3 m3 eq 4 m1 eq where g2 m3 v 2 v 2 2 2 2 veq veq v 1 eq2 eq 4 g2 eq3 m1 Assu min g Identical N and P Transistor s g2 m3 2v 2 2 2 veq 2 veq 1 2 eq3 g m1 The total 1/f and thermal noise contributions can be written as 2 ' B 2 B K L p 2 1 N N 1 veq 1 / f K' B L f W1 L1 P P 3 16 k T 2 veq th 1 3 2K' I W L 2 1 1 P 1 where BN,P KF 2 Cox KN' ,P 1 ' 2 KN W3 L3 1 ' KP W1 L1 1/f Noise 2 ' 2 B K B L p 2 N N 1 1 veq 1 / f K' B L f W1 L1 P P 3 To get the input noise for NMOS input stages interchange BP for BN, KN’ for KP’ and vice versa. Since BN = 5BP it is preferable to use PMOS input stage to reduce 1/f noise with large area for M1 and M2 and 2 KN' BN L1 1 ' K B L P P 3