N.A. Sales Training Telcom Overview - ESET-Wiki

... protection while the data lines and power bus are protected from ESD with a twochannel diode array (1pF). Companion Solutions: Other solutions within the LF portfolio exist in addition to these recommendations. For example, if the operating current on the power bus is higher or lower, an appropriate ...

... protection while the data lines and power bus are protected from ESD with a twochannel diode array (1pF). Companion Solutions: Other solutions within the LF portfolio exist in addition to these recommendations. For example, if the operating current on the power bus is higher or lower, an appropriate ...

English - SMC ETech

... Warning (1) The compatibility of the product is the responsibility of the person who designs the equipment or decides its specifications. Since the product specified here is used under various operating conditions, its compatibility with specific equipment must be decided by the person who designs t ...

... Warning (1) The compatibility of the product is the responsibility of the person who designs the equipment or decides its specifications. Since the product specified here is used under various operating conditions, its compatibility with specific equipment must be decided by the person who designs t ...

NTB0104 1. General description Dual supply translating transceiver; auto direction sensing;

... Product data sheet ...

... Product data sheet ...

Space Qualification and Performance Results of the SIDECAR ASIC

... SIDECAR ASIC requires a number of bypass capacitors close to the chip. In case of the generic package approach presented in the previous section, the capacitors are placed on the board next to the SIDECAR socket. For JWST, however, a different packaging approach was chosen to be able to retrofit the ...

... SIDECAR ASIC requires a number of bypass capacitors close to the chip. In case of the generic package approach presented in the previous section, the capacitors are placed on the board next to the SIDECAR socket. For JWST, however, a different packaging approach was chosen to be able to retrofit the ...

NTB0102 1. General description Dual supply translating transceiver; auto direction sensing;

... Product data sheet ...

... Product data sheet ...

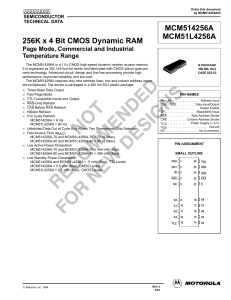

256K x 4 Bit CMOS Dynamic RAM MCM514256A MCM51L4256A

... strobe (RAS) and column address strobe (CAS), into two separate 9-bit address fields. A total of eighteen address bits, nine rows and nine columns, will decode one of the 262,144 bit locations in the device. RAS active transition is followed by CAS active transition (active = VIL, tRCD minimum) for ...

... strobe (RAS) and column address strobe (CAS), into two separate 9-bit address fields. A total of eighteen address bits, nine rows and nine columns, will decode one of the 262,144 bit locations in the device. RAS active transition is followed by CAS active transition (active = VIL, tRCD minimum) for ...

UJA1075A 1. General description High-speed CAN/LIN core system basis chip

... cyclic wake-up and by the activation of external switches. Additionally, it provides a periodic control signal for pulsed testing of wake-up switches, allowing low-current operation even when the wake-up switches are closed in Standby mode. All transceivers are optimized to be highly flexible with r ...

... cyclic wake-up and by the activation of external switches. Additionally, it provides a periodic control signal for pulsed testing of wake-up switches, allowing low-current operation even when the wake-up switches are closed in Standby mode. All transceivers are optimized to be highly flexible with r ...

RTC_PS3-27__submission_readback

... during readout it uses a common clock for both functions.) A sampling frequency of 37.532 MHz is used, which is four times the RHIC bunch crossing clock. This was chosen to provide sufficient samples to determine the leading edge of a signal pulse (with a typical peaking time of order 50 to 100 ns) ...

... during readout it uses a common clock for both functions.) A sampling frequency of 37.532 MHz is used, which is four times the RHIC bunch crossing clock. This was chosen to provide sufficient samples to determine the leading edge of a signal pulse (with a typical peaking time of order 50 to 100 ns) ...

NMEA Data Multiplexer NDC-4 Install User Manual

... standard - only one device on a connected network can actually send data (a single talker), with multiple devices (determined by the current limit of the sending unit) listening to that data (multiple listeners). If the vessel owner has an instrument that ideally requires the data output of two or m ...

... standard - only one device on a connected network can actually send data (a single talker), with multiple devices (determined by the current limit of the sending unit) listening to that data (multiple listeners). If the vessel owner has an instrument that ideally requires the data output of two or m ...

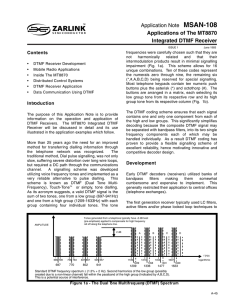

MSAN-108 - Applications of The MT8870 Integrated DTMF Receiver

... active filters to bandsplit the composite signal and MOS digital devices to decode the tones. The development of silicon-implemented switched capacitor sampled filters marked the birth of the fourth and current generation of DTMF receiver technology. Initially single chip bandpass filters were combi ...

... active filters to bandsplit the composite signal and MOS digital devices to decode the tones. The development of silicon-implemented switched capacitor sampled filters marked the birth of the fourth and current generation of DTMF receiver technology. Initially single chip bandpass filters were combi ...

MSAN-108 - Applications of The MT8870 Integrated

... active filters to bandsplit the composite signal and MOS digital devices to decode the tones. The development of silicon-implemented switched capacitor sampled filters marked the birth of the fourth and current generation of DTMF receiver technology. Initially single chip bandpass filters were combi ...

... active filters to bandsplit the composite signal and MOS digital devices to decode the tones. The development of silicon-implemented switched capacitor sampled filters marked the birth of the fourth and current generation of DTMF receiver technology. Initially single chip bandpass filters were combi ...

Chapter 6

... 24 pins for I/O : programmable in groups of 12 pins groups that operate in three distinct modes of operation interface any TTL-compatible I/O device to µ require wait states if operated with µ higher than 8MHz provided at least 2.5 mA of sink current at each output, with a maximum of 4.0 mA Fig. 11- ...

... 24 pins for I/O : programmable in groups of 12 pins groups that operate in three distinct modes of operation interface any TTL-compatible I/O device to µ require wait states if operated with µ higher than 8MHz provided at least 2.5 mA of sink current at each output, with a maximum of 4.0 mA Fig. 11- ...

Survey of Noise Sources in Bulk CMOS

... MOSFETs, using the assumption that the necessary time constants are caused by the tunneling of carriers from the channel into traps located inside the oxide. A number of other applications of the McWhorter theory to MOSFETs have been done. Das and Moore [12] reviewed and compared a number of these t ...

... MOSFETs, using the assumption that the necessary time constants are caused by the tunneling of carriers from the channel into traps located inside the oxide. A number of other applications of the McWhorter theory to MOSFETs have been done. Das and Moore [12] reviewed and compared a number of these t ...

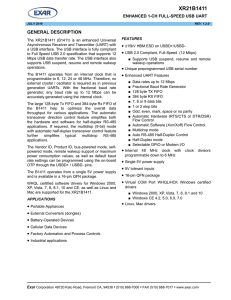

XR21B1411

... programmable to 6, 12, 24 or 48 MHz. Therefore, no external crystal / oscillator is required as in previous generation UARTs. With the fractional baud rate generator, any baud rate up to 12 Mbps can be accurately generated using the internal clock. The large 128-byte Tx FIFO and 384-byte Rx FIFO of ...

... programmable to 6, 12, 24 or 48 MHz. Therefore, no external crystal / oscillator is required as in previous generation UARTs. With the fractional baud rate generator, any baud rate up to 12 Mbps can be accurately generated using the internal clock. The large 128-byte Tx FIFO and 384-byte Rx FIFO of ...

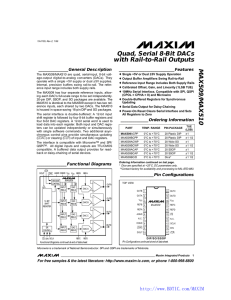

MAX509/MAX510 Quad, Serial 8-Bit DACs with Rail-to-Rail Outputs _______________General Description

... The MAX509/MAX510 are quad, serial-input, 8-bit voltage-output digital-to-analog converters (DACs). They operate with a single +5V supply or dual ±5V supplies. Internal, precision buffers swing rail-to-rail. The reference input range includes both supply rails. The MAX509 has four separate reference ...

... The MAX509/MAX510 are quad, serial-input, 8-bit voltage-output digital-to-analog converters (DACs). They operate with a single +5V supply or dual ±5V supplies. Internal, precision buffers swing rail-to-rail. The reference input range includes both supply rails. The MAX509 has four separate reference ...

1Gb DDR2 SDRAM

... input buffers and output drivers. Taking CKE LOW provides PRECHARGE POWER DOWN and SELF REFRESH operation (all banks idle), or ACTIVE POWER DOWN (row ACTIVE in any bank). CKE is synchronous for POWER DOWN entry and exit, and for SELF REFRESH entry. CKE is asynchronous for SELF REFRESH exit. After VR ...

... input buffers and output drivers. Taking CKE LOW provides PRECHARGE POWER DOWN and SELF REFRESH operation (all banks idle), or ACTIVE POWER DOWN (row ACTIVE in any bank). CKE is synchronous for POWER DOWN entry and exit, and for SELF REFRESH entry. CKE is asynchronous for SELF REFRESH exit. After VR ...

cmos area image sensors with pixel level ad conversion

... I would like to rst and foremost thank my loving wife Roe Turco-Fowler for her support and encouragement, especially during the writing of this thesis. I also want to thank my parents Albert and Shirely Fowler, my sisters Mary Husted and Kimerly Fowler, my aunt Ruth Fowler, and my cousin Chris Fowl ...

... I would like to rst and foremost thank my loving wife Roe Turco-Fowler for her support and encouragement, especially during the writing of this thesis. I also want to thank my parents Albert and Shirely Fowler, my sisters Mary Husted and Kimerly Fowler, my aunt Ruth Fowler, and my cousin Chris Fowl ...

NTB0101 1. General description Dual supply translating transceiver; auto direction sensing;

... Product data sheet ...

... Product data sheet ...

lvdswp.pdf

... The faster the transition time (i.e., edge rate), the higher the potential data rate. To provide switching speeds in the hundreds-of-Mbps range, the LVDS standard typically has a low-voltage signal level of 350 mV. Since there is little margin for noise with a swing that small, a differential data t ...

... The faster the transition time (i.e., edge rate), the higher the potential data rate. To provide switching speeds in the hundreds-of-Mbps range, the LVDS standard typically has a low-voltage signal level of 350 mV. Since there is little margin for noise with a swing that small, a differential data t ...

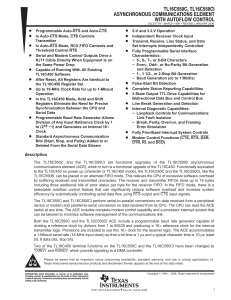

Asynchronous Communications Element With

... status at any time. The ACE includes complete modem control capability and a processor interrupt system that can be tailored to minimize software management of the communications link. Both the TL16C550C and the TL16C550CI ACE include a programmable baud rate generator capable of dividing a referenc ...

... status at any time. The ACE includes complete modem control capability and a processor interrupt system that can be tailored to minimize software management of the communications link. Both the TL16C550C and the TL16C550CI ACE include a programmable baud rate generator capable of dividing a referenc ...

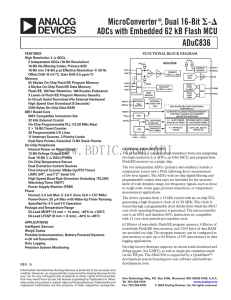

MicroConverter , Dual 16-Bit ADCs with Embedded 62 kB Flash MCU ADuC836

... two high resolution - ADCs, an 8-bit MCU, and program/data Flash/EE memory on a single chip. The two independent ADCs (primary and auxiliary) include a temperature sensor and a PGA (allowing direct measurement of low level signals). The ADCs with on-chip digital filtering and programmable output d ...

... two high resolution - ADCs, an 8-bit MCU, and program/data Flash/EE memory on a single chip. The two independent ADCs (primary and auxiliary) include a temperature sensor and a PGA (allowing direct measurement of low level signals). The ADCs with on-chip digital filtering and programmable output d ...

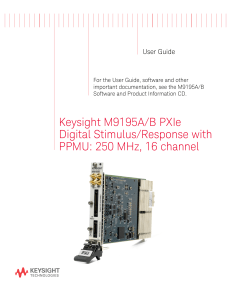

Keysight M9195A/B PXIe Digital Stimulus/Response with PPMU

... license and may be used or copied only in accordance with the terms of such license. ...

... license and may be used or copied only in accordance with the terms of such license. ...

BOOK OF ABSTRACTS 11 International Workshop on Finite Elements

... mountain-view location, offering old-world charm matched with the latest of modern amenities. Located at an elevation of 7,500 feet (2,286 meters) and within sight of the Rocky Mountain National Park, it was built in 1907-1909 by the inventor of the Stanley Steamer automobile (which is on display in ...

... mountain-view location, offering old-world charm matched with the latest of modern amenities. Located at an elevation of 7,500 feet (2,286 meters) and within sight of the Rocky Mountain National Park, it was built in 1907-1909 by the inventor of the Stanley Steamer automobile (which is on display in ...

TLC2554 数据资料 dataSheet 下载

... analog inputs and internal test voltages The 4/8 analog inputs and three internal test inputs are selected by the analog multiplexer depending on the command entered. The input multiplexer is a break-before-make type to reduce input-to-input noise injection resulting from channel switching. pseudo-d ...

... analog inputs and internal test voltages The 4/8 analog inputs and three internal test inputs are selected by the analog multiplexer depending on the command entered. The input multiplexer is a break-before-make type to reduce input-to-input noise injection resulting from channel switching. pseudo-d ...

On-Chip Signaling Techniques for High-Speed SerDes Transceivers The American University in Cairo

... Table 4.2 The results summary of the design in this chapter in TSMC 65nm CMOS technology 45 Table 4.3 The area distribution of the different parts of the design ............................................ 60 Table 4.4 The post layout results summary of the design in UMC 0.13μm CMOS ................ ...

... Table 4.2 The results summary of the design in this chapter in TSMC 65nm CMOS technology 45 Table 4.3 The area distribution of the different parts of the design ............................................ 60 Table 4.4 The post layout results summary of the design in UMC 0.13μm CMOS ................ ...