* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download ispPAC-POWR1220AT8 Evaluation Board

Phone connector (audio) wikipedia , lookup

Printed circuit board wikipedia , lookup

Alternating current wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Voltage optimisation wikipedia , lookup

Power electronics wikipedia , lookup

Opto-isolator wikipedia , lookup

Buck converter wikipedia , lookup

Power MOSFET wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Electrical connector wikipedia , lookup

Rectiverter wikipedia , lookup

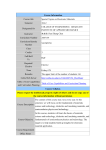

PAC-POWR1220AT8-EV Evaluation Board March 2007 Application Note AN6065 Introduction Lattice Semiconductor’s Power Manager II ispPAC®-POWR1220AT8 device simplifies power supply design by integrating the analog and digital functions of power supply management (sequencing, monitoring, trimming/margining, measurement) into a single device. This device provides designers with a rich set of features: A/D and D/A conversion, precision comparators with a built-in voltage reference, MOSFET drivers with programmable slew rates, an easy-to-use closed-loop power supply voltage trim system, and a programmable logic device (PLD) for sequencing and supervisory logic functions. All of these blocks can be accessed via I2C for enhanced flexibility in systems employing an on-board microcontroller. Configuration for all subsystems in the ispPAC-POWR1220AT8 device is stored in non-volatile E2CMOS® memory. Programming is performed via the industry-standard JTAG IEEE 1149.1 interface. PAC-POWR1220AT8-EV Evaluation Board The PAC-POWR1220AT8-EV evaluation board (Figure 1) allows the designer to quickly configure and evaluate the ispPAC-POWR1220AT8 device on a fully assembled printed-circuit board. The four-layer board supports a 100-pin TQFP package, pads for user I/O, a JTAG programming cable connector, and a connector for the device's I2C interface. JTAG programming signals can be generated by using an ispDOWNLOAD® programming cable connected between the evaluation board and a PC’s parallel (printer) port. Both analog and digital features of the ispPACPOWR1220AT8 device can be easily configured using PAC-Designer® software. The actual size of the board is 5” x 4” (12.5 x 10 cm). The I2C interface includes circuitry to allow the use of either an ispDOWNLOAD cable or standard open collector I2C bus. The I2C software utility that is included in PAC-Designer makes use of the ispDOWNLOAD cable interface to allow designers to evaluate the device’s I2C capabilities without having to buy additional cables or adapters. More information about this software tool can be found in application note AN6067, ispPAC-POWR1220AT8 I2C Hardware Verification Utility Users Guide. Extra pads are provided adjacent to the I2C connector to allow the user to easily access the SDA and SCL signals as well as the regulated 3.3 volt VCC supply. Connection to a standard I2C bus or cable is done simply by connecting to the SDA, SCL, and GND pins of J5; pin #3 is left floating. Connection to an ispDOWNLOAD cable is done simply by mating the ispDOWNLOAD cable’s connector to the I2C header (J5). Figure 1. PAC-POWR1220AT8-EV Evaluation Board © 2007 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice. www.latticesemi.com 1 an6065_01.2 Lattice Semiconductor PAC-POWR1220AT8-EV Evaluation Board Programming Interface Lattice Semiconductor’s ispDOWNLOAD cable can be used to program the ispPAC-POWR1220AT8 device on the evaluation board. This cable plugs into a PC-compatible's parallel port connector, and includes active buffer circuitry inside its DB-25 connector housing. The other end of the ispDOWNLOAD cable terminates in an 8-pin 0.100” pitch header connector which plugs directly into a mating connector provided on the PAC-POWR1220AT8-EV evaluation board (J4). Power Supply Considerations The ispPAC-POWR1220AT8 device operates with analog and digital core power supplies of 3.3V, To simplify evaluation work, the evaluation board was designed to operate from a single 4.5V to 5.5V power supply, which may be brought in through either a pair of banana plugs (J2 and J3), or a standard 5mm power plug (J1 - center tip positive). The evaluation board provides a linear regulator to provide the appropriate operating voltages for the ispPACPOWR1220AT8 device, as well as reverse polarity protection. Input/Output Connections Connectors are provided for key functions and test points on this evaluation board, as shown In Figure 2. Power may be supplied in one of two ways; either through two color coded (RED = +, BLACK = -) banana jacks in the upper right corner of the board or through a 5mm (center pin +) DC power connector (J1), The JTAG programming cable is connected to a keyed header (J4) in the upper right corner of the board. Another header (J5) provides access to the device’s I2C port. This header is pinned-out, and associated with interface circuitry so that in addition to providing a standard I2C bus connection (with on-board 2K pull-ups to 3.3V), it may also be driven by the Lattice DL2download cable when the “Power Manager I2C Utility” in PAC-Designer is used. Access to a subset of the ispPAC-POWR1220AT8 device’s I/O pins is available along the left edge of the assembly, where a 2x34 block of pads supports the attachment of test probes or a ribbon-cable connector. Pads for accessing the ATDI and TDISEL signals are provided immediately below the JTAG header (J4). An auxiliary connection for OUT5/SMB Alert is provided on a pad below the I2C header (J5). Figure 2. I/O Connections, Controls and Indicators 2 Lattice Semiconductor PAC-POWR1220AT8-EV Evaluation Board Controls and Indicators Two momentary switches, S2 and S3, are provided on the evaluation board. They are connected to IN4 and IN5, respectively. An 8-position dipswitch (S1) is provided on the evaluation board for the purpose of setting device inputs. Table 1 shows the options controlled by each switch: Table 1. Switch S1 User Configuration Functions Position Function (when ON) 1 VPS1 – Voltage Profile Select bit 1 2 VPS0 – Voltage Profile Select bit 0 3 TDISEL 4 IN1 5 IN2 6 IN3 7 VMON12_POT 8 VMON11_POT Switch positions 1 through 6 control logic inputs. When the switch is turned ON, the corresponding logic input goes HIGH. If a logic input is to be driven from an external signal source, then its associated DIP switch should be set to the OFF position. Switch positions 1 and 2 control Voltage Profile Select pins VPS1 and VPS0, respectively. If the device has been programmed for voltage profile control via VPS0 and VPS1, then these switches are used to select the active voltage profile. Switch position 3 controls the TDI selector pin, TDISEL. This switch should be in the ON position in order to program the device through J4. Switch positions 4-6 control logic inputs IN1-IN3, respectively. When in the ON position, switches 7 and 8 connect VMON11 and VMON12 to the two linear potentiometers provided on the board. This lets the user interactively apply analog voltages to the VMON11 and VMON12 inputs without the use of additional hardware. Note that the ground-sense pins for VMON11 and VMON12 have been hardwired to ground in order to support this feature. Several red LEDs are also provided on the evaluation board to indicate proper function and as aids to debugging. LED D2 indicates that the on-board 3.3V supply is powered up. LED D3 is connected to the ispPACPOWR1220AT8 device’s TDO line, and will briefly flash when downloading, indicating that download data has made it to the device. LEDs are also provided on digital outputs OUT5 through OUT20 so that a user may easily monitor the progress of sequence programs run on the evaluation board. Each of these LEDs uses a dual-resistor bias circuit that provides CMOS-3.3V compatible logic levels. Schematics The following four figures comprise the schematics for the ispPAC-POWR1220AT8-EV evaluation board. Figure 3 shows the on-board power-supply circuitry, Figure 4 shows the LED display and I2C adapter circuitry, Figure 5 shows user control circuits, while Figure 6 shows connections to the device itself. 3 Lattice Semiconductor PAC-POWR1220AT8-EV Evaluation Board Figure 3. On-Board Power Supply U2 D1 + C1 10µF J2 GND BANANA (BLACK) C3 0.1µF TPS77733 1 5 OUT 6 OUT +3.3V C4 0.1µF + C2 10 µF ENb +5V BANANA (RED) 3 IN 4 IN GND J3 2 J1 5mm Power Jack + Figure 4. LED Indicators and I2C Port Interface +3.3V +3.3V R1 2K 13 D2 1 D4 2 3 4 D5 R2 2K 14 5 6 7 12 D7 11 10 9 8 13 D9 D11 11 10 1 2 3 5 6 RESET VCC J1.1 SDA SDA J1.2 SCL SDIN J1.3 GND J1.7 SCL J1.8 D12 D13 4 D15 D8 D10 12 D14 D6 ‘PWR’ OUT5 OUT11 OUT6 OUT12 OUT7 OUT13 OUT8 OUT14 OUT9 OUT15 OUT10 OUT16 +3.3V R3 2K 14 13 D16 12 11 D17 1 2 D18 3 4 5 6 D19 8 9 10 7 D20 OUT17 OUT18 OUT19 OUT20 +3.3V TDO ATDI +3.3V R6 4.7k Q2 R11 4.7k Q1 R12 4.7k 4 R5 4.7k 7 8 Lattice Semiconductor PAC-POWR1220AT8-EV Evaluation Board Figure 5. User Controls +3.3V S1 R13 1k VPS1 VPS0 TDISEL IN1 IN2 IN3 1 R14 1k 2 R15 1k 3 R16 1k 4 R17 1k 5 R18 1k 6 +3.3V R8 1k R10 220 VMON12 C10 0.1uF 7 VMON12 8 +3.3V VMON11 IN4 IN5 R19 1k S2 R20 1k S3 13 14 1 2 3 4 5 6 7 R4 2K 5 R7 1k R9 220 C9 0.1uF VMON11 Lattice Semiconductor PAC-POWR1220AT8-EV Evaluation Board Figure 6. Device Connections +3.3V IN1 IN2 IN3 97 1 2 4 IN4 IN5 IN6 PLDCLK MCLK VPS0 VPS1 SDA SCL RESETb VCCPROG 6 7 95 96 89 90 93 92 91 39 VCCJ VCCD VCCA VCCINP VCCD HVOUT1 HVOUT2 HVOUT3 HVOUT4 OUT5/SMBA OUT6 VMON5GS VMON6 VMON6GS VMON7 VMON7GS VMON8 OUT7 OUT8 OUT9 OUT10 OUT11 OUT12 U1 ispPACPOWR1220AT8 VMON8GS VMON9 VMON9GS VMON10 VMON10GS VMON11 VMON11GS OUT13 OUT14 OUT15 OUT16 OUT17 OUT18 OUT19 VMON12 VMON12GS OUT20 TRIM1 TRIM2 TRIM3 TRIM4 IN1 IN2 IN3 IN4 IN5 IN6 TRIM5 TRIM6 TRIM7 TRIM8 PLDCLK MCLK ATDI TDISEL TDO TDI TMS TCK VPS0 VPS1 SDA SCL RESETb VCCPROG 3 22 36 43 88 GNDA 72 71 VMON2GS VMON3 VMON3GS VMON4 VMON4GS VMON5 GNDA VMON12 33 GNDD 68 67 70 69 94 GNDD VMON10 VMON10GS VMON11 60 GNDD 66 65 5 GNDD 57 62 61 64 63 38 GNDD VMON7 VMON7GS VMON8 VMON8GS VMON9 VMON9GS 52 51 54 53 56 55 58 VMON1 VMON1GS VMON2 GNDD VMON3GS VMON4 VMON4GS VMON5 VMON5GS VMON6 VMON6GS 47 46 50 48 VCCD 13 VMON1 VMON1GS VMON2 VMON2GS VMON3 98 45 87 +3.3V C5 C6 C7 C8 0.1uF 0.1uF 0.1uF 0.1uF (94) (13) (38) (60) 6 86 85 42 40 8 9 10 11 12 14 15 16 17 18 19 20 21 23 24 25 84 83 82 80 79 75 74 73 30 32 34 31 28 37 HVOUT1 HVOUT2 HVOUT3 HVOUT4 OUT5 OUT6 OUT7 OUT8 OUT9 OUT10 OUT11 OUT12 OUT13 OUT14 OUT15 OUT16 OUT17 OUT18 OUT19 OUT20 TRIM1 TRIM2 TRIM3 TRIM4 TRIM5 TRIM6 TRIM7 TRIM8 ATDI TDISEL +3.3V VCC J4.1 TDO J4.2 TDI J4.3 TMS J4.6 GND J4.7 TCK J4.8 Lattice Semiconductor PAC-POWR1220AT8-EV Evaluation Board PCB Artwork Figure 7. Silk Screen Figure 8. Component Side Copper (Layer 1) 7 Lattice Semiconductor PAC-POWR1220AT8-EV Evaluation Board Figure 9. Ground Plane (Layer 2) Figure 10. Power Plane (Layer 3) 8 Lattice Semiconductor PAC-POWR1220AT8-EV Evaluation Board Figure 11. Solder-side Copper (Layer 4) Component List Quantity Reference Designators 2 C1, C2 Description 8 C3 to C10 0.1µF 0603 SMD cap, Panasonic ECJ-1VB1C104K 1 D1 Schottky diode, International Rectifier MBRS130LTR 18 D2 to D19 1 J1 5mm DC power connector, CUI PJ-102BH 1 J2 Banana Jack, red, SPC Technology 845-R 1 J3 Banana Jack, Black, SPC Technology 845-B 2 J4, J5 1 Q1 MMBT3904LT1 NPN transistor, On-Semiconductor 1 Q2 MMBT3906LT1 PNP transistor, On-Semiconductor 4 R1, R2, R3, R4 2 R5, R6, R11, R12 2 R7, R8 2 R9, R10 2 S2, S3 8 R13 to R20 1 S1 8-position dipswitch, CTS 206-8ST 1 U1 ispPAC-POWR1220AT8 1 U2 3.3V fixed regulator SOIC8, Texas Instruments TPS77733D 1 n/a Printed circuit board, 4” x 5”, 4-layer 4 n/a Rubber feet, 3M SJ-5003 10µF 10V tantalum cap, Nichicon F931A106MBA Red LED, SMD1206 package, LiteOn LTST-C150KRKT 8-position pin header, Molex 22-28-4084 2K resistor network, CTS 768141202G 4.7K 5% 0805 resistor, Yageo 9C08052A4701JLHFT 35mm slide pot, 1K, Alpha-Taiwan RA3043-20-10EB1-B13 220 Ohm 5% 0805 resistor, Yageo RC0805JR-07220RL Momentary switch, Panasonic EVQPAD04M 1k ohm 5% 0805 resistor, Yageo 9C08052A1001JLHFT 9 Lattice Semiconductor PAC-POWR1220AT8-EV Evaluation Board Related Literature • ispPAC-POWR1220AT8 Data Sheet • Lattice Application Note AN6067, ispPAC-POWR1220AT8 I2C Hardware Verification Utility Users Guide. Ordering Information Description Ordering Part Number ispPAC Power Manager 1220AT8 Design System China RoHS Environment-Friendly Use Period (EFUP) PAC-SYSPOWR1220AT8 10 Technical Support Assistance Hotline: 1-800-LATTICE (North America) +1-503-268-8001 (Outside North America) e-mail: [email protected] Internet: www.latticesemi.com Revision History Date Version — — March 2007 01.2 Change Summary Previous Lattice releases. Corrected silk screen error in the labeling of the VPS0 and VPS1 connections, located on the left side of the board at the 34 dual row set of interconnect holes. VPS1 is on the left and VPS0 is on the right. Added Ordering Information section. © 2007 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice. 10