* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Radiation-Hard ASICs for Optical Data Transmission in the ATLAS Pixel Detector K.K. Gan

Survey

Document related concepts

Transcript

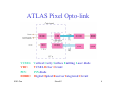

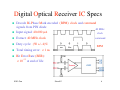

Radiation-Hard ASICs for Optical Data Transmission in the ATLAS Pixel Detector K.K. Gan The Ohio State University Oct 23, 2002 K.E. Arms, K.K. Gan, M. Johnson, H. Kagan, R. Kass, C. Rush, S. Smith, R. Ter-Antonian, M.M. Zoeller The Ohio State University A. Ciliox, M. Holder, M. Ziolkowski Universitaet Siegen, Germany K.K. Gan Siena02 1 Outline l Introduction l Results on IBM 0.25 mm Prototype Chips l Results on Proton Irradiations l Summary K.K. Gan Siena02 2 ATLAS Pixel Detector 3 barrel layers l l l l l l Inner most tracking detector Pixel size: 50 mm x 400 mm ~ 100 million channels 3 disks Barrel layers at r = 5.1, 9.9, 12.3 cm Disks at z = 50, 58, 65 cm Dosage after 10 years: middle barrel layer: 50 Mrad or 1015 1-MeV neq/cm2 optical link: 30 Mrad K.K. Gan Siena02 3 ATLAS Pixel Opto-link VCSEL: Vertical Cavity Surface Emitting Laser diode VDC: VCSEL Driver Circuit PIN: PiN diode DORIC: Digital Optical Receiver Integrated Circuit K.K. Gan Siena02 4 VCSEL Driver Circuit Specs l Convert LVDS input signal into single-ended signal appropriate to drive VCSEL diode l Output (bright) current: 0 to 20 mA, controlled by external voltage l Standing (dim) current: ~ 1 mA to improve switching speed l Rise & fall times: 1 ns nominal (80 MHz signals) l Duty cycle: (50 +/- 4)% l “On” voltage of VCSEL: up to 2.3 V at 20 mA for 2.5 V supply l Constant current consumption! K.K. Gan Siena02 5 Digital Optical Receiver IC Specs l Decode Bi-Phase Mark encoded (BPM) clock and command signals from PIN diode l Input signal: 40-600 mA 40 MHz clock l Extract: 40 MHz clock command l Duty cycle: (50 +/- 4)% l Total timing error: < 1 ns l Bit Error Rate (BER): < 10-11 at end of life K.K. Gan BPM Siena02 6 DORIC Logic l Training period: ~25 ms of 20 MHz clock (BPM with no data) Input transitions ] leading edges Internal delays Delay of Trailing Edges ] trailing edges 40 MHz Recovered Clock Delay Locked Loop: Duty Cycle = 50%? ] Ready for data: BPM Recovered Data 1 0 K.K. Gan 0 0 Recovered 40 MHz Clock 0 0 Siena02 7 VDC & DORIC Design History l Original design for ATLAS SemiConductor Tracker (SCT) q AMS 0.8 mm BiPolar in radiation tolerant process (4 V) l DMILL #1-3: Summer 1999 - May 2001 q 0.8 mm CMOS rad-hard process (3.2 V) q VDC & DORIC #3: meet specs q severe degradation of circuit performance in April 2001 proton irradiation migrate to IBM 0.25 mm (2.5 V) in Summer 2001 a enclosed layout transistors and guard rings for improved radiation hardness a K.K. Gan Siena02 8 VDC & DORIC Designs in 0.25mm l IBM #1-2: June - October 2001 VDC: decouple adjustment of bright & dim currents more constant current consumption DORIC: optimized differential preamp circuit a both circuits meet specs l IBM #3: November 2001 VDC: DORIC: further improvements in current consumption single-ended preamp keeps 10 V PIN bias off chip improved delay control circuit… a single-ended preamp matches prior performance l IBM #4: April 2002 VDC: DORIC: compatible with common cathode VCSEL arrays, 4-channel chip preamp optimized for common anode PIN arrays improved delay control circuit: centers clock at 50% duty cycle reset added for slow and controlled recovery…4-channel chip a improved performance over #3 K.K. Gan Siena02 9 VDC-I4: VCSEL Drive Currents vs Iset 30.0 25.0 IOUT (mA) 20.0 VDC-I2 bright (data) VDC-I2 bright (simulation) VDC-I3 bright (data) VDC-I3 bright (simulation) VDC-I3 dim (data) VDC-I4 bright (data) VDC-I4 bright (simulation) VDC-I4 dim (data) VDC-I5 bright (simulation) I5 I2 I3 I4 15.0 10.0 5.0 0.0 0.0 0.5 1.0 1.5 2.0 Iset (mA) l l l l turning over at high Iset is due to 10 W in series used in measurement dependence of bright current vs Iset is as expected need to increase bright (VDC-I3 reached 20 mA) and dim (1 mA) currents VDC-I5 is predicted to produce more currents K.K. Gan Siena02 10 Duty Cycle vs Iset for 40 MHz Clock 60.0 operating range +Duty Cycle (%) 55.0 50.0 VDC-I2 (data) I2 45.0 VDC-I3 (data) I3 VDC-I3 (simulation) I4 VDC-I4 (data) VDC-I4 (simulation) VDC-I5 (simulation) 40.0 0.0 0.5 1.0 1.5 2.0 Iset (mA) clock duty cycle close to 50% l rise & fall times: 1.0-1.5 ns over operating range ] improve speed of pFETs used to drive common cathode VCSEL l K.K. Gan Siena02 11 PIN Current Thresholds in DORIC-I4 4 Count 3 2 1 0 0 10 20 I l PIN 30 40 (mA) PIN current thresholds for no bit error are low: ~ 15 mA K.K. Gan Siena02 12 Jitter of Recovered Clock in DORIC-I4 2.5 Clock Jitter (ns) 2 I4 DORIC #35 Very Short/Very Fast I4 DORIC #37 Short/Fast I4 DORIC #1 Nominal I4 DORIC #4 Nominal I4 DORIC #39 Nominal I4 DORIC #42 Long/Slow I4 DORIC #43 Very Long/Very Slow 1.5 1 0.5 0 20 40 100 400 600 IPIN (mA) l l jitter is low for low PIN current jitter is large for high PIN current due to kludge used in getting DORIC to work with common cathode PIN K.K. Gan Siena02 13 Period/Duty Cycle of Recovered Clock in DORIC-I4 25.6 I4 DORIC #35 Very Short/Very Fast I4 DORIC #37 Short/Fast I4 DORIC #1 Nominal I4 DORIC #4 Nominal I4 DORIC #39 Nominal I4 DORIC #42 Long/Slow I4 DORIC #43 Very Long/Very Slow 55 25.4 Duty Cycle (%) Period (ns) 60 I4 DORIC #35 Very Short/Very Fast I4 DORIC #37 Short/Fast I4 DORIC #1 Nominal I4 DORIC #4 Nominal I4 DORIC #39 Nominal I4 DORIC #42 Long/Slow I4 DORIC #43 Very Long/Very Slow 25.8 25.2 25.0 50 45 24.8 24.6 20 40 100 400 40 600 20 IPIN (mA) K.K. Gan 40 100 400 600 IPIN (mA) l clock period is close to 25 ns l clock duty cycle is close to 50% Siena02 14 VDC-I4: Clock Duty Cycle vs. Dosage l irradiated opto-electronics with 24 GeV protons at CERN 56 54 link1 Duty Cycle (%) 52 link2 link3 link4 50 link5 link6 48 link7 link8 46 44 0 10 20 30 40 50 60 Dosage (Mrad) l duty cycle increases by ~ 2% after 58 Mrad K.K. Gan Siena02 15 VCSEL Drive Current of Irradiated VDC-I4 18.0 16.0 14.0 VDCI4-4 Pre Irrad (bright) IOUT (mA) 12.0 VDCI4-6 Pre Irrad (bright) VDCI4-7 Pre Irrad (bright) VDCI4-9 Pre Irrad (bright) 10.0 VDCI4-4 post Irrad (bright) VDCI4-6 Post Irrad (bright) 8.0 VDCI4-7 Post Irrad (bright) VDCI4-9 Post Irrad (bright) 6.0 VDCI4-6 Pre Irrad (dim) VDCI4-9 Pre Irrad (dim) VDCI4-4 Post Irrad (dim) 4.0 VDCI4-6 Post Irrad (dim) VDCI4-7 Post Irrad (dim) 2.0 VDCI4-9 Post Irrad (dim) 0.0 0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0 Iset (mA) l no degradation from irradiation l similar result for irradiated VDC-I3 K.K. Gan Siena02 16 Opto-Board for Irradiation Study Opto-pack clock PIN DORIC data VCSEL VDC VCSEL VDC PIN array 4-channel DORIC-I4 VCSEL array K.K. Gan Siena02 4-channel VDC-I4 17 Opto-Board Bit Error Threshold vs. Dosage 30 25 IPIN (mA) 20 Link3 15 Link4 Link5 Link6 10 21.0 Mrad 12 hours 16.9 Mrad 13 hours 9 hours 13.8 Mrad 14 hours 12.2 Mrad 12 hours 8.3 Mrad 15 hours 6.2 Mrad 12 hours 3.1 Mrad Start 0 9 hours 5 Dosage/VCSEL Annealing Time l l K.K. Gan VCSELs annealed with 20 mA during indicated periods bit error thresholds remain constant up to 21 Mrad Siena02 18 Opto-Board Optical Power vs. Dosage 1400 1200 Power (mW) 1000 link6 link3 link4 link5 800 600 400 200 23.4 Mrad link6 12 hours 18.9 Mrad 13 hours 9 hours 15.4 Mrad 14 hours 13.7 Mrad 12 hours 9.2 Mrad 15 hours 6.9 Mrad 12 hours 9 hours 3.4 Mrad Start 0 Dosage/VCSEL Annealing Time l K.K. Gan optical power above ATLAS pixel specs Siena02 19 Summary l VDC-I4 & DORIC-I4 (IBM 0.25 mm) meet ATLAS pixel specs l opto-link passes ATLAS pixel radiation hardness specs ] continue to perform well after 20-58 Mrad! l next submission: Dec. 2002 q improve speed & amplitude of common cathode VDC q implement common cathode preamp in DORIC K.K. Gan Siena02 20