* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Title of Presentation - University of California, Santa Barbara

Waveguide filter wikipedia , lookup

Radio transmitter design wikipedia , lookup

Flexible electronics wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Microwave transmission wikipedia , lookup

Invention of the integrated circuit wikipedia , lookup

Index of electronics articles wikipedia , lookup

Tektronix analog oscilloscopes wikipedia , lookup

Waveguide (electromagnetism) wikipedia , lookup

British telephone socket wikipedia , lookup

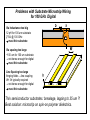

Interconnects in 50-100 GHz Integrated Circuits M.J.W Rodwell, S. Krishnan, M. Urteaga, Z. Griffith, M. Dahlström, Y. Wei, D. Scott, N. Parthasarathy, Y-M Kim, S. Lee University of California, Santa Barbara [email protected] 805-893-8044, 805-893-3262 fax Outline • Introduction • Transmission line characterization for on-wafer device measurements • Monolithic millimeter-wave ICs • Mixed-signal medium-scale ICs High-speed InP Heterojunction Bipolar Transistors Apply scaling approaches of Si-devices with material advantages of III-V systems to realise ultra-fast transistors Previous research: Transferred-substrate HBT technology Current research: Highly scaled mesa-HBT technology Why is the wiring environment important to us? Accurate device measurements require controlled ZO Monolithic Millimeter-wave IC design Ultra-high frequency mixed-signal IC design Transferred-substrate HBTs • Substrate transfer process permits simultaneous scaling of emitter-base and collector-base junction widths • Maximum frequency of oscillation f max f / 8RbbCcb • Record values of measured transistor power gain at 110 GHz, record values of extrapolated fmax (> 1 THz) Vce = 1.2 V Ic=6 mA 25 U Gains, dB • Process provides mirostrip wiring environment with thin (5 mm) low loss BCB dielectric (er= 2.7) 30 20 0.4 mm x 6 mm emitter, 0.7 mm x 9 mm collector, MSG 15 H 10 21 5 0 10 100 Frequency,GHz 1000 Ultra Wideband mesa-HBTs UCSB / IQE Mattias Dahlstrom (UCSB) Amy Liu (IQE) • Highly Carbon-doped InGaAs base enables low base contact resistance, short Ohmic transfer length Lt ~ 0.1 mm • Allows aggressive scaling of basemesa width in traditional mesa-HBT structure • Record fmax (> 400 GHz) for mesa-HBT device 30 25 21 Gain (dB) H , U • Incorporate coplanar waveguide (CPW) or microstrip wiring environment with backend processing 20 15 f =282 GHz t 10 f =480 GHz max 5 0 10 10 10 11 frequency (GHz) 10 12 On-wafer Device Measurements High-frequency Device Measurements • Commercial vector network analyzers available to 350 GHz • UCSB capabilities: DC-50 GHz, 75-110 GHz, 140-220 GHz • Accurate S-parameter measurements require accurate on-wafer calibration • Line-Reflect-Line calibration is preferred for submicron device measurements UCSB 140-220 GHz VNA Measurement Set-up On-wafer Device Measurements • Submicron HBTs have very low Ccb (< 5 fF) 230 mm 230 mm • Characterization requires accurate measure of very small S12 • Standard 12-term VNA calibrations do not correct S12 background error due to probe-to-probe coupling Transistor Embedded in LRL Test Structure Solution Embed transistors in sufficient length of on-wafer transmission line to reduce coupling Line-Reflect-Line calibration to place measurement reference planes at device terminals Corrupted 75-110 GHz measurements due to excessive probe-to-probe coupling Line-Reflect-Line Calibration • LRL does not require accurate characterization of Open or Short calibration standards • LRL does require accurate characterization of transmission line characteristic impedance • LRL does require single-mode propagation environment Transferred-substrate process provides ideal wiring environment for on-wafer device measurements Mesa-HBT technology presents challenges to realizing single-mode environment to 220 GHz Transferred-substrate HBT Measurements • Substrate-transfer provides wellmodeled microstrip wiring environment with thin dielectric (5 mm) • Conductors must be narrow for ZO = 50W : high resisistive losses • LRL calibration is referenced to Line standard ZO • Must correct for complex ZO, particularly at low frequencies R j L ZO G j C S11 S22 freq (6.000GHz to 40.00GHz) Transistor S-parameters with (red) and without (blue) complex ZO correction Mesa-HBT Measurements • CPW wiring is incorporated with minimal backend processing •Must avoid coupling to parasitic modes +V +V +V -V 0V 0V +V S11 0V Microstrip mode Slot mode S22 kz freq (75.00GHz to 110.0GHz) Substrate modes Mesa-HBT measurement corrupted from CPW excitation of parasitic modes in 75-110 GHz band Monolithic mm-Wave ICs Monolithic mm-Wave Integrated Circuits MIMICs have applications in • Point-to-point mm-wave links (60 GHz, 90 GHz…) • Automotive radar (46 GHz, 77 GHz…) • Planetary exploration, atmospheric sensing (140-220 GHz) Transmission line tuning networks require low-loss interconnects with precisely controlled impedance and velocity Transmission Line Options • Microstrip with semiconductor substrate dielectric • Coplanar Waveguide (CPW) • Thin-film dielectric Microstrip Microstrip Wiring with Semiconductor Dielectric Microstrip wiring with semiconductor dielectric is extensively used in MIMICs Requires thinning of substrate thickness to minimize through-wafer via inductance Via inductance 12 pH for 100 mm substrate, j7.5W @ 100 GHz Substrate mode coupling Synchronous coupling into TM0 mode at f S ,TM 0,min 106 h er 1 “Handbook of Microwave Integrated Circuits” R. Hoffman, Artech House, 1987 kz CPW Wiring Frequently used for high frequency MIMIC designs Substrate must still be thinned to avoid coupling to substrate modes, h < 0.12ld . Reference: Riaziat, M. et al. “ Propagation Modes and Dispersion Characteristics of Coplanar Waveguide” IEEE MTT, March 1990 . Through-wafer vias or multiple-wire bonds are necessary in packaged ICs to prevent parallel plate waveguide modes for L > ld /2 L Thin-dielectric Microstrip Wiring Wiring and Ground planes on IC top surface separated by a few microns of thin dielectric Planarising spin-on-polymers offer low dielectric constant, low microwave loss Low ground access inductance, low dispersion, low mode coupling, due to thin substrate thickness … but thin dielectrics result in narrow conductor widths and high resistive losses Ground Plane Low er Via Via S.I. Substrate Cross-section of Transferred-substrate HBT Thin-dielectric Wiring Environment Transferred-substrate Microstrip Wiring Properties • 5 mm BCB substrate er = 2.7 Passive Element Matching Network for Single-stage Amplifier • 50 W line W = 12.5 mm, Loss 1 dB/mm @100 GHz • 4mm x 4mm vias allows dense integration Excellent agreement between measurement and CAD simulations of microstrip matching networks seen to 200 GHz S11 S21 S22 freq (140.0GHz to 220.0GHz) Red- Simulation Blue- Measurement IC Results: 140-220 GHz Small-Signal Amplifiers 8 6 dB 4 2 0 -2 Single-transistor amplifier 6.3 dB gain @ 175 GHz -4 140 150 160 170 180 190 200 210 220 frequency, GHz Cell Dimensions: 0.69mm x 0.35 mm 15 10 dB 5 0 -5 Three-transistor amplifier 8.5 dB gain @ 195 GHz -10 140 150 160 170 180 190 frequency (GHz) 200 210 220 Cell Dimensions: 1.6mm x 0.59 mm IC Results: W-band Power Amplifiers UCSB Yun Wei 20 Common-base PA 10 Psat=16 dBm @ 85 GHz Pout 8 10 6 5 4 0 2 T 15 G , dB P1dB=14.5 dBm Pout, dBm GT GT=8.5 dB Total Emitter Area AE = 128 mm2 -5 0 -15 -10 -5 0 5 10 15 Pin, dBm Cascode PA 15 10 GT GT=8.2 dB Total Emitter Area AE = 64 mm2 8 6 GT, dB P1dB=9.5 dBm Pout 10 Pout, dBm Psat=12.5 dBm @ 90 GHz Cell Dimensions: 0.5mm x 0.4 mm 5 4 0 -5 -15 2 -10 -5 0 Pin, dBm 5 0 10 Cell Dimensions: 0.5mm x 0.4 mm Mixed-Signal ICs High Frequency Mixed-Signal ICs Applications • Long haul fiber optic transmission ICs (40 Gb/s, 80 Gb/s. 160 Gb/s ??) • Digital radio: ADCs, DACs, etc… > 10 Gb/s sampling rates Medium scales of integration (1000-10,000 transistors) Wiring requirements for mixed-signal ICs • Low common-lead ground-return inductance • Controlled characteristic impedance for CAD simulation • Low line-to-line coupling in densely packed ICs • Low eeff for time-delay sensitive circuits Problems with top-side CPW Wiring for 100 GHz Digital CPW for long interconnects only Unknown ZO for most wires CAD modeling difficult Implement circuit design techniques to minimize effects Circuit Cross-talk Densely packed internal wires with large large fringing fields Excitation of surface wave or parallel-plate modes couple circuits CAD modeling difficult Ground Inductance Discontinuous ground planes Wire bonds to package ground ~0.3 pH/mm inductance Signal distortion, Ground Bounce, Ringing Problems with Coplanar Waveguide Packaged ICs Lbond/n Peripheral grounding allows parallel plate mode resonance InP die dimensions must be <0.4mm at 100GHz …or thin wafer and add Vias Csub Bond wire inductance resonates with through-wafer capacitance at 1 o CsubLbond / n Problems with Substrate Microstrip Wiring for 100 GHz Digital Via Inductance too big 12 pH for 100 um substrate j7.5W @ 100 GHz must thin substrate Via spacing too large ~100 um for 100 um substrate not dense enough for digital must thin substrate Line Spacing too large fringing fields line coupling W> 3h typically required not dense enough for digital must thin substrate Thin semiconductor substrates: breakage, lapping to 35 um ?! Best solution: microstrip on spin-on polymer dielectrics. Top-side Thin-dielectric Microstrip Wiring for 100 GHz digital Low via inductance 0.6 pH for 5 mm substrate j0.4W @ 100 GHz Ground Plane Low er Via Via Small Via dimensions 4 mm x 4 mm; dense integration Low line-to-line coupling Dense integration Low eeff, high wave velocity Low time-of flight delays Well-controlled ZO Good for CAD modeling S.I. Substrate Drawbacks • Added process complexity/cost • Capacitive low impedance lines • Lower current carrying capacity with narrow conductors • Substrate and parallel plate modes still present for packaged ICs Packaging Thin-dielectric Microstrip Circuits BCB (5 um thick) plated top-surface ground plane circuits thinned (75 um) semi-insulating InP substrate circuits via < ld /2 via plated back-surface ground plane solder bond package ground Thinned wafer with substrate Vias: Kills ground bounce & substrate modes Wafer lapped & thinned to 75 um Vias to backside ground plane & package ground 200 mm via spacing suppresses all DC-200 GHz substrate resonant modes IC Results: 87 GHz HBT Master-Slave Latch UCSB PK Sundararajan, Zach Griffith Static frequency division to 87 GHz InP /InGaAs/InP mesa-DHBT Technology Wiring Process Flow Two-levels of topside interconnects, NiCr resistors, MIM capacitors Spin 6 mm BCB dielectric Via etch/planarization etchback to 5 mm Patterned Au electroplating of IC ground planes, and probe pads. 87 GHz input, 43.5 GHz output -0.06 -0.08 V out (Volts) -0.1 -0.12 -0.14 -0.16 -0.18 -0.2 22 22.02 22.04 22.06 22.08 time (nsec) 22.1 22.12 22.14 IC photograph before and after plating ground plane IC Results: 8 GHz SD ADC UCSB PK Sundararajan, Zach Griffith Technology InP /InGaAs/InP mesa-DHBT 400 Å base, 2000 Å collector, 9 V BVCEO, 200 GHz ft, 180 GHz fmax 2.5 x 105 A/cm2 operation Thin-dielectric microstrip wiring Design simple 2nd-order gm-C topology comparator is 87 GHz MSS latch integration by capacitive loads 3-stage comparator, RTZ gated DAC 975 kHz FFT bin size 8 GHz clock rate 65.5 MHz signal 64:1 oversampling ratio Results 133 dB (1 Hz) SNR at 74 MHz equivalent to ~8.8 bits at 200 MS/s IC photograph before and after plating ground plane Conclusions High performance III-V devices require high performance wiring environments Accurate on-wafer device measurements require known ZO with single-mode propagation MIMIC designs require well-modeled wiring with low ground access inductance Mixed-signal ICs require high-levels of integration and a low eeff wiring environment Wafer thinning is required to avoid substrate and parallel-plate modes in packaged ICs