* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Lecture03_04

Survey

Document related concepts

Transcript

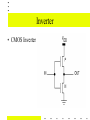

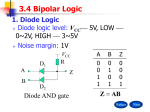

ELE22MIC Lecture 3 • Paul Main’s Office Location has moved to Pysical Sciences 2 Room 107 • Will be available for 2 hours consultation 10am - 12am after Tuesday and Friday Lectures during term time • Revision: • Decimal, Hexadecimal, Binary Arithmetic • Electronic Schematic Symbols & Logic Voltage vs 5V TTL Logic Levels • • • • True = Logic “1” = High Voltage Level False = Logic “0” = Low Voltage Level TTL “High” or “1” is 2.0V to 5V TTL “Low” or “0” is 0V to 0.8V. – Indeterminate Logic Level Between 0.8 & 2.0V – Actual Valid High & Low voltages vary depending on the logic family & power supply voltage Input Voltage vs AVR logic levels Interfacing various logic families 1. • It is possible to connect the AVR outputs directly to DTL, TTL, LS Logic, CMOS, etc providing the generated logic levels fall within the required range for that logic family at that VCC voltage level. • For example If we let VCC=3.3V • 0.2 x VCC = 0.7 V - TTL logic low • 0.6 x VCC = 2V V - TTL logic high Interfacing various logic families 2. • If we let VCC=2.7V • 0.2 x VCC = 0.54V - TTL logic low • 0.6 x VCC = 1.6V - TTL logic indeterminate. Thus at VCC = 2.7V, we cannot use TTL logic! • So in general, look at the “electrical characteristics” in the datasheets to determine potential conflicts. Interfacing various logic families 3. • Similarly, If we let VCC=5V, but we use a 3.3V display (as we will) we note the maximum logic high is VCC+0.5v. • I.e. the maximum allowable input voltage before the internal protection circuits operate is 3.8V. Therefore we need logic level translation ic… 74AHC and 74VHC series chips typically have 5V tollerant inputs, so make good logic level translators. Terminology - Edge transitions • Logic “1” -> Logic “0” = Falling Edge • Logic “0” -> Logic “1” = Rising Edge Inverter • Buffer - Logic state is Maintained • Inverter - Logic state is Inverted - NOT Inverter • CMOS Inverter 2-Input AND Logic Symbol Truth Table for : 2-Input AND Gate Output will be 1, only if all inputs are 1 3-Input AND Logic Symbols Truth Table for : 3-Input AND Gate 2-Input OR Logic Symbol • OR - True of any input is True – 2-Input OR Gate Truth Table 3-Input 0R Logic Symbol • 3-Input OR Gate XOR Logic Symbol • Exclusive OR - True if one input is True Binary Addition (1) • Say for example we want to add two numbers, 5 and 8 . Too easy! • If we first convert these to binary we get 101 and 1000 . • Adding these together we get 1101 . • Converting back to decimal • 1101 =23 + 22 + 0 + 20=8 + 4 + 0 + 1=13 • Simple - We knew that one! (dec) (bin) (dec) (bin) (bin) (bin) (dec) Binary Addition (2) • Say for example we want to add two numbers, 7 and 9 . • If we first convert these to binary we get 111 and 1001 . • Adding these together we get 10000 . • Converting back to decimal • 10000 = 24 = 16 • Hmm! So many ones and zeroes! (dec) (bin) (dec) (bin) (bin) (bin) (dec) Hexadecimal • In Hexadecimal (Hex for short) we use the numbers 0..9 and A..F to represent groups of 4 bits. • A group of four bits is called a nibble, and a group of 8 bits is called a byte. • So any byte can be represented in 2 nibbles, or two hex digits. • For example 11111110 = 254(dec) = FE (hex) (binary) • • Now that’s easier to remember - FE FI FO FUM! And takes less letters than decimal! What interesting words can you make just using four hex digits? Full Adder • Full Adder Truth Table Who invented the base 2 adder? (1) Full Adder (2) • A Full Adder adds two bits, A0 & B0, plus the Carry-In as shown creating a Bit 0 Sum and Carry Out. Carry Out Bit 0 Sum Carry In 8 Bit Adder • 8 Full adders can be cascaded to form an 8-bit ADDer • The AVR assembly language instructions “ADD” and “ADC” configures the ALU to use the logic shown. • Carry in is set to 0 for ADD. • Carry in is set to CF for ADC. Claude Shannon • Interests: Model Planes, Radio Controlled boats, local telegraph, juggling, unicycling, and chess… • Studied Boole’s work on Boolean Algebra • Graduated with degrees in Electrical Engineering and Mathematics. • Utilised and extended boolean algebra to operate on relays • AND Invented the base 2 adder! • He also contributed to cryptography theory! Equivalent Circuits • To make a TTL inverter requires a single NPN transistor, diode and 2 resistors. • To make a simple Diode-Nor gate requires a single transistor, 2 diodes and 3 resistors. • It is possible to create AND gates using NOR gates and Inverters. (deMorgans theorum) • Example Inverting the inputs to a NAND gate -> OR gate. • Work Example - OR, AND, MUX, Latch Memory Elements: 1 Bit Latch • Latches can be created using NAND Gates Registers • A register can be created using an array of latches with their gates connected together.. • The lower nibble of R01 R01.0..R01.3 can be created using the latches as shown here. 68HC11 Register Set 68HC11 CPU • Contains – Registers – Execution Unit – ALU & Condition Codes Register AVR Core Architecture AVR Register Set (1) • The AVR contains 32 General Purpose working registers. • The ALU supports 8 & 16 bit operations. AVR Register Set (2) AVR Register Set (3) • The AVR contains 32 General Purpose working registers. • Most instructions have full access to all the registers for 8 or 16 bit operations. • The X, Y and Z registers have a special function. They can be set to index anywhere in memory, including any register as they are also mapped into memory. • I.e. X, Y and Z they can be used as pointers. AVR Register Set (4) AVR Status Register • • • Bit#7 - Interrupt - Cleared on interrupt 6 - T - biT for Bit Load & Store instructions 5 - H - Half Carry • • • • • 4 - S - Sign 3 - V - oVerflow 2 - N - Negative 1 - Z - Zero 0 - C - Carry • From Pages 9 & 10 of ATMEGA128 manual Condition Codes Register: ZERO FLAG