* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Topic: High Performance Data Acquisition Systems Analog

Time-to-digital converter wikipedia , lookup

Buck converter wikipedia , lookup

PID controller wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Control system wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Quantization (signal processing) wikipedia , lookup

Oscilloscope types wikipedia , lookup

Oscilloscope history wikipedia , lookup

Rectiverter wikipedia , lookup

Integrating ADC wikipedia , lookup

Opto-isolator wikipedia , lookup

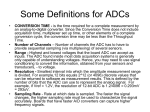

Topic: High Performance Data Acquisition Systems Analog Components: Analog to Digital Convertors Figure 1 Generic High Performance Analog to Digital Convertor Figure 1 shows a simplified block diagram of a high performance analog to digital convertor. As previously discussed, the analog to digital convertor is usually the most complex device within a data acquisition system and often times sets the limits on the overall accuracy of the system. Therefore, proper selection and characterization of the ADC will be crucial in achieving a robust system design that will operate within the desired limits of the system error budget. Again, once you have selected your ADC for the system, usually all other components are then designed and selected to perform better than the limits set by the ADC. This is fundamentally why understanding the performance of the ADC goes a long way in designing the rest of the system. Let’s take a look at some basic errors that are inherent within all ADC’s. Figure 2 Transfer Function of an Ideal 3-Bit Quantizer As we went over last week, the ideal transfer function of an ADC is shown is Figure 2. As shown in the diagram, there are 2n-1 decision points (or threshold levels) in the transfer function (where n equals the bit resolution of the ADC). The analog decision point voltage should be precisely halfway between the code word center points and therefore a staircase function becomes the best case approximation to a straight line drawn through the origin and the full scale point. If the ADC input is moved through its entire range of analog values and the difference between the output and input is taken, a sawtooth error function is the result (that is also shown in Figure 2). This is the irreducible error that results from the conversion process and it can only be reduced by increasing the resolution of the ADC (choosing an ADC with higher bit resolution). Ideally speaking, the ADC output can be thought of as simply the analog input with the sawtooth waveform (quantization noise) added to it. An ADC is usually/ideally a unity gain device (the quantized encoded digital output tracks the analog input) but of course the reality of real error sources within the ADC become the most dominant performance limiters. Figure 3 ADC Transfer Function Errors Real ADC’s do not have the ideal transfer function that is shown in Figure 2. There are four basic departures from the ideal transfer function: offset, gain, linearity, and noise errors. These errors are all present at the same time in the convertor; in addition, they also change with both time and temperature. Figure 3 shows ADC transfer functions which illustrate 3 of the 4 error types (offset, gain, and linearity). Figure 3a shows offset error which is the analog error by which the transfer function fails to pass through zero. Of course, fundamentally in a data acquisition system, cumulative offset errors within the system will give a false reading when the system actually has no signal to acquire. This error is easily accounted for and calibrated out within the system either digitally (but running a calibration cycle and capturing the system offset error and subtracting it from subsequent measurements) or by using analog means using a “servo-loop” technique by reconverting the cumulative digital offset error through a digital to analog convertor and using the analog voltage applied to various ports in the system to subtract out the offset error. Either way, the offset error must be accounted for and removed in the system because time and temperature will also cause the offset to vary significantly. Also shown in Figure 3b is the gain error. This is the difference in slope between the actual transfer function and the ideal, expressed as a percent of analog magnitude. Remember, most specifications for an ADC can be thought of as “referred to the input of the device.” For instance, in regards to offset voltage, when a perfectly mid-scale analog voltage is applied to an ADC, the output code will include the offset of the ADC and not reflect a mid-scale code as it would in an ideal case. But what works better for overall understanding and system error budget management, is to know what the referred input voltage to the ADC that is required to force the ADC output code to mid-scale. This is also true for computing gain error. It is best to know the percentage difference between the actual and ideal voltage to force the ADC to output a full-scale output code. Gain error within a system, can also be calibrated out digitally (with a calibration cycle and digital multiplication in post processing the ADC output data), but when digital multiplication is not advantageous within the system, again, a reconverted analog gain error signal can usually be summed with the reference voltage of the ADC and the gain error can be subsequently calibrated out in real time. Figure 3c also shows a third error, which is much more difficult to manage, called linearity error or non-linearity. This is defined as the maximum deviation of the actual transfer function from the ideal straight line at ANY point along the function. It is usually expressed as a percent of full scale or in LSB (least significant bit) size, such as +/- ½ LSB, and it assumes that offset and gain errors have been calibrated out and adjusted to zero. While offset and gain errors are generally easily removed from the system through calibration, linearity on the other hand is not usually calibrated out and is usually a limiting factor in overall system performance (in regards to overall system level distortion). When the non-linearity of the ADC output signal is measured to be inversely symmetrical on either side of the output waveform (such as an “S” shape), the distortion is usually measured as “odd harmonics.” Correspondingly, asymmetrical non-linearity yields even order harmonics. In this case linearity of the output waveform would produce more of a “bow” overlaid on what would be an error free straight line. Finally, the fourth error is noise. This is manifest in every aspect of the ADC (the voltage reference, analog signal conditioning, and sampling due to aperture uncertainty (which also includes jitter both in the sample and hold switch and the clock generator). This is another error that also sets the performance limits of the data acquisition system. It is also not realizable to be calibrated out and fundamentally it simply increases the amplitude of the sawtooth waveform shown in Figure 2. Again, when designing a high performance (and high frequency) data acquisition system, the analog to digital convertor should be the ultimate limiting factor in overall system resolution, accuracy, and noise. For instance, selecting resolution instantly defines the SNR of the system. Also, the linearity of the ADC will fundamentally set the overall precision of the system. Keep in mind, choosing the proper ADC, and correlating it’s specifications to the key results that you desire the system to perform, will then set the limit of most of your system level performance parameters. Kai ge from CADEKA