* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download High efficiency and low electromagnetic interference boost DC–DC

Three-phase electric power wikipedia , lookup

Electric power system wikipedia , lookup

Mercury-arc valve wikipedia , lookup

Stray voltage wikipedia , lookup

Electrical ballast wikipedia , lookup

History of electric power transmission wikipedia , lookup

Power inverter wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Voltage optimisation wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Power engineering wikipedia , lookup

Two-port network wikipedia , lookup

Circuit breaker wikipedia , lookup

Regenerative circuit wikipedia , lookup

Current source wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Surge protector wikipedia , lookup

Integrating ADC wikipedia , lookup

Electrical substation wikipedia , lookup

Distribution management system wikipedia , lookup

Mains electricity wikipedia , lookup

Alternating current wikipedia , lookup

Opto-isolator wikipedia , lookup

HVDC converter wikipedia , lookup

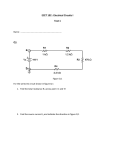

Vol. 35, No. 4 Journal of Semiconductors April 2014 High efficiency and low electromagnetic interference boost DC–DC converter Li Yajun(李亚军)1; , Lai Xinquan(来新泉)1 , Ye Qiang(叶强)2 , and Yuan Bing(袁冰)2 1 Institute 2 Key of Electronic CAD, Xidian University, Xi’an 710071, China Laboratory of High-Speed Circuit Design and EMC, Ministry of Education, Xidian University, Xi’an 710071, China Abstract: A synchronous boost DC–DC converter with an adaptive dead time control (DTC) circuit and antiringing circuit is presented. The DTC circuit is used to provide adjustable dead time and zero inductor current detection for power transistors and therefore, a high efficiency is achieved by minimizing power losses, such as the shoot-through current loss, the body diode conduction loss, the charge-sharing loss and the reverse inductor current loss. Simultaneously, a novel anti-ringing circuit controlled by the switching sequence of power transistors is developed to suppress the ringing when the converter enters the discontinuous conduction mode (DCM) for low electromagnetic interference (EMI) and additional power savings. The proposed converter has been fabricated in a 0.6 m CDMOS technology. Simulation and experimental results show that the power efficiency of the boost converter is above 81% under different load currents from 10 to 250 mA and a peak efficiency of 90% is achieved at about 100 mA. Moreover, the ringing is easily suppressed by the anti-ringing circuit and therefore the EMI noise is attenuated. Key words: DC–DC; dead time; discontinuous conduction mode; electromagnetic interference; anti-ringing DOI: 10.1088/1674-4926/35/4/045002 EEACC: 2570 1. Introduction The boost DC–DC converter, which is able to deliver a high output voltage with a very low power supplyŒ1 3 , is widely used for mobile applications owing to its favorable characteristics, such as high efficiency, low quiescent current, small size, wide range of input voltage and excellent driving capacityŒ4 7 . However, the DC–DC converter operates in switch mode, especially when the converter works in discontinuous conduction mode (DCM), ringing occurs. On one hand, ringing lowers the power efficiency; on the other hand, ringing causes large switching noise and serious electromagnetic interference (EMI). EMI noise may be radiated in free space and damage the radio frequency (RF) circuits. Now, some passive and active EMI filtering methodsŒ8; 9 are presented to attenuate the EMI noise, but those techniques increase the size and the cost of a printed circuit board (PCB), which is not suitable for portable applications. In Ref. [10], a time varying resistor network, which is connected between the switching node and the power supply of the DC–DC converter, is proposed to solve this problem. Unfortunately, the time varying resistor network should be carefully designed to achieve its best function, which requires a complicated control circuit and the die size will be increased. Meanwhile, the light load efficiency is decreased when this method is used. In this paper, a novel boost DC–DC converter with an adaptive dead time control circuit and anti-ringing circuit is presented. By this technique, the EMI noise is effectively suppressed and high power efficiency is achieved. Section 2 describes the formation of ringing when boost DC–DC converter operates in DCM. Section 3 analyzes the working principle of the proposed boost converter thoroughly. The experimental results are presented in Section 4 and the conclusions are given in Section 5. 2. Ringing formation Figure 1 shows the schematic of a conventional synchronous boost DC–DC converter: VIN represents the power supply and VO is the output; L is an energy transferring inductor; CO is an output filtering capacitor; RL is the load resistor; CX is the parasitic capacitor at node VLX ; and IL stands for the current through the inductor L. Normally, to achieve low onresistance and high efficiency, the power switches MN and MP are always very large, so CX cannot be ignored. There are three main stages when the boost converter works in DCM. Figure 2 illustrates the timing diagram and equivalent circuits. During stage 1 (t0 < t < t1 /, MN is on and MP is off. VLX and CX are shorted to ground. IL ramps up at a slope of VIN =L from zero and the energy stored in inductor L also increases. Fig. 1. Schematic of a conventional synchronous boost DC–DC converter. * Project supported by the National Natural Science Foundation of China (No. 61106026) and the Fundamental Research Funds for the Central Universities of China (No. K50511020028). † Corresponding author. Email: [email protected] Received 27 July 2013, revised manuscript received 9 November 2013 © 2014 Chinese Institute of Electronics 045002-1 J. Semicond. 2014, 35(4) Li Yajun et al. Fig. 2. (a) Timing diagram. (b) Equivalent circuits. During stage 2 (t1 < t < t2 /, MN is off and MP is on. VLX is equal to VO and CX is paralleled with output capacitor CO . IL ramps down at a slope of (VIN – VO /=L and flows into the output VO . The energy stored in inductor L depletes gradually. At the end of this stage, IL decreases to zero. During stage 3 (t2 < t < t3 /, both MN and MP are off. Inductor L and parasitic capacitor CX form a resonant tank. Ringing will appear at the VLX node, causing large EMI in the system. In this stage, the following equations can be obtained: IL .t/ D CX VIN dVLX .t/ ; dt VLX .t/ D L dIL .t/ : dt (1) (2) 3. Proposed Boost DC–DC converter 3.1. Architecture d2 VLX .t / 1 1 C VLX .t/ D VIN : 2 dt LCX LCX (3) Moreover VLX .t2 / D VO ; (4) 1 IL .t2 / D 0: CX (5) From Eqs. (3)–(5), the resonant voltage at node VLX can be given by VLX .t/ D VIN C .VO VIN / cos !0 .t t2 / ; t 2 6 t 6 t3 ; (6) and the resonant current can be derived as IL .t/ D VIN VO sin !0 .t !0 L where !0 is calculated by t2 / ; (8) Today and in the future, small-value off-chip inductorsŒ11; 12 or even on-chip inductorsŒ13 are and will be widely used for portable applications to achieve small size and low cost. Thus, the oscillation frequency at the VLX node gets higher and higher. Large ringing and EMI noise may seriously affect RF circuits and decrease the power efficiency. In addition, the resonant current sinks and sources current from VIN repeatedly, which therefore results in poor stability of the power supply. According to Eqs. (1) and (2), we can get 0 VLX .t2 / D 1 !0 D p : LCX t 2 6 t 6 t3 ; (7) In order to suppress the ringing and improve the power efficiency, as shown in Fig. 3(a), a novel boost converter with a dead time control (DTC) circuit and an anti-ringing circuit is proposed. D is the body diode of the P-channel metal-oxide semiconductor (PMOS) switch MP. The substrate of the MP should be connected to the highest voltage of the boost converter VO and the substrate of the N-channel metal-oxide semiconductor (NMOS) switch MN should be tied to the ground to make sure the normal operation of DC–DC converter. A compensation blockŒ14 18 ensures the stability of the converter and the pulse width modulator (PWM) module provides the duty cycle. The soft-start signal VSTART minimizes the inrush current and the output overshoot during normal startup. Timing diagram of the proposed converter is shown in Fig. 3(b), which is different from the timing diagram of a conventional converter shown in Fig. 2(a) in two aspects. (1) Dead time, during which the power transistors MP and MN are both off, is added to reduce shoot-through current loss, body diode conduction loss and charge-sharing loss; the DTC circuit provides an optimal dead time. Moreover, the DTC cir- 045002-2 J. Semicond. 2014, 35(4) Li Yajun et al. Fig. 3. (a) Architecture. (b) Theoretical waveforms. Fig. 4. (a) Body diode conduction loss. (b) Charge-sharing loss. cuit can avoid the reverse inductor current from lowering the power efficiency when the inductor current reaches zero. (2) During stage 3, ringing is eliminated by the anti-ringing circuit based on the switching sequence of power transistors. Therefore, low EMI and high efficiency can be achieved. 3.2. DTC circuit The power switches MN and MP always have very low onresistances for the purpose of obtaining high efficiency, so MN and MP should not conduct at the same time to avoid a large shoot-through current that greatly degrades the efficiency and causes large glitches in the inductor current and output voltage. To solve this problem, a dead time between stages 1 and 2 is needed. During the dead time, both MN and MP are off. Inductor current IL charges the parasitic capacitor CX and VLX goes up from zero. It should be noted that the optimal dead time TOPT is related to the load condition and should satisfy the equation as follows: TOPT D VO CX ; IPEAK (9) where IPEAK is the peak inductor current, which is proportional to the load current and thus TOPT is finally determined by the load current when VO and CX are given. If the dead time is fixed as T and T is designed according to the medium load of the converter, extra power losses caused by the charge-sharing and the body diode conduction will be introduced, which can easily be understood as follows. (1) Body diode conduction loss. As shown in Fig. 4(a), assuming the load current is very large and hence the fixed dead time T is much longer than the optimal dead time TOPT , the body diode D will conduct and VLX will be clamped to VO C VD (forward voltage drop of diode D). Since the voltage drop across the body diode is much higher than that across the power switch MP, conversion efficiency is decreased due to the body diode conduction loss. 045002-3 J. Semicond. 2014, 35(4) Li Yajun et al. Fig. 5. Schematic of the proposed DTC circuit. (2) Charge-sharing loss. As shown in Fig. 4(b), if the load current is very small and hence T is much shorter than TOPT , MP will be turned on before VLX reaches VO . Energy stored in the output capacitor CO will charge CX until VLX goes up to VO . That is to say, the energy stored in CO for the load is depleted because of the charge-sharing loss. As a result, a dynamic dead time optimization is required. In this design, a DTC circuit that can provide an adaptive dead time is presented. Compared with dead time optimization methodsŒ19; 20 that need complex algorithms to find out the optimal dead time, the proposed DTC circuit can easily adjust the dead time depending on the load current with a very compact structure. As shown in Fig. 5, the DTC circuit is composed of transistors M1–M9, a driver and a constant current source IB . The sources of M2 and M5 are connected to the node VLX while the sources of M1, M3 and M4 are connected to VO . The aspect ratios of M1–M9 are designed as follows: W W D K1 ; (10) L M2; 3 L M1 W W D ; (11) L M4 L M5 W W D K2 ; (12) L M6; 9 L M7; 8 where K1 > 1 and K2 > 1. Figure 6 shows the simulation results of the proposed DTC circuit. As mentioned before, at the end of stage 1, MN is turned off immediately and VLX goes up from zero. Once VLX > VO , current I2 goes larger than current I3 because source-to-gate voltage of M2 is higher than that of M3. Since I6 D K2 I2 and I5 D K2 I3 , I6 > I5 . Moreover, I5 > I4 , I6 is thus much larger than I4 and the voltage at node VA drops to zero rapidly, as shown in Fig. 6(a). MP will be turned on and then stage 2 starts. Therefore, adaptive dead time control is achieved. On the contrary, at the end of stage 2, if a reverse inductor current happens, VLX < VO and the VA node voltage pulls up to high Fig. 6. Simulation results of the proposed DTC circuit. Table 1. State transition table of the proposed DTD circuit. Stage VN VP Q VC MN MP MS Stage 1 1 1 1 1 ON OFF OFF Dead time 0 1 1 1 OFF OFF OFF (T ) Stage 2 0 0 0 1 OFF ON OFF Stage 3 0 1 0 0 OFF OFF ON quickly, as shown in Fig. 6(b). MP is turned off and then stage 3 begins, which prevents the reverse inductor current loss from lowering the power efficiency. 3.3. Anti-ringing circuit From Fig. 2(a), ringing occurs during stage 3, causing large EMI. To overcome this drawback, a novel anti-ringing circuit is developed. As shown in Fig. 7, the circuit consists of two level shifters, a PMOS switch MS, a buffer and a dead time detection (DTD) circuit. The substrate of MS is biased by VO . When both MN and MP are off in stage 3, MS is turned on. The oscillation loop is broken by shorting the inductor L and hence ringing is effectively suppressed. The difficulty of designing the anti-ringing circuit is to generate a proper drive signal to make sure MS is turned on only in stage 3 without affecting the operation of the converter in other stages. It is obvious that both MN and MP are also off during the dead time. If control signal VC1 is decided only by the states of MN and MP, MS will conduct in dead time and the energy stored in inductor L will be wasted by the onresistance of MS instead of transferring to VO , which results in large power loss. To overcome this problem, a DTD circuit is used. From Fig. 7, output signal VC of the DTD circuit is related to the state of Q besides the states of MN and MP. VC is first converted by the level shifter and then buffered to get VC1 to control MS. Table 1 shows the state transition table of the proposed DTD circuit. It can be seen from the table that though 045002-4 J. Semicond. 2014, 35(4) Li Yajun et al. Fig. 7. Schematic of the proposed anti-ringing circuit. Fig. 8. Simulation results of the proposed anti-ringing circuit. Fig. 9. Level shifter. Fig. 10. Simulation results. (a) A boost converter without anti-ringing circuit. (b) Proposed boost converter with anti-ringing circuit. both MN and MP have the same states in stage 3 and dead time, the state of Q is different and therefore MS is switched on only in stage 3. Furthermore, the proposed DTD circuit is very compact and nearly has no time delay. Figure 8 shows the simulation results of the proposed anti-ringing circuit. From the results, during the operation period T , drive signal VC is low only in stage 3, which agrees with the theory analysis above. It should be noted that drive signals VC1 and VP should be powered by VO , which is the highest voltage of the converter. However, VN and the DTD circuit are powered by VIN , so a level shifter is needed to achieve the conversion of different voltage levels. The schematic and timing diagram are shown in Fig. 9. A boost converter with the proposed anti-ringing circuit is simulated and the simulation is conducted with the following typical application condition: VIN D 3.3 V, VO D 4.6 V, L D 1.5 H, CO D 4.7 F, clock frequency fS D 1.6 MHz and temperature TA D 25 ıC. A high switching frequency ensures a small-value off-chip inductor can be used. In order to verify the advantages of the proposed boost converter, simula- 045002-5 J. Semicond. 2014, 35(4) Li Yajun et al. Table 2. Component values and output voltage. Name Value Name Value VIN 3.3 V L 1.5 H VO 4.6 V CO 4.7 F CIN 4.7 F RFB1 422 k CREF 1 F RFB2 150 k Fig. 11. Micrograph of the proposed boost DC–DC converter. Fig. 12. Test circuit of the proposed boost DC–DC converter. tion of a boost converter without an anti-ringing circuit is also performed and the results are shown in Fig. 10(a). From the results, ringing occurs when the converter operates in DCM. Figure 10(b) shows the results of the proposed boost DC–DC converter and that the ringing is effectively suppressed with the developed anti-ringing circuit. Fig. 13. Experimental results. VIN D 3.3 V, VO D 4.6 V, IO D 250 mA. 4. Experimental results The designed boost DC–DC converter with both the proposed DTC circuit and the proposed anti-ringing circuit has been fabricated using the 0.6 m CDMOS process. Figure 11 shows the micrograph of the proposed converter and the die size is about 2.2 1.5 mm2 . The total area of the DTC circuit and anti-ringing circuit is only 0.03 mm2 , which is less than 1% of the die size. The converter is able to provide a maximum load current of 250 mA at an input voltage ranging from 2.5 to 4.5 V. The output voltage can be externally set from 4 to 8 V with a resistor divider. Digital soft-start, cycle-by-cycle current limit and thermal shutdown are also integrated in this circuit in order to improve the reliability of the boost converter. The test circuit of the proposed boost DC–DC converter is shown in Fig. 12. The component values and output voltage are shown in Table 2. Figure 13 presents the experimental results of the proposed boost DC–DC converter under the condition of VIN D 3.3 V, VO D 4.6 V and IO D 250 mA (maximum load). The converter works in continuous conduction mode (CCM) and the output Fig. 14. Experimental results. VIN D 3.3 V, VO D 4.6 V, IO D 30 mA. voltage ripple is only 35 mV. Figure 14 presents the experimental results of the proposed boost DC–DC converter under the condition of VIN D 3.3 V, VO D 4.6 V and IO D 30 mA. The converter works in discontinu- 045002-6 J. Semicond. 2014, 35(4) Li Yajun et al. Fig. 15. Experimental results. (a) Reference voltage. (b) Line regulation. (c) Load regulation. (d) Measured efficiency. ous conduction mode (DCM) and the ringing appeared at node VLX when both MN and MP are off has effectively been suppressed. The measured waveforms agree with the simulation results and theory analysis perfectly. Furthermore, by carefully designing the DTC circuit, the on time of body diode is only about 15 ns and the duration of reverse inductor current is only about 50 ns owing to the inherent propagation delay in the DTC circuit and power transistors. Figure 15(a) shows the reference voltage of the proposed boost converter under the condition of VIN D 3.3 V, VO D 4.6 V, IO D 0 mA and TA D 40 to 125 ıC. The variation of the reference voltage is only 2.6 mV under a wide range of temperatures. Figure 15(b) shows the line regulation of the proposed boost converter under the condition of VIN D 2.5–4.5 V, VO D 4.6 V, IO D 5 mA and TA D 25 ıC. The variation of the output voltage is only 1 mV and the line regulation is less than 0.03% under a wide range of input voltages. Figure 15(c) shows the load regulation of the proposed boost converter under the condition of VIN D 3.3 V, VO D 4.6 V, IO D 0–250 mA and TA D 25 ıC. The variation of the output voltage is only 12 mV and the load regulation is less than 0.3% under a wide range of load currents. Figure 15(d) shows the power efficiency of the proposed boost converter under the condition of VIN D 3.3 V, VO D 4.6 V, IO D 10–250 mA and TA D 25 ıC. By using the internal synchronous rectification, a maximum power efficiency of 90% is obtained at about 100 mA load current. Also, by Table 3. Performance comparison summary of the chips. Parameter EUP2512 This work Input voltage range (V) 2.5–4.5 2.5–4.5 Output voltage (V) 4–8 4–8 Maximum output current (mA) 250 250 Peak current limit (A) 1.2 1.5 Inductor L (H) 4.7 1.5 Capacitor CO (F) 4.7 4.7 Turn-on resistance of MP (/ 0.6 0.6 Turn-on resistance of MN (/ 0.5 0.5 Switching frequency (MHz) 1.4 1.6 Line regulation @ 40 to 85 ıC (%) 0.5 < 0.3 Load regulation @ 40 to 85 ıC (%) 1 < 0.5 Power efficiency @ 10 mA, VIN D 67 81 3.3 V, VO D 4.6 V (%) Power efficiency (peak) @ VIN D 83 90 3.3 V, VO D 4.6 V (%) improving the switching timing of power transistors with the proposed DTC circuit and anti-ringing circuit, the power efficiency of the boost converter is above 81% under different load currents from 10 to 250 mA. Table 3 shows the performance comparison of the proposed boost DC–DC converter and the EUP2512 under room temperature. From the comparison results, high efficiency is achieved by using the proposed technique. 045002-7 J. Semicond. 2014, 35(4) Li Yajun et al. 5. Conclusions In this paper, a synchronous boost DC–DC converter with proposed DTC circuit and anti-ringing circuit is analyzed and successfully achieved. The DTC circuit provides adaptive dead time control and zero inductor current detection, thus helping in improving the power efficiency by minimizing the shoot-through current loss, the body diode conduction loss, the charge-sharing loss and the reverse inductor current loss. Additionally, the proposed anti-ringing circuit with a DTD cell not only attenuates the EMI noise but also further enhances the power efficiency by suppressing the ringing when the boost converter works in DCM. Experimental results show that the designed boost DC–DC converter achieves high efficiency and low EMI and that it is suitable for portable devices. References [1] Ye Qiang, Lai Xinquan, Li Yanming, et al. A piecewise linear slope compensation circuit for DC–DC converters. Journal of Semiconductors, 2008, 29(2): 281 [2] Chen Fuji, Lai Xinquan, Li Yushan. Design and implementation of an adaptive slope compensation circuit. Journal of Semiconductors, 2008, 29(3): 593 [3] Chen Fuji, Lai Xinquan, Li Yushan, et al. Design of a low input voltage startup circuit for the boost DC–DC converter. Journal of Xidian University, 2010, 37(3): 476 [4] Lai Xinquan, Zeng Huali, Ye Qiang, et al. Design of high efficiency dual-mode buck DC–DC converter. Journal of Semiconductors, 2010, 31(11): 115005 [5] Yuan Bing, Lai Xinquan, Li Yanming, et al. High efficiency realization of a DC–DC converter at light loads for portable applications. Journal of Semiconductors, 2008, 29(6): 1198 [6] Li Yanming, Lai Xinquan, Yuan Bing, et al. An on-chip soft-start circuit for DC–DC switching regulators. Journal of Semiconductors, 2008, 29(6): 1210 [7] Liu Y X, Liu S B, Li Y M, et al. Design and implementation of a compact frequency synchronisation control circuit using enable input for DC–DC converter. IET Power Electron, 2012, 5(9): 1827 [8] Hamza D, Sawan M, Jain P K. Suppression of common-mode input electromagnetic interference noise in DC–DC converters using the active filtering method. IET Power Electron, 2011, 4(7): 776 [9] Chen Wenjie, Yang Xu, Wang Zhaoan. An active EMI filtering technique for improving passive filter low-frequency performance. IEEE Trans EMC, 2006, 48(1): 172 [10] Wang Hongyi, Lai Xinquan, Li Yushan, et al. A novel antiringing circuit for buck DC–DC chip. Acta Electronica Sinica, 2006, 34(2): 361 [11] Wang N, O’Donnell T, Meere R, et al. Thin-film-integrated power inductor on Si and its performance in an 8-MHz buck converter. IEEE Trans Magn, 2008, 44(11): 4096 [12] Du M, Lee H, Liu J. A 5-MHz 91% peak-power-efficiency buck regulator with auto-selectable peak- and valley-current control. IEEE J Solid-State Circuits, 2011, 46(8): 1928 [13] Wibben J, Harjani R. A high-efficiency DC–DC converter using 2 nH integrated inductors. IEEE J Solid-State Circuits, 2008, 43(4): 844 [14] Ye Qiang, Liu Jie, Yuan Bing, et al. On-chip frequency compensation with a dual signal path operational transconductance amplifier for a voltage mode control DC/DC converter. Journal of Semiconductors, 2012, 33(4): 045006 [15] Lai Xinquan, Li Zuhe, Yuan Bing, et al. Control of chaos in double-loop current-mode DC/DC based on adaptive slope compensation. Acta Physica Sinica, 2010, 59(4): 2256 [16] Yuan Bing, Lai Xinquan, Ye Qiang, et al. An integrated currentsensing circuit for current-mode DC–DC buck converters. Journal of Semiconductors, 2008, 29(8): 1627 [17] Yuan Bing, Lai Xinquan, Jia Xinzhang, et al. Implementation of high stability with on-chip frequency compensation in a current mode DC–DC converter. Journal of Xidian University, 2008, 35(4): 685 [18] Lee C F, Mok P K T. A monolithic current-mode CMOS DC–DC converter with on-chip current-sensing technique. IEEE J SolidState Circuits, 2004, 39(1): 3 [19] Yousefzadeh V, Maksimovi D. Sensorless optimization of dead times in DC–DC converters with synchronous rectifiers. IEEE Trans Power Electron, 2006, 21(4): 994 [20] Reiter T, Polenov D, Pröbstle H, et al. PWM dead time optimization method for automotive multiphase DC/DC-converters. IEEE Trans Power Electron, 2010, 25(6): 1604 045002-8