* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download TIDU628 - Texas Instruments

Transistor–transistor logic wikipedia , lookup

Electric battery wikipedia , lookup

Schmitt trigger wikipedia , lookup

Operational amplifier wikipedia , lookup

Integrating ADC wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Current source wikipedia , lookup

Voltage regulator wikipedia , lookup

Rechargeable battery wikipedia , lookup

Power MOSFET wikipedia , lookup

Surge protector wikipedia , lookup

Power electronics wikipedia , lookup

Opto-isolator wikipedia , lookup

Current mirror wikipedia , lookup

Advanced Low Power Reference Design

Florian Feckl

Low Power DC/DC, ALPS

Energy Buffering for

Long-Life Battery Applications

Reference Guide & Test Report

CIRCUIT DESCRIPTION

Long Life Batteries like LiSOCl2 chemistry in a bobbin type cell construction have a very

high Specific energy (Wh/kg) but are unable to provide currents higher than e.g. 20mA.

They furthermore suffer with reduced operation runtimes when higher currents are

drawn.

This application concept shows a proven reference design for a combination of

TPS62740 and a Super-Capacitor powered by a long life primary cell.

In this Reference Design, the Ultra-Low Quiescent Current Buck Converter TPS62740

charges a Supercapacitor to buffer energy for load peaks.

BENEFITS

•

•

•

•

•

Peak Power Assistance

Energy Buffering

Longer Battery Runtime

>15 Years operating Runtime

Efficient Super Capacitor Charging

APPLICATIONS

•

•

•

Wireless Sensor Nodes

Smart Flow Meter

Heat Cost Allocator

LINKS

TPS62740 Product Page

TPS62740 Evaluation Module

Energy Buffering Application Note

Step control (MCU),

timing

VSEL

e.g. 3mA max

TPS62740

Voltage Stepping

Advanced Low Power Solutions

Page 1/16

Test Report

PMP9753

TABLE OF CONTENTS

1

Introduction ......................................................................................................... 3

2

Reference Design Description ........................................................................... 4

3

4

2.1

Detailed Block Diagram ................................................................................ 6

2.2

Wireless Metering-Bus Circuit Definition .................................................... 7

2.3

Schematic ..................................................................................................... 8

Measurement Results ......................................................................................... 9

3.1

Start-up behavior .......................................................................................... 9

3.2

Recharge Sequence Results ...................................................................... 11

3.3

Recharge Conversion Efficiency Results ................................................. 13

Summary ........................................................................................................... 16

LIST OF FIGURES

Figure 1: typ. discharge curve of a TADIRAN SL-360 over several loads ..................... 3

Figure 2: Simplified charging block diagram .................................................................. 4

Figure 3: Recharge Cycle Sequencing .......................................................................... 5

Figure 4: Reference design block diagram .................................................................... 6

Figure 5: PMP9753 schematic ...................................................................................... 8

Figure 6: Start-up circuit configuration .......................................................................... 9

Figure 7: Battery current and capacitor voltage during pre-charge .............................. 10

Figure 8: Diagram of the measurement setup ............................................................. 11

Figure 9: Charging waveforms .................................................................................... 12

Figure 10: Conversion efficiency ................................................................................. 13

Figure 11:TPS62740: Efficiency vs. output current ..................................................... 14

Figure 12: Energy conversion efficiency measurement setup ..................................... 14

Figure 13: Overall charging power losses ................................................................... 15

Figure 14: Energy conversion efficiency...................................................................... 15

Advanced Low Power Solutions

Page 2 of 16

Test Report

PMP9753

1 Introduction

Battery chemistries like the LiSOCl2 type offer great benefits in terms of application

runtime. They bring operation runtimes of 15 years and more to reality.

The technology, however, has a limited characteristic in terms of supporting higher

loads.

Higher load pulses cannot be supported by the battery itself due to the internal

impedance. As well, the higher the drawn current, the shorter the battery operation.

Figure 1 shows, how different battery currents translates to different battery runtimes.

Figure 1: typ. discharge curve of a TADIRAN SL-360 over several loads

1

To overcome these limitations, peak power assistance concepts have to be

considered.

For example, a wireless Sensor node transmits its gathered data once a day to a base

station. The data transmission requires 500mA for 200ms. This short power peak

cannot be supported by the primary cell itself. The pulse needs to be buffered

somewhere else.

1

http://www.tadiranbatteries.de/pdf/lithium-thionyl-chloride-batteries/SL-360.pdf

Advanced Low Power Solutions

Page 3 of 16

Test Report

PMP9753

2 Reference Design Description

This Reference Design shows an Energy Buffering Concept based on the TPS62740, a

360nA quiescent current buck converter, in combination with an EDLC (electric double

layer capacitor) or a so called Supercapacitor.

Voltage control (µController)

VSEL

Charge Current

e.g. 3mA max.

TPS62740

Primary

Cell

Storage

Capacitor,

EDLC

Figure 2: Simplified charging block diagram

The circuit uses a resistor at the output of the TPS62740 to limit the current into the

Storage Capacitor as well as the battery current drawn from the primary cell. The

resistor will be selected in a way to keep the load and thereby the battery current below

a level, the primary battery can support. The TPS62740 features a digital input to

adjust the output voltage by four VSEL Pins. During the charging of the EDLC, the

output voltage can be stepped up in 100mV steps. This helps to minimize the power

losses caused by the resistor.

Advanced Low Power Solutions

Page 4 of 16

Test Report

PMP9753

In an application like a wireless sensor, the µController will be supplied from the output

of the TPS62740 step-down converter. Therefore the voltage must stay above the

µController minimum supply voltage (e.g. 1.9V). The maximum voltage of a single layer

super-cap is typically 2.7V which leads to a usable capacitor voltage range of 1.9V to

2.7V

Figure 3 shows the basic flow of a recharge cycle.

Most of the time the voltage is kept at 1.9V to minimize the losses of the microcontroller and other leakage currents in the application (Phase 1). Prior a wireless data

transmission, the capacitor is charged up to 2.7V (Phase 2). During transmission the

stored energy in the capacitor can be extracted down to 1.9V (Phase 3).

For a more detailed description including component and parameter calculations,

please see Application Report TIDU628.

VMAX

2.7V

1.9V

VMIN

idle

charge

1

VSEL [V]

2

1.9

Stepping 1.9 .. 2.7

radio transmittion

discharge

idle

3

1

1.9

1.9

active

TIME [~]

13 min

200ms

Figure 3: Recharge Cycle Sequencing

Advanced Low Power Solutions

Page 5 of 16

Test Report

PMP9753

2.1 Detailed Block Diagram

Figure 4 below shows the Block Diagram of the Energy Buffering Reference Design. It

consists of following main blocks:

•

•

•

•

•

Primary Cell

TPS62740 Buck Converter

Current Limiting Resistor Network

Storage Capacitor

Connection to the µController

The LiSoCl2 primary cell is directly connected to the TPS62740. The Buck Converter is

controlled by the available µController in the Application. The MCU enables/disables

the Buck Converter, adjusts the output voltage and enables the efficient charging as

shown in Figure 3.

The output of the DC/DC Converter is connected to the current limiting resistor. Figure

4 shows two resistors, one resistor can be connected by a switch. This is designed to

handle the start-up procedure which is necessary to pre-charge the EDLC to the

minimum Voltage of 1.9V. To not exceed the maximum battery current, only the 300Ω

resistor is used.

Once the Storage Capacitor is pre-charged, the switch is turned on and the current is

limited by the combined resistance.

A load like a radio power amplifier can now be directly connected to the storage

capacitor which does support larger peak currents to be drawn from it.

µController

Control

Power

5

VSEL, EN

LowIq-Buck

TPS62740

PMP9753

Figure 4: Reference design block diagram

Advanced Low Power Solutions

Page 6 of 16

Test Report

PMP9753

2.2 Wireless Metering-Bus Circuit Definition

The measurement results presented in this document use the following typical use

case: A Wireless-Metering-Bus (wM-Bus) data transmission with following parameters:

•

•

•

•

Battery Voltage = 3.6V

Maximum battery current = 3mA

Transmission duration = 200ms

Transmission power = 1000mW

The consideration is that the system uses a LiSoCl2 primary battery. The primary cell is

fresh and has a voltage of 3.6V. To make sure not to reduce the battery operation

runtime, the battery current should not exceed 3mA during continuous operation.

It is only necessary to buffer the energy for one wM-Bus data transmission which

requires 1000mW and has duration of maximum 200ms. To have enough margins, a

0.47F capacitor is used.

To achieve a system runtime of at least 15 years, the muRata EDLC

DMF3Z5R5H474M3DTA0 is only charged up to 2.7V. Another benefit of keeping the

voltage at this level is that there is no need for balancing which would add additional

energy losses.

For more details around the calculation of the parameters and devices’ values, please

refer to Energy Buffering Application Report TIDU628.

Advanced Low Power Solutions

Page 7 of 16

Test Report

PMP9753

2.3 Schematic

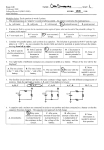

Figure 5: PMP9753 schematic

Advanced Low Power Solutions

Page 8 of 16

Test Report

PMP9753

3 Measurement Results

Following Section shows the results of the start-up sequence where the EDLC is precharged to its minimum value. It also shows the results of the regular recharge cycle

and the conversion efficiency for charging the capacitor.

3.1 Start-up behavior

Figure 6 shows the circuit configuration during start-up. For this scenario only the

higher 300Ω resistor is used.

As the input current must not be higher than ~3.5mA during start-up, the corresponding

output current has to be limited to 6.3mA. For the initial voltage step of 1.9V, the

resistor value is chosen as 300Ω

For more detailed calculations, please refer to Energy Buffering Application Report

TIDU628.

USB2ANY

Control

PC Interface

Power

Measure

A

LowIq-Buck

TPS62740

Load

V

V

Figure 6: Start-up circuit configuration

Advanced Low Power Solutions

Page 9 of 16

Test Report

PMP9753

Following graph shows the curves of the voltage across the EDLC and the battery

current drawn. It shows that the battery current is limited to 3.7mA which corresponds

to the calculated value above. This current is just flowing for the first time the

application is powered up and it becomes smaller the higher the voltage at the storage

capacitor is.

This sequence occurs at the very first initializing of the circuit. It just happens once in

the whole lifetime of the application.

3

1.00E-02

Storage Capacitor Voltage

Battery Current

2.5

8.00E-03

2

Current [A]

Voltage [V]

6.00E-03

1.5

4.00E-03

1

2.00E-03

0.5

0

0.00E+00

0

100

200

300

400

500

600

700

800

900

time [s]

Figure 7: Battery current and capacitor voltage during pre-charge

Advanced Low Power Solutions

Page 10 of 16

Test Report

PMP9753

3.2 Recharge Sequence Results

The block diagram in Figure 8 shows the measurement setup for the recharge

sequence. This sequence is present prior every data transmission in the application.

The test sequence is controlled by TI’s USB2ANY Interface and a LabVIEW program.

The software controls the VSEL-Pins and adjusts the output voltage. This is how the

sequencing in Figure 3 is implemented.

In a normal application this is controlled by the µController that is present.

USB2ANY

Control

PC Interface

Power

Measure

A

LowIq-Buck

TPS62740

Load

V

V

Figure 8: Diagram of the measurement setup

Advanced Low Power Solutions

Page 11 of 16

Test Report

PMP9753

Figure 9 shows the waveforms in the application during a recharge cycle of the EDLC.

In this sequence, the initial voltages at the storage capacitor as well as at the output of

TPS62740 are at 1.9V.

Prior a wM-Bus data transmission, the capacitor is charged up by incrementing the

TPS62740 output voltage in steps of 100mV.

Between the steps, the capacitor charges up to the next higher 100mV value. The

current is limited by the resistor to its maximum value right after a step in the DC/DC

converter’s output voltage occurred and it decreases as expected in a RC-charge

configuration. Once the capacitors voltage is at the level of the DC/DC converters

output the next higher output voltage of the TPS62740 is selected. This way the

voltage drop across the current limiting resistor will always be 100mV or below leading

to reduced energy losses and highly efficient charging of the super-capacitor from 1.9V

to 2.7V

Voltage across Storage Capacitor

2.9

14

Output Voltage of TPS62740

12

Battery Current

2.5

10

2.3

8

2.1

6

1.9

4

1.7

2

1.5

0

200

400

600

Time [sec]

800

1000

1200

Current [mA]

Voltage [V]

2.7

0

1400

Figure 9: Charging waveforms

Advanced Low Power Solutions

Page 12 of 16

Test Report

PMP9753

3.3 Recharge Conversion Efficiency Results

Figure 10 shows that the loss of the whole power conversion from the primary cell to

the EDLC is split. It is the sum of the losses caused by the DC/DC Converter and the

current limiting resistor.

Losses due to

DC/DC Converter

Losses due to

Resistor

TPS62740

Resistor

Overall Losses

Figure 10: Conversion efficiency

The DC/DC Efficiency is found from Datasheet Curves. An excerpt is shown in Figure

11. Taking the curve, with an input voltage of 3.6V, the efficiency at 4.5mA of output

current is ~91%. At this TPS62740 output current, the battery current is in the range of

2-3mA (Figure 9).

The highest losses are generated right after a new output voltage step, where the

current through the resistor is the highest. For this case, the power loss is at its

maximum.

Between two steps, the current decreases and therefore the resistor losses decrease

as well. As shown in Figure 11, the Efficiency of the TPS62740 stays above 90% even

down to 100µA.

Advanced Low Power Solutions

Page 13 of 16

Test Report

PMP9753

91%

4.5mA IOUT

Figure 11:TPS62740: Efficiency vs. output current

The energy conversion efficiency is measured with the setup as shown in Figure 12.

The input power is taken by measuring the battery current multiplied by the battery

voltage.

The energy stored in the capacitor is determined by the charging current through the

resistor and the voltage across the capacitor.

Figure 13 shows the overall power losses for the conversion sequence. In Figure 14,

the energy drawn from the battery and the one stored in the EDLC are monitored and

put into perspective. It shows that the energy buffering concept show in this document

has an conversion efficiency close to 90%.

Power

Measure

A

LowIq-Buck

TPS62740

A

V

Figure 12: Energy conversion efficiency measurement setup

Advanced Low Power Solutions

Page 14 of 16

Test Report

PMP9753

1000

Overall charging losses in Micro-Watt

900

800

Power Loss [µW]

700

600

500

400

300

200

100

0

0

100

200

300

400

500

600

700

800

900

1000

time [s]

Figure 13: Overall charging power losses

1.20

90

80

1.00

70

60

50

0.60

40

0.40

Efficiency [%]

Energy (t) [Ws]

0.80

30

Energy drawn from the battery

0.20

Energy stored in the EDLC

20

10

Conversion energy efficiency

0.00

0

0

500

1000

1500

2000

time [s]

Figure 14: Energy conversion efficiency

Advanced Low Power Solutions

Page 15 of 16

Test Report

PMP9753

4 Summary

Due to the characteristics of certain batteries, applications with ultra-long runtimes

need new concepts for buffering energy.

Using an EDLC in combination the TPS62740 brings following main advantages:

• Single Cell Super Capacitor with a maximum voltage of below 3V can be used

• Storage Capacitors like muRata DMF series enable an application runtime of

>15 years.

• Pulsed currents are decupled from batteries leading to more extractable energy

• Application runtimes are extended because of the high efficiency of the solution

The charging sequence can be implemented efficiently due to the digital output voltage

selection feature of TPS62740.

This Buck Converter is designed to operate with a quiescent current of typical 360nA

and is ideal for a direct connection to the battery and ultra-long runtimes.

Applications like a wireless sensor node can use the existing µController to handle the

charging sequence of the EDLC.

Advanced Low Power Solutions

Page 16 of 16

IMPORTANT NOTICE FOR TI REFERENCE DESIGNS

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers (“Buyers”) who are developing systems that

incorporate TI semiconductor products (also referred to herein as “components”). Buyer understands and agrees that Buyer remains

responsible for using its independent analysis, evaluation and judgment in designing Buyer’s systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. TI has not conducted any

testing other than that specifically described in the published documentation for a particular reference design. TI may make

corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the

reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL

OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY

OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right,

or other intellectual property right relating to any combination, machine, or process in which TI components or services are used.

Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a

warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual

property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE

REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR

COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS

FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY

INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE

FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO

OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE

LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY

THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN

ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER’S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per

JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant

information before placing orders and should verify that such information is current and complete. All semiconductor products are sold

subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI’s terms

and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI

deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not

necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers’ products. Buyers are responsible for their products and

applications using TI components. To minimize the risks associated with Buyers’ products and applications, Buyers should provide

adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is

without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for

such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements

concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support

that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that

anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate

remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in

Buyer’s safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI’s goal is to

help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and

requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties

have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or “enhanced plastic” are designed and intended for use in

military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that

have not been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory

requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of

non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2014, Texas Instruments Incorporated