* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download a. For VIN VT , M1 is in cutoff regime, thus I=0 and Vout = 2.5V

Index of electronics articles wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Radio transmitter design wikipedia , lookup

Thermal runaway wikipedia , lookup

Nanofluidic circuitry wikipedia , lookup

Integrating ADC wikipedia , lookup

Current source wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Wilson current mirror wikipedia , lookup

Operational amplifier wikipedia , lookup

Voltage regulator wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Schmitt trigger wikipedia , lookup

Opto-isolator wikipedia , lookup

Surge protector wikipedia , lookup

History of the transistor wikipedia , lookup

Power electronics wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Power MOSFET wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

Current mirror wikipedia , lookup

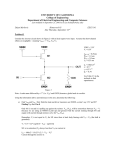

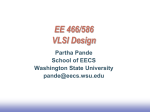

3. a. b. For VIN < VT , M 1 is in cuto regime, thus I=0 and Vout = 2.5V . For VIN > VT , M1 is conducting and Vout = 2.5V − (I ∗ R). This in turn gives a low Vout and the input signal is inverted. Assuming negligible leakage, when VIN < VT , transistor M1 is o and VOH = 2.5V . For VIN = 2.5V , assume M1 is in the linear region, and because VDS is negligible in the linear region, channel-length modulation can be ignored. For the linear region, Vmin = VDS = Vout = VOL = 46.25m. Checking the assumption: VGT = 2.07V , VDSat = 0.63V , and VDS = 46.25m, thus, M1 was correctly assumed to be in the linear region. To nd VM , set the resistor current equal to the NMOS current, with an input and out put voltage of VM . 2 (V − 0.43) 2.5 − VM = kn (1 + 0.06VM ) 75k 2 Thus, VM = 0.79V . To nd VIL and VIH , the slope of the VTC, at VM , is derived and the line is extrapolated out to VOH and VOL respectively. Ignoring the eects of channel length modulation, the slope is given by the following: RL kn W dVo =− (2Vin − 0.86) dVin 2L Plugging VM = 0.79V , into the slope equation above, gives a slope of 9.32. Extrapolating the line back to VOH gives VIL = 0.607V and the extrapolation of the line to VOL gives VIH = 0.87V . c. d. N ML = VIL = 0.607V and N MH = 2.5V − VIH = 1.63V . (i) Vin = 0 means M1 is cuto, therefore, IV DD = 0 and consequently PV DD = 0. (ii) Vin = 2.5V , Vout = VOL = 46.25mV , IV DD = ∆V 2.5 − 46.25m = = 32.7µA R 75k P = VDD × IV DD = 2.5V × 32.7mA = 81.75mW e. Spice results: Figure 1: Hspice results. f. As RL increases, the VTC curve becomes more ideal for the following reasons: VOL decreases, N ML increases, VIH decreases, and N MH increases. However, these come as tradeos because, as RL increases, VIL decreases, which is less ideal, and VOH remains unchanged. 1 g. As the impedance load increases, there is a tradeo, the inverter VTC becomes more ideal with a higher gain and thus better noise margins. However, the VTC curve is shifted in favor of M1 and the threshold voltage is lowered as the VTC moves to the left. 5. a. Circuit A: VOH : We calculate VOH , when M1 is o. The threshold for M2 is: q q VT = VT 0 + γ( |-2φF + VSB |- |-2φF |), VSB = VOU T , |-2φF | = 0.6V and M2 will be o when: VGS VT = VDD VOU T VT = 0. Substitute VT in the last equation and solve for VOU T . p p VDD VOU T VT = 2.5 − VOU T − 0.43 + 0.4 |0.6 + VOU T | − |0.6| = 0 We get VOU T = VOH = 1.765V VOL : To calculate VOL , we set VIN = VDD = 2.5V . We expect VOU T to be low, so we can make the assumption that M2 will be velocity saturated and M1 will be in the linear region. For M2: 0 W2 V2 ID2 = kn (VGS − VT ) · VDSAT − DSAT (1 + λVDS ) L2 2 and for M1: 0 ID1 = kn W1 L1 (VGS − VT 0 ) · VDS − 2 VDS 2 Setting ID1 = ID2 we get an equation and we solve for VOU T . We get VOU T = VOL = 0.263V , so our assumption holds. VM : To calculate VM we set VM = VIN = VOU T . Assuming that both transistors are velocity saturated, then we have the next pair of equations: 2 0 W1 VDSAT (1 + λVM ) ID1 = kn (VM − VT 0 ) · VDSAT − L1 2 2 0 W2 VDSAT ID2 = kn (1 + λ (VDD − VM )) (VDD − VM − VT ) · VDSAT − L2 2 Setting ID1 = ID2 , we get for VM = 1.269V Circuit B: When VIN = 0V , the NMOS transistor is o and the PMOS transistor in on and pulls VOU T up to VDD , so VOH = 2.5V . Similarly, when VIN = 2.5V , the PMOS transistor is o and the NMOS transistor pulls VOU T all the way down to ground, so VOL = 0V . To calculate VM we set VM = VIN = VOU T . We assume that both transistors are velocity saturated. We get the following pair of equations: ! 2 VDSAT 0 W4 p (VM − VDD − VT 0p ) · VDSAT p − (1 + λp VM ) ID4 = kp L4 2 0 W3 V2 ID3 = kn (VM − VT 0n ) · VDSAT n − DSAT n (1 + λn VM ) L3 2 Setting ID3 + ID2 = 0 , we get for VM = 1.095V . So the assumption that both transistors were velocity saturated holds. b. The two VTCs are shown below. 2 Figure 2: Depletion Load Inverter and CMOS Inverter. c. Circuit A: VIL = 0.503V ⇒ VOU T 1 = 1.65V, VIH = 1.35V ⇒ VOU T 2 = 0.588V N MH = VOH − VOU T 2 = 1.765 − 1.65 = 0.115V, N ML = VOU T 1 − VOL = 0.588 − 0.23 = 0.358V Circuit B: VIL = 0.861V ⇒ VOU T 1 = 2.33V, VIH = 1.22V ⇒ VOU T 2 = 0.219V N MH = VOH − VOU T 2 = 2.5V − 1.22V = 1.28V, N ML = VOU T 1 − VOL = 0.861V − 0V = 0.861V We can increase the noise margins by moving VM closer to the middle of the output voltage swing. d. It is clear from the two VTCs, that the CMOS inverter is more robust, since the low and high noise margins are higher than the rst inverter. Also the regeneration in the second inverter is greater since it provides rail to rail output and the gain of the inverter is much greater. 8. a. To determine the rise time, an average current has to be calculated between the start of the transition with VO = 0V and midpoint of the transition. At the start of the transition: VO = VOL = 0V , M1 is velocity saturated and IDsat = 1.46mA. To nd the voltage swing, VOH must be calculated using the body eect: p √ Vgs = 2.5V − VOH = Vtn + γ |0.6 + VOH | − 0.6 VOH = 1.76V . The midpoint is thus, VOH − VOL = 0.88V 2 and the threshold voltage at the midpoint is VT (Vsb = 0.88V ) = 0.607V . Using this threshold voltage, VGT = 1.013V, VDS = 1.62V, andVDSat = 0.63V , thus transistor M1 is still velocity saturated, giving IDSat = 49.17mA. Finding the average current between V0 = 0V and V0 = 0.88V gives: Iaverage = 0.756mA. tp = 5pf × 0.88V CL ∆V = = 5.82ns Iaverage 0.756mA b. tpLH = 0.69RL CL = 0.69 × 5kΩ × 5pF = 17.25ns c. ∆QV DD = Cl ∆V = 5pF × 1.76V = 8.8pC ∆EV DD = ∆QV DD VDD = 8.8pC × 2.5V = 22pC Half the energy is dissipated in the transistor M1, while the other half is dissipated in the restistor Rs . The energy dissipated is independent of Rs . 3 d. If a PMOS device replaces the NMOS device, body eect will not exist and the PMOS device will be faster. 12. a. b. The range will be from 0.4 V to 2.07 V, since the PMOS is a weak pull down device and the NMOS is a weak pull up device. For a 0 V to 2.5 V transition on the input, the energy drawn from the power supply is: Q ˆ ESU P P LY = iV DD VDD dt = VDD ∆Q = CVDD ((VDD − Vtn ) − |Vtp |) The PMOS will be in cuto and the energy dissipated in the NMOS will be: EDISSIP AT ED = ESU P P LY − ∆ECAP " = CVDD ((VDD − Vtn ) − |Vtp |) − C VDD − Vtn 2 2 − |Vtp | 2 2 # For a 2.5 V to 0 V transition on the input, the NMOS will be in cuto and no energy will be drawn from the power supply. The energy dissipated in the PMOS device will be equal to: " 2 2 # VDD − Vtn |Vtp | E=C − 2 2 c. When the input is high and the capacitor charges, the PMOS device is in cuto and the NMOS is velocity saturated for the duration of the charging. The total voltage range is 0.4 V to 2.07 V, so the midpoint is 1.24 V. We can use the average current method to approximate tplh . For the velocity saturated NMOS: µn Cox W VDSAT N VDSAT N VGS − Vtn − (1 + λVDS ) I= L 2 Solving for the current at V=0.4 V and V=1.24 V and averaging yields an average current of 404 uA. Then: C∆V (100f F )(1.24V − 0.4V ) tplh = = 208ps = Iavg 404µA d. The PMOS will be deep in cuto when Vout approaches VOH . Therefore, we consider only the NMOS. We can express the equation for threshold voltage numerically as follows: p √ Vtn = 0.43 + 0.5( 0.6 + 2.5 − Vtn − 0.6) This is an equation in one variable, so it may be solved numerically to nd that Vtn = 0.8V . 15. a. Minimum delay occurs when the delay through each √ √ buer is the same. This can be achieved by sizing the buer as f , f 2 , respectively where f = N F = 3 2000 = 12.6, so (γ = 0) tp = N tp0 (1 + f/γ ) = 3 · 70ps · (1 + 12.6) = 2.8ns b. c. From the text, we know that the minimum delay occurs when f = e. Therefore, N = ln(2000) = 7.6 ln(f ) f = e tdelay = 7 × 3.96 × 70ps = 1.9ns ln(2000) 7 = 2.96 Solution (b) is faster but it consumes much more area than (a). 4 d. The power consumption is determined as follows: 1 α T 4 3 X f −1 1 2 1 k 2 1 = 136 pW P = Ci Vdd α f = Ci Vdd α T T f −1 T 2 P = Ctot Vdd k=0 16. Consider scaling a CMOS technology by S > 1. In order to maintain compatibility with existing system components, you decide to use constant voltage scaling. a. 2 We know that P ∝ CVDD f and f ∝ 1 tp ∝ IDsat CVDD , P ∝ IDsat V ∝ k To keep power constant we need to scale W ∝ smaller. so 0 W W 2 (V − Vt ) V ∝ (s) 1 L S 1 s2 . which means redesigning gates with W a factor of 1/s b. WL CV tp ∝ 0 W 2 ∝ 0 W t ∝ k LV k LV 1 s2 1 s 1/s2 s 1/s 1 1/s so tp ∝ 1/s2 . c. P ∝ ISAT VDD ∝ VDD W Cox (Vgs − Vt ) vmax ∝ W (s), so W ∝ 1s . This means that no changes need to be made. 5