* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download ECE 452 - Rose

Oscilloscope history wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Phase-locked loop wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Topology (electrical circuits) wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Josephson voltage standard wikipedia , lookup

Radio transmitter design wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Two-port network wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Operational amplifier wikipedia , lookup

Schmitt trigger wikipedia , lookup

Wilson current mirror wikipedia , lookup

Power MOSFET wikipedia , lookup

Integrating ADC wikipedia , lookup

Surge protector wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Current source wikipedia , lookup

Voltage regulator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Opto-isolator wikipedia , lookup

Power electronics wikipedia , lookup

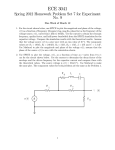

ECE 452 PSpice Project 9 Single-Phase Half-Wave, Full-Wave Bridge, and Three-Phase FullWave Converters with SCRs Objective The objective of this project is to become familiar with the performance of single-phase half-wave and full-wave bridge converters/rectifiers that utilize SCRs. Additionally, to simulate the performance of a three-phase full converter/rectifier, and the response of output current in particular. Procedure Implement the circuit of Figures 1 and 2 in the PSpice. The sinusoidal source (Vsin) has an rms voltage of 120 V and a frequency of 60 Hz. The load has a resistance of 5 in series with an inductance of 0 mH. For the SCR, use the 2N1595 model in the EVAL library. Then edit this PSpice model and replace the code with the following code, which is the SCR model of page 483 of your textbook: .SUBCKT SCR 1 3 2 * anode gate cathode S1 1 5 6 2 SMOD RG 3 4 50 VX 4 2 DC 0V VY 5 7 DC 0V DT 7 2 DMOD RT 2 6 1 CT 6 2 10E-6 F1 2 6 POLY(2) VX VY 0 50 11 .MODEL SMOD VSWITCH (RON=0.0125 ROFF=10E+5 VON=0.5V VOFF=0V) .MODEL DMOD D(IS=2.2E-15 BV=1800V TT=0) .ENDS SCR Use a pulse (Vpulse) for triggering SCRs with the following parameters: Initial Voltage = 0 V Fall Time = 4 ns Pulse Voltage = 12 V Pulse Width = 200 s o Delay Time = 30 Period = 16.6667 ms Rise Time = 2 ns SCR1 I0 I + 0 + SCR 1 R + SCR 3 R + VS V0 VS - V0 - L - Figure 1. Half-Wave SCR Converter SCR 4 L SCR 2 - Figure 2. Full-Wave SCR Converter Then perform the simulations and obtain the following for the circuits of Figures 1 and 2: 1. Plot the instantaneous input current, output current, and output voltage as 3 subplots on one graph from 0 to 50 ms. Calculated Vdc by hand. 2. Increase the Pulse Delay Time to 60 degrees and repeat Part 1. 3. Increase the Pulse Delay Time to 120 degrees and set L = 5 mH, then repeat Part 1. Now, implement the three-phase full converter of Figure 3 in the PSpice. The sinusoidal sources have an rms voltage of 120 V (line-to-neutral) and a frequency of 60 Hz. The load has a resistance of 2 in series with an inductance of 25 mH. + Van n Vbn Vcn - + - + - + i a a T1 T3 T5 i 0 i b b v 0 LOAD i c c T4 T6 T2 - Figure 3. Three-Phase Full Converter Use the same SCR model and the SCR triggering pulses. Perform the simulations for 40 ms, and plot/calculate the following: 1. For a delay angle of 0 degree, a. Plot all six gate voltages as 6 subplots on one graph. b. Plot the output voltage (first), voltage across the resistor, and voltage across the inductor as 3 subplots on one graph. c. Plot the output current (first), phase "a" current, phase "b" current, and the phase "c" current as 4 subplots on one graph. d. Calculate Vdc by hand. 2. For a delay angle of 90 degrees, a. Plot all six gate voltages as 6 subplots on one graph. b. Plot the output voltage (first), voltage across the resistor, and voltage across the inductor as 3 subplots on one graph. c. Plot the output current (first), phase "a" current, phase "b" current, and the phase "c" current as 4 subplots on one graph. d. Calculate Vdc by hand. Report Write a memo and discuss the results. Attach the PSpice output files and all of your hand calculations to your memo.