* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download revised hw#1

Distributed element filter wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Operational amplifier wikipedia , lookup

Schmitt trigger wikipedia , lookup

Spectrum analyzer wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Telecommunications engineering wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Zobel network wikipedia , lookup

RLC circuit wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Power electronics wikipedia , lookup

Power MOSFET wikipedia , lookup

Opto-isolator wikipedia , lookup

Index of electronics articles wikipedia , lookup

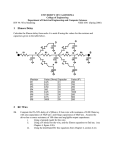

Revised Homework: Don’t do problems #2, #3, #4 Replace with these problems: a) Sketch the impedance of your chip to the package to the board to the Spectrum Analyzer (see figure on last page) Blocks A and B are the pads of your 0.18um TSMC testchip. A is chip bond-pad, 150um x 150um size, or parallel plate capacitance of 0.2pF. AA is bond-wire from bond pad to package pad. Assume 2mm long (1nH/mm) AAA is package impedance. Assume 55 Ohm, 1ns long distance. AAAA is bonding capacitance. Board bonding pad has large capacitance to GND. Assume 1pF. AAAAA is via capacitance. Trace needs to go from top of board to bottom of board. This looks like a capacitance. Assume 1pF. B is a transmission line. It needs to be XXXX Ohm impedance, 20ns distance. It has no loss. Assume BB and BBB is the input into the spectrum analyzer (or oscilloscope, or antennae, or other chip, etc. etc). Assume ideal, impedance here of 50 Ohms. b) Sketch the trace height/width of the transmission line B, both in FR4 and in Teflon. How wide is the wire B? How far is it above the GND plane? c) Simulate the AC response of the line. Stick in a AC voltage source into node A, with a series source termination of 50 Ohms. Measure on a log/log scale the AC response of the channel, with respect to the output at “BB”. d) Replace ideal transmission line B with a lossy transmission line, and simulate its AC response. (i.e. lossy transmission line whose frequency response has bandwidth rolloff at higher frequencies. For example, due to metal skin effect resistance or dielectric loss.) You can obtain the model for the lossy transmission line using the file “~pchiang/rlc.rlc”, and usage statement in “~pchiang/rlc_spice_deck”. e) Simulate the transient response of the line. Simulate this by putting a 1V voltage source, in series with 50 Ohms, and drive a singular “010” pulse, and measure the response at the end at “BB”. Make the DATA-HIGH portion 5ns long. (Or 200MHz) f) Simulate the transient response again, but make the DATA-HIGH portion 500ps long. (Or 2GHz) 3. In problem 2, we simulated the transient response with an ideal voltage source and a series source resistor of 50 Ohms. Now we will need to replace it with what we normally drive the output with – a large inverter. Replace the voltage source/50 Ohm source resistance with a large inverter.(There is no 50 Ohm source termination anymore). Use any technology you want (i.e. 180nm, 90nm), and put a large inverter there. Say, PMOS = 200um/90nm, NMOS=100um/90nm. Simulate for a 5ns pulse, and for a 200MHz pulse, and 500ps pulse. Simulate your inverter driver “010” for both an ideal transmission line, and for a lossy rlc.rlc transmission line. 4. Replace the inverter structure with the current-mode logic structure. Swing 400mV at the output using the differential pair, current mode switching logic, and 50 Ohm source termination to VDD. Simulate this for “010” of your data input for 5ns pulse, and 200MHz pulse, and for 500ps pulse. Simulate this current-mode structure for an ideal transmission line, as well as for a lossy rlc.rlc transmission line. 5. Replace the “010” input stimulus with the random data sequence. Use PWL statement to create random data symbol string for 10 bits. (i.e. 0010111010) Simulate for both inverter driver (5ns, 500ps per bit) and current-model logic driver(5ns, 500ps per bit). Simulate also for ideal transmission line, as well as for lossy rlc.rlc transmission line. Spectrum Analyzer BBB BB ... B AA CHIP A B AAA AAAA AAAAA CHIP PACKAGE PCB BOARD Figure #1: Idea of chip-package trace design, and how it appears from 2D sense.