AD8348 数据手册DataSheet 下载

... I- and Q-Channel Differential Baseband Outputs. Typical output swing is equal to 2 V p-p differential. The dc common-mode voltage level on these pins is set by the voltage on VCMO. Baseband DC Common-Mode Voltage. The voltage applied to this pin sets the dc common-mode levels for all the baseband ou ...

... I- and Q-Channel Differential Baseband Outputs. Typical output swing is equal to 2 V p-p differential. The dc common-mode voltage level on these pins is set by the voltage on VCMO. Baseband DC Common-Mode Voltage. The voltage applied to this pin sets the dc common-mode levels for all the baseband ou ...

MAX9320/MAX9320A 1:2 Differential LVPECL/LVECL/HSTL Clock and Data Drivers General Description

... The MAX9320/MAX9320A are low-skew, 1-to-2 differential drivers designed for clock and data distribution. The input is reproduced at two differential outputs. The differential input can be adapted to accept single-ended inputs by applying an external reference voltage. The MAX9320/MAX9320A feature ul ...

... The MAX9320/MAX9320A are low-skew, 1-to-2 differential drivers designed for clock and data distribution. The input is reproduced at two differential outputs. The differential input can be adapted to accept single-ended inputs by applying an external reference voltage. The MAX9320/MAX9320A feature ul ...

PCF1179CT

... The number (n) is stored in a non-volatile memory which is achieved by the following steps (see Fig.6): 1. Set SEL to VSS and a level of VDD − 5 V to VPP 2. The quartz-frequency deviation ∆f/f is measured and (n) is calculated (see Table 1) 3. A first pulse tE is applied to the DATA input clears the ...

... The number (n) is stored in a non-volatile memory which is achieved by the following steps (see Fig.6): 1. Set SEL to VSS and a level of VDD − 5 V to VPP 2. The quartz-frequency deviation ∆f/f is measured and (n) is calculated (see Table 1) 3. A first pulse tE is applied to the DATA input clears the ...

14-Bit, 500 kSPS PulSAR ADC in MSOP AD7946

... the data should be read when CNV is high. Serial Data Output. The conversion result is output on this pin. It is synchronized to SCK. Serial Data Clock Input. When the part is selected, the conversion result is shifted out by this clock. Serial Data Input. This input provides multiple features. It s ...

... the data should be read when CNV is high. Serial Data Output. The conversion result is output on this pin. It is synchronized to SCK. Serial Data Clock Input. When the part is selected, the conversion result is shifted out by this clock. Serial Data Input. This input provides multiple features. It s ...

AD6640 数据手册DataSheet下载

... that the input voltage on either encode pin does not go below 0 V. The maximum value ensures that the input voltage on either ENCODE pin does not go below 2.0 V or above AVCC (e.g., for a differential input swing of 0.8 V, the min and max common-mode specs become 0.4 V and 2.4 V, respectively). ...

... that the input voltage on either encode pin does not go below 0 V. The maximum value ensures that the input voltage on either ENCODE pin does not go below 2.0 V or above AVCC (e.g., for a differential input swing of 0.8 V, the min and max common-mode specs become 0.4 V and 2.4 V, respectively). ...

"Lessons In Electric Circuits, Volume IV -

... quantity – length – to represent numbers, and to help perform arithmetical operations with two or more numbers at a time. It, too, is an analog device. On the other hand, a digital representation of that same monetary figure, written with standard symbols (sometimes called ciphers), looks like this: ...

... quantity – length – to represent numbers, and to help perform arithmetical operations with two or more numbers at a time. It, too, is an analog device. On the other hand, a digital representation of that same monetary figure, written with standard symbols (sometimes called ciphers), looks like this: ...

CY62128EV30 MoBL®, 1-Mbit (128 K × 8) Static RAM

... 15. Test Conditions for all parameters other than tri-state parameters assume signal transition time of 3 ns or less (1 V/ns), timing reference levels of VCC(typ)/2, input pulse levels of 0 to VCC(typ), and output loading of the specified IOL/IOH as shown in the Figure 4 on page 5. 16. At any given ...

... 15. Test Conditions for all parameters other than tri-state parameters assume signal transition time of 3 ns or less (1 V/ns), timing reference levels of VCC(typ)/2, input pulse levels of 0 to VCC(typ), and output loading of the specified IOL/IOH as shown in the Figure 4 on page 5. 16. At any given ...

MAX3453E–MAX3456E ±15kV ESD-Protected USB Transceivers General Description Features

... USB devices. The devices fully comply with USB 1.1 and USB 2.0 when operating at full (12Mbps) and low (1.5Mbps) speeds. The MAX3453E–MAX3456E operate with VL as low as +1.65V, ensuring compatibility with low-voltage ASICs. The MAX3453E–MAX3456E feature a logic-selectable suspend mode that reduces c ...

... USB devices. The devices fully comply with USB 1.1 and USB 2.0 when operating at full (12Mbps) and low (1.5Mbps) speeds. The MAX3453E–MAX3456E operate with VL as low as +1.65V, ensuring compatibility with low-voltage ASICs. The MAX3453E–MAX3456E feature a logic-selectable suspend mode that reduces c ...

ADS9110 18-Bit, 2-MSPS, 15-mW, SAR ADC

... input signals and operates with a 2.5-V to 5-V external reference, offering a wide selection of input ranges without additional input scaling. The device consumes only 15 mW of power when operating at the full 2-MSPS throughput. Power consumption at lower throughputs can be reduced by using the flex ...

... input signals and operates with a 2.5-V to 5-V external reference, offering a wide selection of input ranges without additional input scaling. The device consumes only 15 mW of power when operating at the full 2-MSPS throughput. Power consumption at lower throughputs can be reduced by using the flex ...

THS4081 Low-Power High Speed Operational

... 1.6 General High-Speed Amplifier Design Considerations The THS4081 EVM layout has been designed and optimized for use with high-speed signals and can be used as an example when designing THS4081 applications. Careful attention has been given to component selection, grounding, power supply bypassing, ...

... 1.6 General High-Speed Amplifier Design Considerations The THS4081 EVM layout has been designed and optimized for use with high-speed signals and can be used as an example when designing THS4081 applications. Careful attention has been given to component selection, grounding, power supply bypassing, ...

FEATURES

... data output to be minimized for optimum maximum-frequency system performance. In order to reduce this skew, a flexible setup time adjustment (FSTA) feature is incorporated into the device that sets a predetermined delay between the clock and data. The CMS and direction (DIR) inputs control the mode ...

... data output to be minimized for optimum maximum-frequency system performance. In order to reduce this skew, a flexible setup time adjustment (FSTA) feature is incorporated into the device that sets a predetermined delay between the clock and data. The CMS and direction (DIR) inputs control the mode ...

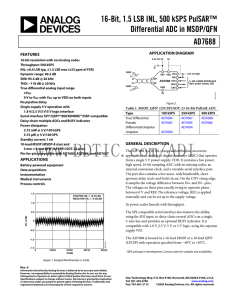

AD7688 数据手册DataSheet下载

... The AD7688 is a 16-bit, charge redistribution, successive approximation, analog-to-digital converter (ADC) that operates from a single 5 V power supply, VDD. It contains a low power, high speed, 16-bit sampling ADC with no missing codes, an internal conversion clock, and a versatile serial interface ...

... The AD7688 is a 16-bit, charge redistribution, successive approximation, analog-to-digital converter (ADC) that operates from a single 5 V power supply, VDD. It contains a low power, high speed, 16-bit sampling ADC with no missing codes, an internal conversion clock, and a versatile serial interface ...

mic2592b.pdf

... The MIC2592B is a dual-slot power controller supporting the power distribution requirements for Peripheral Component Interconnect Express (PCI Express) Hot-Plug compliant systems. The MIC2592B provides complete power control support for two PCI Express slots, including the 3.3VAUX defined by the PCI ...

... The MIC2592B is a dual-slot power controller supporting the power distribution requirements for Peripheral Component Interconnect Express (PCI Express) Hot-Plug compliant systems. The MIC2592B provides complete power control support for two PCI Express slots, including the 3.3VAUX defined by the PCI ...

LOG114 数据资料 dataSheet 下载

... Eight Decades, 100pA to 10mA 2.5V REFERENCE STABLE OVER TEMPERATURE LOW QUIESCENT CURRENT: 10mA DUAL OR SINGLE SUPPLY: +5V, +5V PACKAGE: Small QFN-16 (4mm x 4mm) SPECIFIED TEMPERATURE RANGE: −5°C to +75°C ...

... Eight Decades, 100pA to 10mA 2.5V REFERENCE STABLE OVER TEMPERATURE LOW QUIESCENT CURRENT: 10mA DUAL OR SINGLE SUPPLY: +5V, +5V PACKAGE: Small QFN-16 (4mm x 4mm) SPECIFIED TEMPERATURE RANGE: −5°C to +75°C ...

MAX1710/MAX1711/MAX1712 High-Speed, Digitally Adjusted Step-Down Controllers for Notebook CPUs General Description

... High DC precision is ensured by a 2-wire remote-sensing scheme that compensates for voltage drops in both the ground bus and supply rail. An on-board, digital-toanalog converter (DAC) sets the output voltage in compliance with Mobile Pentium II® CPU specifications. The MAX1710 achieves high efficien ...

... High DC precision is ensured by a 2-wire remote-sensing scheme that compensates for voltage drops in both the ground bus and supply rail. An on-board, digital-toanalog converter (DAC) sets the output voltage in compliance with Mobile Pentium II® CPU specifications. The MAX1710 achieves high efficien ...

A4988 - ICTP Scientific FabLab

... the change does not take effect until the next STEP rising edge. to a predefined Home state (shown in figures 8 through 12), and turns off all of the FET outputs. All STEP inputs are ignored until If the step mode is changed without a translator reset, and abso¯S̄¯Ē ¯T̄ ¯ input is set to high. the ...

... the change does not take effect until the next STEP rising edge. to a predefined Home state (shown in figures 8 through 12), and turns off all of the FET outputs. All STEP inputs are ignored until If the step mode is changed without a translator reset, and abso¯S̄¯Ē ¯T̄ ¯ input is set to high. the ...

In situ testing of detector controllers

... To see the noise and signals of interest we need • Low input referred noise and differential probe. • Same passband as the CDS processor • Samples to be synchronized to pixels. (Interference that is same on every pixel is benign) ...

... To see the noise and signals of interest we need • Low input referred noise and differential probe. • Same passband as the CDS processor • Samples to be synchronized to pixels. (Interference that is same on every pixel is benign) ...

General Description Features

... high output-current capability in a compact package with a minimum number of external components. The MAX16821A–MAX16821C are suitable for use in synchronous and nonsynchronous step-down (buck), boost, buckboost, SEPIC, and Cuk LED drivers. A logic input (MODE) allows the devices to switch between s ...

... high output-current capability in a compact package with a minimum number of external components. The MAX16821A–MAX16821C are suitable for use in synchronous and nonsynchronous step-down (buck), boost, buckboost, SEPIC, and Cuk LED drivers. A logic input (MODE) allows the devices to switch between s ...

ADS1212 数据资料 dataSheet 下载

... generator circuit; and an internal 2.5V reference. The ADS1213 includes a 4-channel input multiplexer. In order to provide low system noise, common-mode rejection of 100dB and excellent power supply rejection, the design topology is based on a fully differential switched capacitor architecture. Turb ...

... generator circuit; and an internal 2.5V reference. The ADS1213 includes a 4-channel input multiplexer. In order to provide low system noise, common-mode rejection of 100dB and excellent power supply rejection, the design topology is based on a fully differential switched capacitor architecture. Turb ...

High Voltage, Quad-Channel 12-Bit Voltage Output DAC AD5504

... Asynchronous Clear Input. The CLR input is falling edge sensitive. When CLR is low, all LDAC pulses are ignored. When CLR is activated, the input register and the DAC register are set to 0x000 and the outputs to zero scale. Falling Edge Synchronization Signal. This is the frame synchronization signa ...

... Asynchronous Clear Input. The CLR input is falling edge sensitive. When CLR is low, all LDAC pulses are ignored. When CLR is activated, the input register and the DAC register are set to 0x000 and the outputs to zero scale. Falling Edge Synchronization Signal. This is the frame synchronization signa ...

Atmel LED Driver-MSL3085 Datasheet Brief EEPROM, and I

... that dynamically adjust the LED string power supplies to their minimum voltage necessary to drive the LED strings, while assuring accurate LED current flow. One of the efficiency optimizers features an input that allows up to eight devices to be connected in a chain configuration. When implemented, ...

... that dynamically adjust the LED string power supplies to their minimum voltage necessary to drive the LED strings, while assuring accurate LED current flow. One of the efficiency optimizers features an input that allows up to eight devices to be connected in a chain configuration. When implemented, ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.