MT-075 TUTORIAL Differential Drivers for High Speed ADCs Overview

... Even if the external feedback networks (RF/RG) are mismatched, the internal common-mode feedback loop will still force the outputs to remain balanced. The amplitudes of the signals at each output will remain equal and 180° out of phase. The input-to-output differential-mode gain will vary proportion ...

... Even if the external feedback networks (RF/RG) are mismatched, the internal common-mode feedback loop will still force the outputs to remain balanced. The amplitudes of the signals at each output will remain equal and 180° out of phase. The input-to-output differential-mode gain will vary proportion ...

MAX1489E ±15kV ESD-Protected, Quad, Low-Power RS-232 Line Receiver _______________General Description

... The IEC100-4-2 standard covers ESD testing and performance of finished equipment; it does not specifically refer to integrated circuits. The MAX1489E helps you design equipment that meets Level 4 (the highest level) of IEC1000-4-2, without additional ESD protection components. The major difference b ...

... The IEC100-4-2 standard covers ESD testing and performance of finished equipment; it does not specifically refer to integrated circuits. The MAX1489E helps you design equipment that meets Level 4 (the highest level) of IEC1000-4-2, without additional ESD protection components. The major difference b ...

ics854104a.pdf

... the center of the input voltage swing. For example, if the input clock swing is only 2.5V and VDD= 3.3V, V_REF should be 1.25V and R2/R1 = 0.609. ...

... the center of the input voltage swing. For example, if the input clock swing is only 2.5V and VDD= 3.3V, V_REF should be 1.25V and R2/R1 = 0.609. ...

NM485SLC - power, Murata

... The increased use of balanced data transmission lines, (distributing data to several system components and peripherals over relatively long lines) has brought about the need for multiple driver/receiver combinations on a single twisted pair line. This resulted in an upgraded version of EIA RS-422, n ...

... The increased use of balanced data transmission lines, (distributing data to several system components and peripherals over relatively long lines) has brought about the need for multiple driver/receiver combinations on a single twisted pair line. This resulted in an upgraded version of EIA RS-422, n ...

FMS6143 Low-Cost Three-Channel 4th-Order Standard Defi nition Video Filter Driver

... Include a metal paddle under the device on the top layer. ■ Minimize all trace lengths to reduce series inductance. ...

... Include a metal paddle under the device on the top layer. ■ Minimize all trace lengths to reduce series inductance. ...

DESCRIPTION FEATURES ULTRA-PRECISION DIFFERENTIAL

... 1. Permanent device damage may occur if the ratings in “Absolute Maximum Ratings” section are exceeded. This is a stress rating only and functional operation is not implied for conditions other than those detailed in the operational sections of this data sheet. Exposure to absolute maximum ratings c ...

... 1. Permanent device damage may occur if the ratings in “Absolute Maximum Ratings” section are exceeded. This is a stress rating only and functional operation is not implied for conditions other than those detailed in the operational sections of this data sheet. Exposure to absolute maximum ratings c ...

General Description

... The Spartan®-6 family provides leading system integration capabilities with the lowest total cost for high-volume applications. The thirteen-member family delivers expanded densities ranging from 3,840 to 147,443 logic cells, with half the power consumption of previous Spartan families, and faster, ...

... The Spartan®-6 family provides leading system integration capabilities with the lowest total cost for high-volume applications. The thirteen-member family delivers expanded densities ranging from 3,840 to 147,443 logic cells, with half the power consumption of previous Spartan families, and faster, ...

FEATURES PIN ASSIGNMENT

... The 5-wire serial interface provides an 8-bit I/O shift register for loading and reading wiper data. The 5wire serial interface control is selected when the port select input, PS, is in a low state. This interface is controlled by the signals RST , DIN, DOUT, CLK, and R/ W . Timing diagrams for the ...

... The 5-wire serial interface provides an 8-bit I/O shift register for loading and reading wiper data. The 5wire serial interface control is selected when the port select input, PS, is in a low state. This interface is controlled by the signals RST , DIN, DOUT, CLK, and R/ W . Timing diagrams for the ...

NM485SLC

... The increased use of balanced data transmission lines, (distributing data to several system components and peripherals over relatively long lines) has brought about the need for multiple driver/receiver combinations on a single twisted pair line. This resulted in an upgraded version of EIA RS-422, n ...

... The increased use of balanced data transmission lines, (distributing data to several system components and peripherals over relatively long lines) has brought about the need for multiple driver/receiver combinations on a single twisted pair line. This resulted in an upgraded version of EIA RS-422, n ...

AD9755 数据手册DataSheet 下载

... a single data interface port DAC. The digital interface consists of two buffered latches as well as control logic. These latches can be time multiplexed to the high speed DAC in several ways. This PLL drives the DAC latch at twice the speed of the externally applied clock and is able to interleave t ...

... a single data interface port DAC. The digital interface consists of two buffered latches as well as control logic. These latches can be time multiplexed to the high speed DAC in several ways. This PLL drives the DAC latch at twice the speed of the externally applied clock and is able to interleave t ...

ADS804 数据资料 dataSheet 下载

... Several applications may require that the bandwidth of the signal path include DC, in which case the signal has to be DC-coupled to the A/D converter. In order to accomplish this, the interface circuit has to provide a DC-level shift. See the circuit of Figure 2 which employs an op amp, to sum the g ...

... Several applications may require that the bandwidth of the signal path include DC, in which case the signal has to be DC-coupled to the A/D converter. In order to accomplish this, the interface circuit has to provide a DC-level shift. See the circuit of Figure 2 which employs an op amp, to sum the g ...

SI844x,5x QSOP

... 1. Specifications in this table are also valid at VDD1 = 2.6 V and VDD2 = 2.6 V when the operating temperature range is constrained to TA = 0 to 85 °C. 2. The nominal output impedance of an isolator driver channel is approximately 85 , ±40%, which is a combination of the value of the on-chip series ...

... 1. Specifications in this table are also valid at VDD1 = 2.6 V and VDD2 = 2.6 V when the operating temperature range is constrained to TA = 0 to 85 °C. 2. The nominal output impedance of an isolator driver channel is approximately 85 , ±40%, which is a combination of the value of the on-chip series ...

mt-075 tutorial

... Even if the external feedback networks (RF/RG) are mismatched, the internal common-mode feedback loop will still force the outputs to remain balanced. The amplitudes of the signals at each output will remain equal and 180° out of phase. The input-to-output differential-mode gain will vary proportion ...

... Even if the external feedback networks (RF/RG) are mismatched, the internal common-mode feedback loop will still force the outputs to remain balanced. The amplitudes of the signals at each output will remain equal and 180° out of phase. The input-to-output differential-mode gain will vary proportion ...

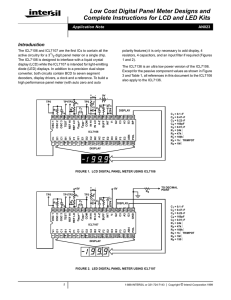

Low Cost Digital Panel Meter Designs and Complete

... read zero. The negative sign should be displayed about 50% of the time, an indication of the effectiveness of the auto-zero system used in the ICL7106 and ICL7107. Note that some competitive circuits flash negative on every alternate conversion for inputs near zero. While this may look good to the u ...

... read zero. The negative sign should be displayed about 50% of the time, an indication of the effectiveness of the auto-zero system used in the ICL7106 and ICL7107. Note that some competitive circuits flash negative on every alternate conversion for inputs near zero. While this may look good to the u ...

FPO SHC5320 FEATURES DESCRIPTION

... most recently sampled signal will be held. Amplifier A2 serves to present a high impedance load to the holding capacitor and to provide a low impedance voltage source for external loads. A minimum of three terminals are provided for the user: input, output, and mode control (or sample/hold control). ...

... most recently sampled signal will be held. Amplifier A2 serves to present a high impedance load to the holding capacitor and to provide a low impedance voltage source for external loads. A minimum of three terminals are provided for the user: input, output, and mode control (or sample/hold control). ...

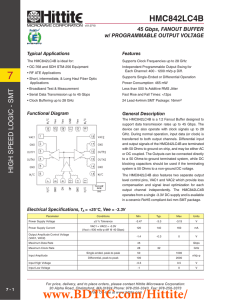

HMC842LC4B 数据资料DataSheet下载

... device can also operate with clock signals up to 28 GHz. During normal operation, input data (or clock) is transferred to both output channels. Differential input and output signals of the HMC842LC4B are terminated with 50 Ohms to ground on-chip, and may be either AC or DC coupled. The Outputs can b ...

... device can also operate with clock signals up to 28 GHz. During normal operation, input data (or clock) is transferred to both output channels. Differential input and output signals of the HMC842LC4B are terminated with 50 Ohms to ground on-chip, and may be either AC or DC coupled. The Outputs can b ...

2.5 A high-side driver industrial intelligent power switch

... deactivates itself. The following actions are taken: all the output stage is switched off; the signal DIAG2 is activated (active low). Normal operation is resumed as soon as (typically after some seconds) the chip temperature monitored goes back below Θlim-ΘH. The different thresholds with hystereti ...

... deactivates itself. The following actions are taken: all the output stage is switched off; the signal DIAG2 is activated (active low). Normal operation is resumed as soon as (typically after some seconds) the chip temperature monitored goes back below Θlim-ΘH. The different thresholds with hystereti ...

BDTIC TLF502x1EL Step-Down DC/DC-Family

... Infineon offers a new automotive DC/DC-family with ultra low current consumption: TLF502x1EL. ...

... Infineon offers a new automotive DC/DC-family with ultra low current consumption: TLF502x1EL. ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.