ADM1066 数据手册DataSheet 下载

... The ADM1066 Super Sequencer® is a configurable supervisory/ sequencing device that offers a single-chip solution for supply monitoring and sequencing in multiple-supply systems. In addition to these functions, the ADM1066 integrates a 12-bit ADC and six 8-bit voltage output DACs. These circuits can ...

... The ADM1066 Super Sequencer® is a configurable supervisory/ sequencing device that offers a single-chip solution for supply monitoring and sequencing in multiple-supply systems. In addition to these functions, the ADM1066 integrates a 12-bit ADC and six 8-bit voltage output DACs. These circuits can ...

INA301 36-V, High-Speed, Zero-Drift, Voltage-Output, Current

... Overcurrent Protection Power-Supply Protection Circuit Breakers Computers and Servers Telecom Equipment Battery Management ...

... Overcurrent Protection Power-Supply Protection Circuit Breakers Computers and Servers Telecom Equipment Battery Management ...

Analog Devices Welcomes Hittite Microwave Corporation

... at high incident power levels. The device can control signals from DC to 3 GHz and is especially suited for Cellular/3G infrastructure, WiMAX and WiBro applications with only 0.3 dB typical insertion loss. The design provides a 3 watt power handling and +65 dBm third order intercept at +8 Volt bias. ...

... at high incident power levels. The device can control signals from DC to 3 GHz and is especially suited for Cellular/3G infrastructure, WiMAX and WiBro applications with only 0.3 dB typical insertion loss. The design provides a 3 watt power handling and +65 dBm third order intercept at +8 Volt bias. ...

MAX12528 Dual, 80Msps, 12-Bit, IF/Baseband ADC General Description Features

... EVALU E L B AVAILA ...

... EVALU E L B AVAILA ...

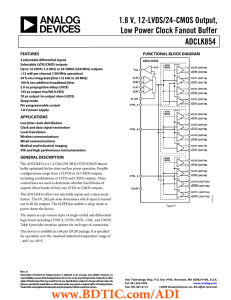

ADCLK854 数据手册DataSheet 下载

... for operation over the standard industrial temperature range of −40°C to +85°C. ...

... for operation over the standard industrial temperature range of −40°C to +85°C. ...

Complete 12-Bit, 25 MSPS Monolithic A/D Converter AD9225

... The AD9225 utilizes a four-stage pipeline architecture with a wideband input sample-and-hold amplifier (SHA) implemented on a cost-effective CMOS process. Each stage of the pipeline, excluding the last stage, consists of a low resolution flash ADC connected to a switched capacitor DAC and interstage ...

... The AD9225 utilizes a four-stage pipeline architecture with a wideband input sample-and-hold amplifier (SHA) implemented on a cost-effective CMOS process. Each stage of the pipeline, excluding the last stage, consists of a low resolution flash ADC connected to a switched capacitor DAC and interstage ...

Raspberry Pi Traffic Light Using an I/O Port Expander

... A typical traffic signal at a major intersection has the usual red-yellow-green lights and a left-turn signal also with red-yellow-green lights/arrows. Although many intersections are asymmetrical as regards turning lanes and timing, for this project we'll limit the number to two symmetrical directi ...

... A typical traffic signal at a major intersection has the usual red-yellow-green lights and a left-turn signal also with red-yellow-green lights/arrows. Although many intersections are asymmetrical as regards turning lanes and timing, for this project we'll limit the number to two symmetrical directi ...

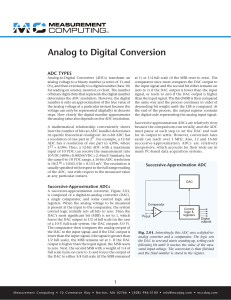

Unit 7 : A/D and D/A Converter

... Fig. 7.2 : Four bit DAC with voltage output. The digital inputs D,C,B, and A are usually derived from the output register of a digital system. The 24 = 16 different binary numbers represented by these 4 bits for each input number, the D/A converter output voltage is a unique value. In fact, for this ...

... Fig. 7.2 : Four bit DAC with voltage output. The digital inputs D,C,B, and A are usually derived from the output register of a digital system. The 24 = 16 different binary numbers represented by these 4 bits for each input number, the D/A converter output voltage is a unique value. In fact, for this ...

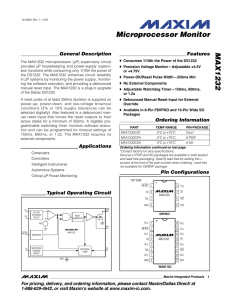

MAX1232 DS

... edges (a high-to-low transition)—the MAX1232 reset outputs are forced to their active states for 250ms (Figure 2). This typically initiates the microprocessor’s power-up routine. If the interruption continues, new reset pulses are generated each timeout period until ST is strobed. The timeout period ...

... edges (a high-to-low transition)—the MAX1232 reset outputs are forced to their active states for 250ms (Figure 2). This typically initiates the microprocessor’s power-up routine. If the interruption continues, new reset pulses are generated each timeout period until ST is strobed. The timeout period ...

Analog Devices Welcomes Hittite Microwave Corporation

... at high incident power levels. The device can control signals from DC to 3 GHz and is especially suited for Cellular/3G infrastructure, WiMAX and WiBro applications with only 0.3 dB typical insertion loss. The design provides a 3 watt power handling and +65 dBm third order intercept at +8 Volt bias. ...

... at high incident power levels. The device can control signals from DC to 3 GHz and is especially suited for Cellular/3G infrastructure, WiMAX and WiBro applications with only 0.3 dB typical insertion loss. The design provides a 3 watt power handling and +65 dBm third order intercept at +8 Volt bias. ...

3 - Texas Instruments

... for their innate ability to resolve an analog input signal to very small LSB voltage ranges. The primarily applications for this type of product is in the Industrial Process Control market such as direct transducer interface for pressure, temperature, flow, weigh scales and force measurement systems ...

... for their innate ability to resolve an analog input signal to very small LSB voltage ranges. The primarily applications for this type of product is in the Industrial Process Control market such as direct transducer interface for pressure, temperature, flow, weigh scales and force measurement systems ...

3.3 V Zero Delay Buffer CY2304 Features

... For applications requiring zero input-output delay, all outputs including the one providing feedback must be equally loaded. If input-output delay adjustments are required, use the graph shown in Figure 2 to calculate loading differences between the feedback output and remaining outputs. For zero ou ...

... For applications requiring zero input-output delay, all outputs including the one providing feedback must be equally loaded. If input-output delay adjustments are required, use the graph shown in Figure 2 to calculate loading differences between the feedback output and remaining outputs. For zero ou ...

PCA9533 1. General description 4-bit I

... When the I/Os are used to control LEDs, they are normally connected to VDD through a resistor as shown in Figure 14. Since the LED acts as a diode, when the LED is off the I/O VI is about 1.2 V less than VDD. The supply current, IDD, increases as VI becomes lower than VDD and is specified as ∆IDD in ...

... When the I/Os are used to control LEDs, they are normally connected to VDD through a resistor as shown in Figure 14. Since the LED acts as a diode, when the LED is off the I/O VI is about 1.2 V less than VDD. The supply current, IDD, increases as VI becomes lower than VDD and is specified as ∆IDD in ...

SMP18

... range but have limited current sinking capability near VSS. In split supply operation, symmetrical output swings can be obtained by restricting the output range to 2 V from either supply. ...

... range but have limited current sinking capability near VSS. In split supply operation, symmetrical output swings can be obtained by restricting the output range to 2 V from either supply. ...

AD549 Ultralow Input Bias Current Operational Amplifier Data Sheet

... current is essentially independent of common-mode voltage. The AD549 is suited for applications requiring very low input current and low input offset voltage. It excels as a preamp for a wide variety of current output transducers, such as photodiodes, photomultiplier tubes, or oxygen sensors. The AD ...

... current is essentially independent of common-mode voltage. The AD549 is suited for applications requiring very low input current and low input offset voltage. It excels as a preamp for a wide variety of current output transducers, such as photodiodes, photomultiplier tubes, or oxygen sensors. The AD ...

SN75LPE185 数据资料 dataSheet 下载

... The device has flexible control options for power management when the serial port is inactive. A common disable for all of the drivers and receivers is provided with the active-low enable (EN) input. The mode-control (MODE) input selects between the STANDBY and WAKE-UP modes. With a low-level input ...

... The device has flexible control options for power management when the serial port is inactive. A common disable for all of the drivers and receivers is provided with the active-low enable (EN) input. The mode-control (MODE) input selects between the STANDBY and WAKE-UP modes. With a low-level input ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.