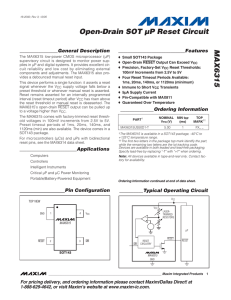

MAX6315 Open-Drain SOT µP Reset Circuit ________________General Description ____________________________Features

... the IC’s VCC pin. However, some systems may use the open-drain output to level-shift from the monitored supply to reset circuitry powered by some other supply (Figure 1). This is one useful feature of an open-drain output. Keep in mind that as the MAX6315’s V CC decreases below 1V, so does the IC’s ...

... the IC’s VCC pin. However, some systems may use the open-drain output to level-shift from the monitored supply to reset circuitry powered by some other supply (Figure 1). This is one useful feature of an open-drain output. Keep in mind that as the MAX6315’s V CC decreases below 1V, so does the IC’s ...

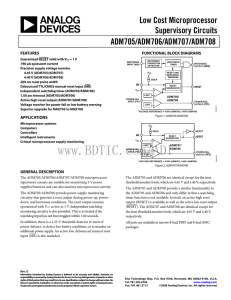

ADM705 数据手册DataSheet 下载

... the microprocessor to check that it is not stalled in an indefinite loop. An output line on the processor is used to toggle the watchdog input (WDI) line. If this line is not toggled within the timeout period (1.60 sec), then the watchdog output (WDO) goes low. The WDO can be connected to a nonmaska ...

... the microprocessor to check that it is not stalled in an indefinite loop. An output line on the processor is used to toggle the watchdog input (WDI) line. If this line is not toggled within the timeout period (1.60 sec), then the watchdog output (WDO) goes low. The WDO can be connected to a nonmaska ...

Watchdog Timer

... The WDP2, WDP1, and WDP0 bits determine the Watchdog Timer prescaling when the Watchdog Timer is enabled. The different prescaling values and their corresponding Timeout Periods are shown on the next slide. ...

... The WDP2, WDP1, and WDP0 bits determine the Watchdog Timer prescaling when the Watchdog Timer is enabled. The different prescaling values and their corresponding Timeout Periods are shown on the next slide. ...

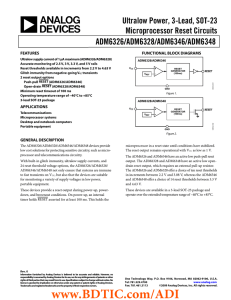

ADM6326 数据手册DataSheet 下载

... active low, open-drain reset output, which requires an external pull-up resistor. The RESET signal is guaranteed to be valid for VCC down to 1 V. When the ADM6326/ADM6328/ADM6346/ADM6348 are powered up, the RESET output remains low for a period typically equal to the RESET active timeout period of 1 ...

... active low, open-drain reset output, which requires an external pull-up resistor. The RESET signal is guaranteed to be valid for VCC down to 1 V. When the ADM6326/ADM6328/ADM6346/ADM6348 are powered up, the RESET output remains low for a period typically equal to the RESET active timeout period of 1 ...

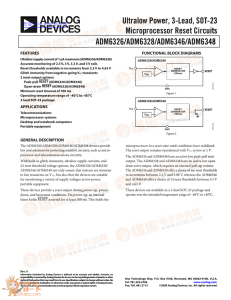

Ultralow Power, 3-Lead, SOT-23 Microprocessor Reset Circuits

... active low, open-drain reset output, which requires an external pull-up resistor. The RESET signal is guaranteed to be valid for VCC down to 1 V. When the ADM6326/ADM6328/ADM6346/ADM6348 are powered up, the RESET output remains low for a period typically equal to the RESET active timeout period of 1 ...

... active low, open-drain reset output, which requires an external pull-up resistor. The RESET signal is guaranteed to be valid for VCC down to 1 V. When the ADM6326/ADM6328/ADM6346/ADM6348 are powered up, the RESET output remains low for a period typically equal to the RESET active timeout period of 1 ...

ADM9690 数据手册DataSheet 下载

... The watchdog timer circuit monitors the activity of the microprocessor in order to check that it is not stalled in an infinite loop. An output line on the processor may be used to toggle the Watchdog Input (WDI) line. If this line is not toggled within the selected timeout period, both RESET outputs ...

... The watchdog timer circuit monitors the activity of the microprocessor in order to check that it is not stalled in an infinite loop. An output line on the processor may be used to toggle the Watchdog Input (WDI) line. If this line is not toggled within the selected timeout period, both RESET outputs ...

AN3261

... The Smart Reset™ devices are designed to meet strict requirements for the lowest possible current consumption and to maintain the common timing constant 10 s/µF, therefore the constant current used to charge the external timing capacitor is very low, in the magnitude of 100 nA. Any external leakage ...

... The Smart Reset™ devices are designed to meet strict requirements for the lowest possible current consumption and to maintain the common timing constant 10 s/µF, therefore the constant current used to charge the external timing capacitor is very low, in the magnitude of 100 nA. Any external leakage ...

Introduction to Embedded System Design Using Field

... updates. The motivation for writing this text is to present a single source of information that can be used to understand how a FPGA and the Hardware Description Language (HDL) can be used in the design of embedded digital systems. Digital design methodology has undergone several changes over the pa ...

... updates. The motivation for writing this text is to present a single source of information that can be used to understand how a FPGA and the Hardware Description Language (HDL) can be used in the design of embedded digital systems. Digital design methodology has undergone several changes over the pa ...

MAX6381XR25D1+T中文资料

... Note:Insert reset threshold suffix (see Reset Threshold table)after "XR", "XS", or "LT." Insert reset timeout delay (see ResetTimeout Delay table) after "D" to complete the part number.Sample stock is generally held on standard versions only (seeStandard Versions table). Standard versions have an or ...

... Note:Insert reset threshold suffix (see Reset Threshold table)after "XR", "XS", or "LT." Insert reset timeout delay (see ResetTimeout Delay table) after "D" to complete the part number.Sample stock is generally held on standard versions only (seeStandard Versions table). Standard versions have an or ...

MAX6340UK16-T中文资料

... system voltages?Monitor System Voltages from 1.6V to 5Vfrom 1.6V to 5V. These devices perform a single function:?Capacitor-Adjustable Reset Timeout Periodthey assert a reset signal whenever the VCCsupply volt-age falls below its reset threshold. The reset output?Low Quiescent Current (1.6?A typ)rema ...

... system voltages?Monitor System Voltages from 1.6V to 5Vfrom 1.6V to 5V. These devices perform a single function:?Capacitor-Adjustable Reset Timeout Periodthey assert a reset signal whenever the VCCsupply volt-age falls below its reset threshold. The reset output?Low Quiescent Current (1.6?A typ)rema ...

Calculating the Capacitor of the Reset Input

... Disclaimer: Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company’s standard warranty which is detailed in Atmel’s Terms and Conditions located on the Company’s web site. The Company assumes no responsibility for any errors which may app ...

... Disclaimer: Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company’s standard warranty which is detailed in Atmel’s Terms and Conditions located on the Company’s web site. The Company assumes no responsibility for any errors which may app ...

Datasheet

... design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are o ...

... design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are o ...

AN1790

... CONCLUSION ST Reset Circuits are low-power supervisory devices, that have been specifically designed to monitor power supplies in microprocessor systems. In standard applications, they can be directly connected to the microprocessor, as no other external circuits are required. However, they can also ...

... CONCLUSION ST Reset Circuits are low-power supervisory devices, that have been specifically designed to monitor power supplies in microprocessor systems. In standard applications, they can be directly connected to the microprocessor, as no other external circuits are required. However, they can also ...

AN-9716 Reset Timers Applications

... device restart. As more device suppliers remove access to the device battery, it has become necessary to provide a more convenient way of forcing a device reset. ...

... device restart. As more device suppliers remove access to the device battery, it has become necessary to provide a more convenient way of forcing a device reset. ...

DSD project

... MCLR to be high. After the time-out period, which is typically 18 ms, it will RESET the reset latch and thus end the on-chip RESET signal. A power-up example where MCLR is not tied to VDD is shown in Figure 5-3. VDD is allowed to rise and stabilize before bringing MCLR high. The chip will actually c ...

... MCLR to be high. After the time-out period, which is typically 18 ms, it will RESET the reset latch and thus end the on-chip RESET signal. A power-up example where MCLR is not tied to VDD is shown in Figure 5-3. VDD is allowed to rise and stabilize before bringing MCLR high. The chip will actually c ...

MAX698/MAX699 Low-Cost, Power-On Reset and Watchdog Controllers General Description

... The MAX698/MAX699 monitor the +5V supply in microprocessor (µP) and digital systems. They supply a RESET pulse of at least 140ms duration on power-up, power-down, and during low-voltage brownout conditions. Circuit reliability is increased at reduced cost by eliminating all external components and a ...

... The MAX698/MAX699 monitor the +5V supply in microprocessor (µP) and digital systems. They supply a RESET pulse of at least 140ms duration on power-up, power-down, and during low-voltage brownout conditions. Circuit reliability is increased at reduced cost by eliminating all external components and a ...

RX Resets - Renesas e

... LVD1RI, LV2RI – Selects interrupt or reset generation for each – 0=Reset, 1=Interrupt Interrupts are NMI’s (set NMIER.LVDEN in the ICU) LVD1 and LVD2 are locked & disabled after reset Lock it after changes with LVDKEYR! LVD Control Register (LVDCR) ...

... LVD1RI, LV2RI – Selects interrupt or reset generation for each – 0=Reset, 1=Interrupt Interrupts are NMI’s (set NMIER.LVDEN in the ICU) LVD1 and LVD2 are locked & disabled after reset Lock it after changes with LVDKEYR! LVD Control Register (LVDCR) ...

An overview of FPGAs: the solution to countless design

... Designers can use a structural view to describe the desired internal implementation, roughly analogous to providing a block diagram. Alternatively, they can use a behavioral view where they treat the system as a black box, and describe overall functionalities and I/O behavior desired. A hardware des ...

... Designers can use a structural view to describe the desired internal implementation, roughly analogous to providing a block diagram. Alternatively, they can use a behavioral view where they treat the system as a black box, and describe overall functionalities and I/O behavior desired. A hardware des ...

Catalog Section

... S.T.A.R.™ programmable delayed reset faulted circuit indicators to quickly and easily locate faulted sections of overhead systems. This faulted circuit indicator (FCI) is designed for use on overhead bare conductors. A long-life lithium battery provides power to indicate the faulted conditions using ...

... S.T.A.R.™ programmable delayed reset faulted circuit indicators to quickly and easily locate faulted sections of overhead systems. This faulted circuit indicator (FCI) is designed for use on overhead bare conductors. A long-life lithium battery provides power to indicate the faulted conditions using ...

Design of JK Flip-Flop using MODFET Technology

... A flip-flop is a bi-stable circuit which stores a logic state of 0 or 1 in response to a clock pulse with one or more data inputs. In digital circuit design, large proportion contributes to synchronous design and they are operated based on the clock signal to reduce the complexity of the circuit des ...

... A flip-flop is a bi-stable circuit which stores a logic state of 0 or 1 in response to a clock pulse with one or more data inputs. In digital circuit design, large proportion contributes to synchronous design and they are operated based on the clock signal to reduce the complexity of the circuit des ...

SmartDesign MSS ACE Simulation

... In the Project Manager Project Flow window click the ModelSim button. In ModelSim's command window type run 3ms. In our example, we are running for 3ms because we have a long hardcoded delay in our testbench, because we want to ensure that the ADC calibration is completed before we begin processing. ...

... In the Project Manager Project Flow window click the ModelSim button. In ModelSim's command window type run 3ms. In our example, we are running for 3ms because we have a long hardcoded delay in our testbench, because we want to ensure that the ADC calibration is completed before we begin processing. ...

EC2357-VLSI DESIGN LABORATORY LABORATORY MANUAL FOR SIXTH SEMESTER B.E (ECE)

... In this section, you will use the FPGA Editor to view the design. You can view your design on the FPGA device, as well as edit the placement and routing with the FPGA Editor. 1. Double-click the View/Edit Routed Design (FPGA Editor) process found in the Place & Route group of processes. Your impleme ...

... In this section, you will use the FPGA Editor to view the design. You can view your design on the FPGA device, as well as edit the placement and routing with the FPGA Editor. 1. Double-click the View/Edit Routed Design (FPGA Editor) process found in the Place & Route group of processes. Your impleme ...

Implementing Keypad Scanners with CoolRunner-II Summary

... In the example shown in Figure 2, there are six bits used to represent the encoded word. Six bits provides 26 or 64 different values each representing a different key. However, one value needs to be used to represent the state when no keys are pressed. Therefore, only 63 keys can be represented in t ...

... In the example shown in Figure 2, there are six bits used to represent the encoded word. Six bits provides 26 or 64 different values each representing a different key. However, one value needs to be used to represent the state when no keys are pressed. Therefore, only 63 keys can be represented in t ...