Atmel LED Driver-MSL1060

... OVP threshold is 2% plus another 1% for the external setting resistors, R8 and R9 (Figure 16 on page 15) reducing the operating maximum voltage to 46.5V. The total voltage needed to drive a string is the forward voltage drop across the desired LED strings, plus the 600mV headroom needed the string’s ...

... OVP threshold is 2% plus another 1% for the external setting resistors, R8 and R9 (Figure 16 on page 15) reducing the operating maximum voltage to 46.5V. The total voltage needed to drive a string is the forward voltage drop across the desired LED strings, plus the 600mV headroom needed the string’s ...

MAX1553/MAX1554 High-Efficiency, 40V Step-Up Converters for 2 to 10 White LEDs General Description

... When large inductor values are used to optimize efficiency, the MAX1553/MAX1554 operate with continuous inductor current. With large inductor values (typically greater than 10µH), stability, input, and output ripple are improved by connecting a capacitor in parallel with the LEDs (C4 in Figures 1, 2 ...

... When large inductor values are used to optimize efficiency, the MAX1553/MAX1554 operate with continuous inductor current. With large inductor values (typically greater than 10µH), stability, input, and output ripple are improved by connecting a capacitor in parallel with the LEDs (C4 in Figures 1, 2 ...

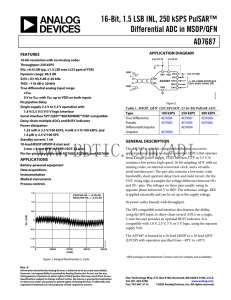

16-Bit, 1.5 LSB INL, 250 kSPS PulSAR™ Differential ADC in MSOP/QFN AD7687

... The AD7687 is a 16-bit, charge redistribution, successive approximation, analog-to-digital converter (ADC) that operates from a single power supply, VDD, between 2.3 V to 5.5 V. It contains a low power, high speed, 16-bit sampling ADC with no missing codes, an internal conversion clock, and a versat ...

... The AD7687 is a 16-bit, charge redistribution, successive approximation, analog-to-digital converter (ADC) that operates from a single power supply, VDD, between 2.3 V to 5.5 V. It contains a low power, high speed, 16-bit sampling ADC with no missing codes, an internal conversion clock, and a versat ...

Complete 12-Bit, 25 MSPS Monolithic A/D Converter AD9225

... The AD9225 utilizes a four-stage pipeline architecture with a wideband input sample-and-hold amplifier (SHA) implemented on a cost-effective CMOS process. Each stage of the pipeline, excluding the last stage, consists of a low resolution flash ADC connected to a switched capacitor DAC and interstage ...

... The AD9225 utilizes a four-stage pipeline architecture with a wideband input sample-and-hold amplifier (SHA) implemented on a cost-effective CMOS process. Each stage of the pipeline, excluding the last stage, consists of a low resolution flash ADC connected to a switched capacitor DAC and interstage ...

MAX1813 Dynamically-Adjustable, Synchronous Step-Down Controller with Integrated Voltage Positioning General Description

... transients while maintaining a relatively constant switching frequency. The MAX1813 is designed specifically for CPU core applications requiring a voltage-positioned supply. The voltage-positioning input (VPCS), combined with a high-DC-accuracy control loop, is used to implement a power supply that ...

... transients while maintaining a relatively constant switching frequency. The MAX1813 is designed specifically for CPU core applications requiring a voltage-positioned supply. The voltage-positioning input (VPCS), combined with a high-DC-accuracy control loop, is used to implement a power supply that ...

BDTIC

... After the PFC stage, there is commonly a PWM stage to provide isolated DC output for end user. Some applications, especially computing, have the holdup time requirement. It means that PWM stage should be able to provide the isolated output even if AC input voltage become zero for a short holdup time ...

... After the PFC stage, there is commonly a PWM stage to provide isolated DC output for end user. Some applications, especially computing, have the holdup time requirement. It means that PWM stage should be able to provide the isolated output even if AC input voltage become zero for a short holdup time ...

71M6541DT/71M6541FT/71M6541GT/ Energy Meter ICs 71M6542FT/71M6542GT General Description

... Our Single Converter Technology® with a 22-bit deltasigma ADC, three or four analog inputs, digital temperature compensation, precision voltage reference, and a 32-bit computation engine (CE) support a wide range of metering applications with very few external components. The 71M654xT devices suppor ...

... Our Single Converter Technology® with a 22-bit deltasigma ADC, three or four analog inputs, digital temperature compensation, precision voltage reference, and a 32-bit computation engine (CE) support a wide range of metering applications with very few external components. The 71M654xT devices suppor ...

$doc.title

... outputs; with pullup resistors, they are compatible with LSTTL outputs. The HC4046A phase–locked loop contains three phase comparators, a voltage–controlled oscillator (VCO) and unity gain op–amp DEM OUT. The comparators have two common signal inputs, COMP IN, and SIG IN. Input SIG IN and COMP IN ca ...

... outputs; with pullup resistors, they are compatible with LSTTL outputs. The HC4046A phase–locked loop contains three phase comparators, a voltage–controlled oscillator (VCO) and unity gain op–amp DEM OUT. The comparators have two common signal inputs, COMP IN, and SIG IN. Input SIG IN and COMP IN ca ...

TRU - JYU Trac Help

... We had to solve some issues with the correct pins in FPGA. We solved it. As far as I understood, it will be not used in final setup. They want to use the black-plane to operate with the board. Second test was the high-speed link. (1 input (40MHz clock from STU, later the LHC clock), 3 output links) ...

... We had to solve some issues with the correct pins in FPGA. We solved it. As far as I understood, it will be not used in final setup. They want to use the black-plane to operate with the board. Second test was the high-speed link. (1 input (40MHz clock from STU, later the LHC clock), 3 output links) ...

20, 40, and 60 Bit I/O Expander with EEPROM

... To read one or more bytes, the master device addresses the unit with a write cycle (= 0) to send AHI followed by ALO, readdresses the unit with a read cycle (= 1), and reads one or more data bytes. Each data byte read increments the internal address counter by one up to the end of the EEPROM address ...

... To read one or more bytes, the master device addresses the unit with a write cycle (= 0) to send AHI followed by ALO, readdresses the unit with a read cycle (= 1), and reads one or more data bytes. Each data byte read increments the internal address counter by one up to the end of the EEPROM address ...

Flip-Flop

... Fig. (1-b) shows the meaning of Set and Reset states in terms of binary voltage levels. To see how F-F operates, refer to Fig. (1-a), Assume that the initial state is the (Set) state (L1 ON and L2 OFF), and that both the Set and Reset lines are low (0). The Set and Reset lines are both stable when ...

... Fig. (1-b) shows the meaning of Set and Reset states in terms of binary voltage levels. To see how F-F operates, refer to Fig. (1-a), Assume that the initial state is the (Set) state (L1 ON and L2 OFF), and that both the Set and Reset lines are low (0). The Set and Reset lines are both stable when ...

Triggering on MIL-STD 1553 Signals

... Other Important Timing Parameters Intermessage Gap: ≥ 4 µs (parity bit crossing to next sync edge) Response Time: 4 to 12 µs (parity bit crossing to next sync edge) ...

... Other Important Timing Parameters Intermessage Gap: ≥ 4 µs (parity bit crossing to next sync edge) Response Time: 4 to 12 µs (parity bit crossing to next sync edge) ...

A8586, A8586-1, A8586-2: Wide Input Voltage, Adjustable

... error amplifier performs an analog OR selection between them; it regulates to either the soft-start voltage or the A8586 internal reference (VREF), whichever is lower. To stabilize the regulator, a series RC compensation network (RZ CZ) must be connected from the error amplifier output (COMP pin) to ...

... error amplifier performs an analog OR selection between them; it regulates to either the soft-start voltage or the A8586 internal reference (VREF), whichever is lower. To stabilize the regulator, a series RC compensation network (RZ CZ) must be connected from the error amplifier output (COMP pin) to ...

MAX8500–MAX8504 PWM Buck Converters with Bypass FET for N-CDMA/W-CDMA Handsets General Description

... output voltage by switching at a constant frequency and then modulating the duty cycle with PWM control. The error-amp output, the main switch current-sense signal, and the slope compensation ramp are all summed using a PWM comparator. The comparator modulates the output power by adjusting the peak ...

... output voltage by switching at a constant frequency and then modulating the duty cycle with PWM control. The error-amp output, the main switch current-sense signal, and the slope compensation ramp are all summed using a PWM comparator. The comparator modulates the output power by adjusting the peak ...

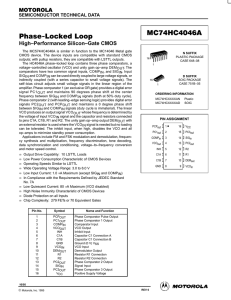

Phase-Locked Loop MC74HC4046A

... outputs; with pullup resistors, they are compatible with LSTTL outputs. The HC4046A phase–locked loop contains three phase comparators, a voltage–controlled oscillator (VCO) and unity gain op–amp DEM OUT. The comparators have two common signal inputs, COMP IN, and SIG IN. Input SIG IN and COMP IN ca ...

... outputs; with pullup resistors, they are compatible with LSTTL outputs. The HC4046A phase–locked loop contains three phase comparators, a voltage–controlled oscillator (VCO) and unity gain op–amp DEM OUT. The comparators have two common signal inputs, COMP IN, and SIG IN. Input SIG IN and COMP IN ca ...

AS4C64M16D2-25BAN 1Gb DDR2_A-Grade 2

... latency, burst length, burst sequence, test mode, DLL reset, WR, and various vendor specific options to make DDR2 SDRAM useful for various applications.The default value of the mode register is not defined, therefore the mode register must be programmed during initialization for proper operation. Th ...

... latency, burst length, burst sequence, test mode, DLL reset, WR, and various vendor specific options to make DDR2 SDRAM useful for various applications.The default value of the mode register is not defined, therefore the mode register must be programmed during initialization for proper operation. Th ...

ADP5020 英文数据手册DataSheet 下载

... The ADP5020 provides a highly integrated power solution that includes all of the power circuits necessary for a digital imaging module. It comprises two step-down dc-to-dc converters, one LDO, and a power sequence controller. All dc-to-dc converters integrate power pMOSFETs and nMOSFETs, making the ...

... The ADP5020 provides a highly integrated power solution that includes all of the power circuits necessary for a digital imaging module. It comprises two step-down dc-to-dc converters, one LDO, and a power sequence controller. All dc-to-dc converters integrate power pMOSFETs and nMOSFETs, making the ...

Introduction to Basic Electronic Components

... electronic devices. It is a type of microprocessor emphasizing selfsufficiency and cost-effectiveness, in contrast to a general-purpose microprocessor, the kind used in a PC. A typical microcontroller contains all the memory and I/O interfaces needed, whereas a general purpose microprocessor require ...

... electronic devices. It is a type of microprocessor emphasizing selfsufficiency and cost-effectiveness, in contrast to a general-purpose microprocessor, the kind used in a PC. A typical microcontroller contains all the memory and I/O interfaces needed, whereas a general purpose microprocessor require ...