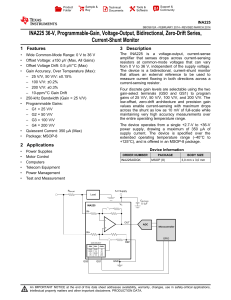

36-V, Prog.-Gain, Voltage-Output, Bidir, Zero

... The device operates from a single +2.7-V to +36-V power supply, drawing a maximum of 350 μA of supply current. The device is specified over the extended operating temperature range (–40°C to +125°C), and is offered in an MSOP-8 package. ...

... The device operates from a single +2.7-V to +36-V power supply, drawing a maximum of 350 μA of supply current. The device is specified over the extended operating temperature range (–40°C to +125°C), and is offered in an MSOP-8 package. ...

LT1937 - Linear Technology

... The LT1937 uses a constant frequency, current mode control scheme to provide excellent line and load regulation. Operation can be best understood by referring to the block diagram in Figure 2. At the start of each oscillator cycle, the SR latch is set, which turns on the power switch Q1. A voltage p ...

... The LT1937 uses a constant frequency, current mode control scheme to provide excellent line and load regulation. Operation can be best understood by referring to the block diagram in Figure 2. At the start of each oscillator cycle, the SR latch is set, which turns on the power switch Q1. A voltage p ...

UCC2813-0-Q1 数据资料 dataSheet 下载

... sense comparator during the 100 ns interval immediately following the rising edge of the OUT pin. This digital filtering, also called leading-edge blanking, means that in most applications, no analog filtering (RC filter) is required on CS. Compared to an external RC filter technique, the leading-ed ...

... sense comparator during the 100 ns interval immediately following the rising edge of the OUT pin. This digital filtering, also called leading-edge blanking, means that in most applications, no analog filtering (RC filter) is required on CS. Compared to an external RC filter technique, the leading-ed ...

AD8628

... amplifiers. Using Analog Devices, Inc., topology, these zerodrift amplifiers combine low cost with high accuracy and low noise. No external capacitor is required. In addition, the AD8628/ AD8629/AD8630 greatly reduce the digital switching noise found in most chopper-stabilized amplifiers. With an of ...

... amplifiers. Using Analog Devices, Inc., topology, these zerodrift amplifiers combine low cost with high accuracy and low noise. No external capacitor is required. In addition, the AD8628/ AD8629/AD8630 greatly reduce the digital switching noise found in most chopper-stabilized amplifiers. With an of ...

MAX5101 +2.7V to +5.5V, Low-Power, Triple, Parallel General Description

... Note 1: Reduced digital code range (code 00 hex to code F0 hex) due to swing limitations when the output amplifier is loaded. Note 2: Gain error is: [100 (VF0,meas - ZCE - VF0,ideal) / VDD]. Where VF0,meas is the DAC output voltage with input code F0 hex, and VF0,ideal is the ideal DAC output voltag ...

... Note 1: Reduced digital code range (code 00 hex to code F0 hex) due to swing limitations when the output amplifier is loaded. Note 2: Gain error is: [100 (VF0,meas - ZCE - VF0,ideal) / VDD]. Where VF0,meas is the DAC output voltage with input code F0 hex, and VF0,ideal is the ideal DAC output voltag ...

IDT74FCT20807 2.5V CMOS 1-TO

... non-inverting clock buffer. The large fanout from a single input reduces loading on the preceding driver and provides an efficient clock distribution network. Providing output to output skew as low as 150ps, the FCT20807 is an ideal clock distribution device for synchronous systems. Multiple power a ...

... non-inverting clock buffer. The large fanout from a single input reduces loading on the preceding driver and provides an efficient clock distribution network. Providing output to output skew as low as 150ps, the FCT20807 is an ideal clock distribution device for synchronous systems. Multiple power a ...

Si53315 - Silicon Labs

... The Si53315 has highly flexible output drivers that support a wide range of clock signal formats, including LVPECL, low power LVPECL, LVDS, CML, HCSL, and LVCMOS. SFOUT[0] and SFOUT[1] are 3-level inputs that can be pin-strapped to select the clock signal formats for all of the outputs, Q0 through Q ...

... The Si53315 has highly flexible output drivers that support a wide range of clock signal formats, including LVPECL, low power LVPECL, LVDS, CML, HCSL, and LVCMOS. SFOUT[0] and SFOUT[1] are 3-level inputs that can be pin-strapped to select the clock signal formats for all of the outputs, Q0 through Q ...

MAX3264

... deterministic jitter. The output buffer produces a limited output signal. The MAX3264/MAX3265/MAX3765 produce a CML output, while the MAX3268/MAX3269/ MAX3768 produce a PECL-compatible output signal. Schematics of these input/output circuits are shown in Figures 4 through 7. ...

... deterministic jitter. The output buffer produces a limited output signal. The MAX3264/MAX3265/MAX3765 produce a CML output, while the MAX3268/MAX3269/ MAX3768 produce a PECL-compatible output signal. Schematics of these input/output circuits are shown in Figures 4 through 7. ...

performance analysis of sssc based on 48 pulse vsc

... The SSSC is a series FACTS device that produces with appropriate control system, a balanced set of three-phase controllable voltages which are in quadrature with the transmission line current. The SSSC has two mode of operation. If SSSC voltage is function of the transmission line current, the SSSC ...

... The SSSC is a series FACTS device that produces with appropriate control system, a balanced set of three-phase controllable voltages which are in quadrature with the transmission line current. The SSSC has two mode of operation. If SSSC voltage is function of the transmission line current, the SSSC ...

IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) e-ISSN: 2278-1676,p-ISSN: 2320-3331,

... from the network and the network is supplied form the line side. When the line side circuit breaker is opened, a value of voltage is transferred to bus-bar through a capacitor which is paralleled with circuit breaker. The voltage value that is produced on bus-bar will be less than the primary voltag ...

... from the network and the network is supplied form the line side. When the line side circuit breaker is opened, a value of voltage is transferred to bus-bar through a capacitor which is paralleled with circuit breaker. The voltage value that is produced on bus-bar will be less than the primary voltag ...

THS7315 数据资料 dataSheet 下载

... This rationale is also used for the chroma (C') term. Chroma is derived from the nonlinear R'G'B' terms and therefore it is also nonlinear. True chominance (C) is derived from linear RGB, and thus the difference between chroma (C') and chrominance (C) exists. The color difference signals (P'B/ P'R/U ...

... This rationale is also used for the chroma (C') term. Chroma is derived from the nonlinear R'G'B' terms and therefore it is also nonlinear. True chominance (C) is derived from linear RGB, and thus the difference between chroma (C') and chrominance (C) exists. The color difference signals (P'B/ P'R/U ...

AAT2552 数据资料DataSheet下载

... The battery charger is a complete constant current/constant voltage linear charger. It offers an integrated pass device, reverse blocking protection, high accuracy current and voltage regulation, charge status, and charge termination. The charging current is programmable via external resistor from 3 ...

... The battery charger is a complete constant current/constant voltage linear charger. It offers an integrated pass device, reverse blocking protection, high accuracy current and voltage regulation, charge status, and charge termination. The charging current is programmable via external resistor from 3 ...

8-Bit, 250 MSPS 3.3 V A/D Converter AD9480

... and subtracting the voltage from the other pin, which is 180° out of phase. Peak-to-peak differential is computed by rotating the inputs phase 180° and taking the peak measurement again. The difference is then computed between both peak measurements. Differential Nonlinearity The deviation of any co ...

... and subtracting the voltage from the other pin, which is 180° out of phase. Peak-to-peak differential is computed by rotating the inputs phase 180° and taking the peak measurement again. The difference is then computed between both peak measurements. Differential Nonlinearity The deviation of any co ...

THE 555 IC TIMER • The 555 IC TIMER

... possibilities such as using the timer as a voltage-controlled oscillator, pulse-width modulator, etc. For applications where the control it is strongly recommended that a bypass capacitor (0.01uF) be placed across the control voltage pin and ground. This will increase the noise immunity of the timer ...

... possibilities such as using the timer as a voltage-controlled oscillator, pulse-width modulator, etc. For applications where the control it is strongly recommended that a bypass capacitor (0.01uF) be placed across the control voltage pin and ground. This will increase the noise immunity of the timer ...

CAT4201 - 350 mA High Efficiency Step Down LED Driver

... A 10 mF ceramic capacitor C2 across the LED(s) keeps the LED ripple current within ±15% of nominal for most applications. If needed, a larger capacitor can be used to further reduce the LED current ripple. Any resistance in series with the LED (0.5 W or more) contributes to reduce the ripple current ...

... A 10 mF ceramic capacitor C2 across the LED(s) keeps the LED ripple current within ±15% of nominal for most applications. If needed, a larger capacitor can be used to further reduce the LED current ripple. Any resistance in series with the LED (0.5 W or more) contributes to reduce the ripple current ...

Integrating ADC

An integrating ADC is a type of analog-to-digital converter that converts an unknown input voltage into a digital representation through the use of an integrator. In its most basic implementation, the unknown input voltage is applied to the input of the integrator and allowed to ramp for a fixed time period (the run-up period). Then a known reference voltage of opposite polarity is applied to the integrator and is allowed to ramp until the integrator output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times allow for higher resolutions. Likewise, the speed of the converter can be improved by sacrificing resolution.Converters of this type can achieve high resolution, but often do so at the expense of speed. For this reason, these converters are not found in audio or signal processing applications. Their use is typically limited to digital voltmeters and other instruments requiring highly accurate measurements.