MAX847 1-Cell, Step-Up Two-Way Pager System IC ________________General Description

... This is not a tested parameter, since the IC is powered from OUT, not BATT. The only limitation in the BATT range is the inability to generate more than 5 times, or less than 1.15 times the BATT voltage at OUT. This is due to PWM controller duty-cycle limitations in Run Mode. Minimum start-up voltag ...

... This is not a tested parameter, since the IC is powered from OUT, not BATT. The only limitation in the BATT range is the inability to generate more than 5 times, or less than 1.15 times the BATT voltage at OUT. This is due to PWM controller duty-cycle limitations in Run Mode. Minimum start-up voltag ...

lab-manual-electronic-devices-and

... than that of the half wave rectifier producing a smoother output waveform. In a Full Wave Rectifier circuit two diodes are now used, one for each half of the cycle. A transformer is used whose secondary winding is split equally into two halves with a common centre tapped connection, (C). This config ...

... than that of the half wave rectifier producing a smoother output waveform. In a Full Wave Rectifier circuit two diodes are now used, one for each half of the cycle. A transformer is used whose secondary winding is split equally into two halves with a common centre tapped connection, (C). This config ...

UQQ-5/20-Q48N-C Datasheet

... (10) Regulation specifications describe the deviation as the line input voltage or output load current is varied from a nominal midpoint value to either extreme. (11) Alternate pin length and/or other output voltages are available under special quantity order. (12) Overvoltage shutdown on 48V input m ...

... (10) Regulation specifications describe the deviation as the line input voltage or output load current is varied from a nominal midpoint value to either extreme. (11) Alternate pin length and/or other output voltages are available under special quantity order. (12) Overvoltage shutdown on 48V input m ...

Dual Wideband, High Output Current Operational Amplifier with

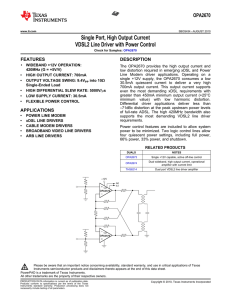

... The OPA2670 provides the high output current and low distortion required in emerging xDSL and Power Line Modem driver applications. Operating on a single +12V supply, the OPA2670 consumes a low 30.5mA quiescent current to deliver a very high 700mA output current. This output current supports even th ...

... The OPA2670 provides the high output current and low distortion required in emerging xDSL and Power Line Modem driver applications. Operating on a single +12V supply, the OPA2670 consumes a low 30.5mA quiescent current to deliver a very high 700mA output current. This output current supports even th ...

UCC28220 数据资料 dataSheet 下载

... frequency and maximum duty cycle. Under normal operation the dc voltage on this pin is 2.5 V. DISCHG: A resistor from this pin to GND sets up the discharge current of the internal CT capacitor used in the oscillator. This resistor, in conjunction with the resistor on the CHG pin is used to set up th ...

... frequency and maximum duty cycle. Under normal operation the dc voltage on this pin is 2.5 V. DISCHG: A resistor from this pin to GND sets up the discharge current of the internal CT capacitor used in the oscillator. This resistor, in conjunction with the resistor on the CHG pin is used to set up th ...

MAX1005 IF Undersampler _______________General Description ____________________________Features

... Note 2: fIN = 4.3MHz digital sine wave applied to DAC data inputs; fCLK = 15MHz. The reference frequency (fREF) is defined to be 10.7MHz (fCLK - fIN). All frequency components present in the DAC output waveform except for fREF and fIN are considered spurious. Note 3: For DAC SFDR measurements, the a ...

... Note 2: fIN = 4.3MHz digital sine wave applied to DAC data inputs; fCLK = 15MHz. The reference frequency (fREF) is defined to be 10.7MHz (fCLK - fIN). All frequency components present in the DAC output waveform except for fREF and fIN are considered spurious. Note 3: For DAC SFDR measurements, the a ...

1. Study of OP AMPs - IC 741, IC 555, IC 565, IC 566, IC 1496

... Vec/3 triggers the output goes to High. The amplitude of the pulse should be able to make the comparator (inside the IC) change its state. However the width of the negative going pulse must not be greater than the width of the expected output pulse. Pin (3) is the output terminal of IC 555. There ar ...

... Vec/3 triggers the output goes to High. The amplitude of the pulse should be able to make the comparator (inside the IC) change its state. However the width of the negative going pulse must not be greater than the width of the expected output pulse. Pin (3) is the output terminal of IC 555. There ar ...

comparison of electric springs with statcom for flc based

... point of common coupling (PCC) connection is compared. In this paper, it turns out that a group of ESs achieves better total voltage regulation than STATCOM with less overall reactive power capacity. Dependence of the ES capability on proportion of critical and NC load is also shown. Here we are usi ...

... point of common coupling (PCC) connection is compared. In this paper, it turns out that a group of ESs achieves better total voltage regulation than STATCOM with less overall reactive power capacity. Dependence of the ES capability on proportion of critical and NC load is also shown. Here we are usi ...

RAJ240500

... Charge block detection circuit (Input power supply, over voltage/over current detection ,Output over voltage/over current detection , Input-output voltage difference detection) Power supply voltage : VCC_FG = 2.0 to 25 V/VCC_CHG=4.5V to 25V. Operation ambient temperature : TA = -20 to ...

... Charge block detection circuit (Input power supply, over voltage/over current detection ,Output over voltage/over current detection , Input-output voltage difference detection) Power supply voltage : VCC_FG = 2.0 to 25 V/VCC_CHG=4.5V to 25V. Operation ambient temperature : TA = -20 to ...

74ALVC162244 Low Voltage 16-Bit Buffer/Line Driver with 3.6V Tolerant Inputs and Outputs

... with 3-STATE outputs to be employed as a memory and address driver, clock driver, or bus oriented transmitter/ receiver. The device is nibble (4-bit) controlled. Each nibble has separate 3-STATE control inputs which can be shorted together for full 16-bit operation. The 74ALVC162244 is designed for ...

... with 3-STATE outputs to be employed as a memory and address driver, clock driver, or bus oriented transmitter/ receiver. The device is nibble (4-bit) controlled. Each nibble has separate 3-STATE control inputs which can be shorted together for full 16-bit operation. The 74ALVC162244 is designed for ...

New Simple Square-Rooting Circuits Based on Translinear Current Conveyors Chuachai Netbut Montree Kumngern

... Two new square-rooting circuits based on second-generation current-controlled current conveyors (CCCIIs) are presented. The first square-rooting circuit consists of two CCCIIs, one current-controlled resistor and two grounded resistors. The input signal of the first circuit is a voltage, and output ...

... Two new square-rooting circuits based on second-generation current-controlled current conveyors (CCCIIs) are presented. The first square-rooting circuit consists of two CCCIIs, one current-controlled resistor and two grounded resistors. The input signal of the first circuit is a voltage, and output ...

NSD-2101

... voltage. Typical system power dissipation can be reduced down to 25% of standard full-bridge drive. When VDD is higher than 5.0V only half bridge mode should be used to avoid exceeding max total power dissipation of 1W. A typical hysteresis of 100mV is implemented to increase ...

... voltage. Typical system power dissipation can be reduced down to 25% of standard full-bridge drive. When VDD is higher than 5.0V only half bridge mode should be used to avoid exceeding max total power dissipation of 1W. A typical hysteresis of 100mV is implemented to increase ...

a 14-Bit, 125 MSPS TxDAC D/A Converter

... Differential current outputs are provided to support singleended or differential applications. Matching between the two current outputs ensures enhanced dynamic performance in a differential output configuration. The current outputs may be tied directly to an output resistor to provide two complemen ...

... Differential current outputs are provided to support singleended or differential applications. Matching between the two current outputs ensures enhanced dynamic performance in a differential output configuration. The current outputs may be tied directly to an output resistor to provide two complemen ...

Dual Wideband, Current-Feedback OPERATIONAL AMPLIFIER With Disable FEATURES APPLICATIONS

... The OPA2691 sets a new level of performance for broadband dual current-feedback op amps. Operating on a very low 5.1mA/ch supply current, the OPA2691 offers a slew rate and output power normally associated with a much higher supply current. A new output stage architecture delivers a high output curr ...

... The OPA2691 sets a new level of performance for broadband dual current-feedback op amps. Operating on a very low 5.1mA/ch supply current, the OPA2691 offers a slew rate and output power normally associated with a much higher supply current. A new output stage architecture delivers a high output curr ...

ELECTRICAL MEASUREMENTS LAB

... Dissipation factor for the capacitors are D1 = tan δ1 =ω C1r1 and D2 = tan δ2 =ω C2r2 D2 – D1 = ω C2(R1R4/R3 – R2) Therefore, if the dissipation factor of one of the capacitors is known, the dissipation factor for the other can be determined. ...

... Dissipation factor for the capacitors are D1 = tan δ1 =ω C1r1 and D2 = tan δ2 =ω C2r2 D2 – D1 = ω C2(R1R4/R3 – R2) Therefore, if the dissipation factor of one of the capacitors is known, the dissipation factor for the other can be determined. ...

POWER SUPPLY MONITOR

... Detection voltage inputs A and B are connected to the inverting input of Comparators A and B respectively. Both comparators have built-in hysterisis. If either VSA or VSB drops lower than about 1.23V, then RESET goes low. Comparator B is used for the arbitrary preset voltage detection (See Example 3 ...

... Detection voltage inputs A and B are connected to the inverting input of Comparators A and B respectively. Both comparators have built-in hysterisis. If either VSA or VSB drops lower than about 1.23V, then RESET goes low. Comparator B is used for the arbitrary preset voltage detection (See Example 3 ...

Integrating ADC

An integrating ADC is a type of analog-to-digital converter that converts an unknown input voltage into a digital representation through the use of an integrator. In its most basic implementation, the unknown input voltage is applied to the input of the integrator and allowed to ramp for a fixed time period (the run-up period). Then a known reference voltage of opposite polarity is applied to the integrator and is allowed to ramp until the integrator output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times allow for higher resolutions. Likewise, the speed of the converter can be improved by sacrificing resolution.Converters of this type can achieve high resolution, but often do so at the expense of speed. For this reason, these converters are not found in audio or signal processing applications. Their use is typically limited to digital voltmeters and other instruments requiring highly accurate measurements.