General Description Benefits and Features

... the gain exceeds the GBW, the gain drop starts earlier at the location where the loop gain is limited. This situation applies typically to an output voltage less than 1.8V, so zero frequency from the ESR is needed to increase the phase margin at the crossover frequency. The recommended relationship ...

... the gain exceeds the GBW, the gain drop starts earlier at the location where the loop gain is limited. This situation applies typically to an output voltage less than 1.8V, so zero frequency from the ESR is needed to increase the phase margin at the crossover frequency. The recommended relationship ...

High PSRR, Low-Noise, 1-A Power Filter (Rev. B)

... Enable pin. Driving EN high turns on the device (if driven low, EN turns off the device). EN must not be left floating and can be connected to IN if not used. ...

... Enable pin. Driving EN high turns on the device (if driven low, EN turns off the device). EN must not be left floating and can be connected to IN if not used. ...

AD7840 数据手册DataSheet 下载

... in conjunction with WR to load parallel data to the input latch. For applications where CS is permanently low, an R, C is required for correct power-up (see LDAC input). If this input is tied to VSS, it defines the AD7840 for serial mode operation. Write/Frame Synchronization Input. In the parallel ...

... in conjunction with WR to load parallel data to the input latch. For applications where CS is permanently low, an R, C is required for correct power-up (see LDAC input). If this input is tied to VSS, it defines the AD7840 for serial mode operation. Write/Frame Synchronization Input. In the parallel ...

MAX1110/MAX1111 +2.7V, Low-Power, Multichannel, Serial 8-Bit ADCs General Description

... The T/H enters its tracking mode on the falling clock edge after the sixth bit of the 8-bit control byte has been shifted in. It enters its hold mode on the falling clock edge after the eighth bit of the control byte has been shifted in. If the converter is set up for singleended inputs, IN- is conn ...

... The T/H enters its tracking mode on the falling clock edge after the sixth bit of the 8-bit control byte has been shifted in. It enters its hold mode on the falling clock edge after the eighth bit of the control byte has been shifted in. If the converter is set up for singleended inputs, IN- is conn ...

MAX1820/MAX1821 WCDMA Cellular Phone 600mA Buck Regulators General Description

... supply voltage range is from 2.6V to 5.5V, and the guaranteed output current is 600mA; 1MHz PWM switching allows for small external components, while skip mode reduces quiescent current to 180µA with light loads. The MAX1820 is dynamically controlled to provide varying output voltages from 0.4V to 3 ...

... supply voltage range is from 2.6V to 5.5V, and the guaranteed output current is 600mA; 1MHz PWM switching allows for small external components, while skip mode reduces quiescent current to 180µA with light loads. The MAX1820 is dynamically controlled to provide varying output voltages from 0.4V to 3 ...

Current Switching with High Voltage Air Disconnector

... The result of measurements has shown that high frequency voltages on busbars occur with amplitudes up to 1.16 p.u. (233 kVpeak) and the dominant frequencies up to 0.6 MHz. The difference between magnitudes of measured and calculated overvoltages is 5 % and 15.6 % on frequency. Measured common mode v ...

... The result of measurements has shown that high frequency voltages on busbars occur with amplitudes up to 1.16 p.u. (233 kVpeak) and the dominant frequencies up to 0.6 MHz. The difference between magnitudes of measured and calculated overvoltages is 5 % and 15.6 % on frequency. Measured common mode v ...

MAX887 100% Duty Cycle, Low-Noise, Step-Down, PWM DC-DC Converter _______________General Description

... data-sampling frequencies. A minimum load is not required during forced PWM operation, since the synchronous rectifier passes reverse inductor current as needed to allow constant-frequency operation with no load. Connecting SYNC to GND enables Idle Mode operation. This proprietary control scheme pla ...

... data-sampling frequencies. A minimum load is not required during forced PWM operation, since the synchronous rectifier passes reverse inductor current as needed to allow constant-frequency operation with no load. Connecting SYNC to GND enables Idle Mode operation. This proprietary control scheme pla ...

DEP_2

... (Because this was performed on the Tektronix 576 a picture could not be obtained of the curve.) The data obtained from the same setup on the Textronix TDS2024 DSO was used to extrapolate the data to determine IS and n. Voltage (V) ...

... (Because this was performed on the Tektronix 576 a picture could not be obtained of the curve.) The data obtained from the same setup on the Textronix TDS2024 DSO was used to extrapolate the data to determine IS and n. Voltage (V) ...

ML15.121 - PULS Power Supply

... office, communication, and instrumentation equipment. Do not use this power supply in equipment, where malfunction may cause severe personal injury or threaten human life. ...

... office, communication, and instrumentation equipment. Do not use this power supply in equipment, where malfunction may cause severe personal injury or threaten human life. ...

MAX1630–MAX1635 Multi-Output, Low-Noise Power-Supply Controllers for Notebook Computers ________________General Description

... Note 2: High duty-factor operation supports low input-to-output differential voltages, and is achieved at a lowered operating frequency (see Overload and Dropout Operation section). Note 3: MAX1630/MAX1632/MAX1633/MAX1635 only. Note 4: Off mode for the 12V linear regulator occurs when the SMPS that ...

... Note 2: High duty-factor operation supports low input-to-output differential voltages, and is achieved at a lowered operating frequency (see Overload and Dropout Operation section). Note 3: MAX1630/MAX1632/MAX1633/MAX1635 only. Note 4: Off mode for the 12V linear regulator occurs when the SMPS that ...

LT6604-2.5

... the input current should be limited to less than 10mA. In addition, the inputs +IN, –IN are protected by a pair of back-to-back diodes. If the differential input voltage exceeds 1.4V, the input current should be limited to less than 10mA Note 9: Channel separation (the inverse of crosstalk) is measu ...

... the input current should be limited to less than 10mA. In addition, the inputs +IN, –IN are protected by a pair of back-to-back diodes. If the differential input voltage exceeds 1.4V, the input current should be limited to less than 10mA Note 9: Channel separation (the inverse of crosstalk) is measu ...

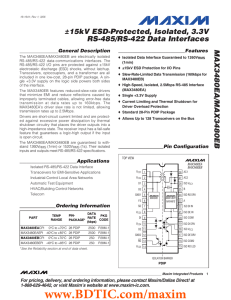

MAX3480EA/MAX3480EB ±15kV ESD-Protected, Isolated, 3.3V RS-485/RS-422 Data Interfaces General Description

... Transceivers, optocouplers, and a transformer are all included in one low-cost, 28-pin PDIP package. A single +3.3V supply on the logic side powers both sides of the interface. The MAX3480EB features reduced-slew-rate drivers that minimize EMI and reduce reflections caused by improperly terminated c ...

... Transceivers, optocouplers, and a transformer are all included in one low-cost, 28-pin PDIP package. A single +3.3V supply on the logic side powers both sides of the interface. The MAX3480EB features reduced-slew-rate drivers that minimize EMI and reduce reflections caused by improperly terminated c ...

Low-Power Signal Conditioning for a Pressure

... The VOCM pin can be connected to a data converter reference voltage pin to achieve tight tracking between the op-amp common mode voltage and the data converter common mode voltage. In this application, the data converter also provides a free dc level conversion for single supply circuits. The common ...

... The VOCM pin can be connected to a data converter reference voltage pin to achieve tight tracking between the op-amp common mode voltage and the data converter common mode voltage. In this application, the data converter also provides a free dc level conversion for single supply circuits. The common ...

TLD1120EL Data Sheet - Infineon Technologies

... The EN pin can be used to supply the internal logic. There are two typical application conditions, where this feature can be used: 1) In “DC/DC control Buck” configurations, where the voltage Vs can be below 5.5V. 2) In configurations, where a PWM signal is applied at the Vbatt pin of a light module ...

... The EN pin can be used to supply the internal logic. There are two typical application conditions, where this feature can be used: 1) In “DC/DC control Buck” configurations, where the voltage Vs can be below 5.5V. 2) In configurations, where a PWM signal is applied at the Vbatt pin of a light module ...

Analysis on an NPN Common-Emitter Amplifier

... forward biased diode will not start conducting current until the potential across it reaches about 0.6V. This is referred to as the turn-on voltage. When applying an AC voltage to a diode, the diode will be forward biased for half of the AC cycle and reverse biased for the other half. When analyzing ...

... forward biased diode will not start conducting current until the potential across it reaches about 0.6V. This is referred to as the turn-on voltage. When applying an AC voltage to a diode, the diode will be forward biased for half of the AC cycle and reverse biased for the other half. When analyzing ...

3.3-V/5-V Multichannel RS-232 Line Driver/Receiver (Rev. D

... The SN75LV4737A‡ consists of three line drivers, five line receivers, and a charge-pump circuit. It provides the electrical interface between an asynchronous communication controller and the serial-port connector, and meets the requirements of TIA/EIA-232-F. This combination of drivers and receivers ...

... The SN75LV4737A‡ consists of three line drivers, five line receivers, and a charge-pump circuit. It provides the electrical interface between an asynchronous communication controller and the serial-port connector, and meets the requirements of TIA/EIA-232-F. This combination of drivers and receivers ...

HIN202, HIN206, HIN207, HIN208, HIN211, HIN213

... Figure 1. The charge pump contains two sections: the voltage doubler and the voltage inverter. Each section is driven by a two phase, internally generated clock to generate +10V and -10V. The nominal clock frequency is 125kHz. During phase one of the clock, capacitor C1 is charged to VCC . During ph ...

... Figure 1. The charge pump contains two sections: the voltage doubler and the voltage inverter. Each section is driven by a two phase, internally generated clock to generate +10V and -10V. The nominal clock frequency is 125kHz. During phase one of the clock, capacitor C1 is charged to VCC . During ph ...

A-156 System A - 100 1. Introduction QNT

... by the quantizer, e.g. only notes from a major scale. Another typical application is shown in fig. 8: using the Quantizer A-156 with the Analog/Trigger Sequenzer A-155. The upper sequencer generates an 8-note sequence. The voltage "Pre Out 1" controls the VCO pitch and is processed by the quantizer ...

... by the quantizer, e.g. only notes from a major scale. Another typical application is shown in fig. 8: using the Quantizer A-156 with the Analog/Trigger Sequenzer A-155. The upper sequencer generates an 8-note sequence. The voltage "Pre Out 1" controls the VCO pitch and is processed by the quantizer ...

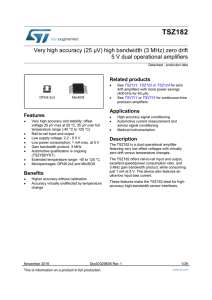

Very high accuracy (25 µV) high bandwidth (3 MHz) zero drift 5 V

... Equivalent input noise voltage density ...

... Equivalent input noise voltage density ...

Module 5.3

... either case the nameplate voltage and current are always VLine and ILine . The power can be given in either KW or KVA. While the generator voltage and frequency are kept relatively constant, the current and power outputs change according to load demand changes. ...

... either case the nameplate voltage and current are always VLine and ILine . The power can be given in either KW or KVA. While the generator voltage and frequency are kept relatively constant, the current and power outputs change according to load demand changes. ...

Integrating ADC

An integrating ADC is a type of analog-to-digital converter that converts an unknown input voltage into a digital representation through the use of an integrator. In its most basic implementation, the unknown input voltage is applied to the input of the integrator and allowed to ramp for a fixed time period (the run-up period). Then a known reference voltage of opposite polarity is applied to the integrator and is allowed to ramp until the integrator output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times allow for higher resolutions. Likewise, the speed of the converter can be improved by sacrificing resolution.Converters of this type can achieve high resolution, but often do so at the expense of speed. For this reason, these converters are not found in audio or signal processing applications. Their use is typically limited to digital voltmeters and other instruments requiring highly accurate measurements.