8413S12BI-126 - Integrated Device Technology

... NOTE: All HCSL output banks running at 100MHz. NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specificat ...

... NOTE: All HCSL output banks running at 100MHz. NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specificat ...

Analog to Digital Converters (ADC)

... counter, costing considerable time. This type of ADC is therefore unsuitable for rapidly changing analog input. ◊ Each clocking pulse increments the counter by one. It takes (2N-1) clock cycles times the clock period for an output to be produced. ...

... counter, costing considerable time. This type of ADC is therefore unsuitable for rapidly changing analog input. ◊ Each clocking pulse increments the counter by one. It takes (2N-1) clock cycles times the clock period for an output to be produced. ...

MAX1673 Regulated, 125mA-Output, Charge-Pump DC-DC Inverter ________________General Description

... When in Skip mode, output ripple depends mostly on two parameters: charge transfer between the capacitance values of CFLY and COUT, and the ESR of COUT. The ESR ripple contribution occurs as COUT charges. The charging current creates a negative voltage pulse across the capacitor’s ESR that recedes a ...

... When in Skip mode, output ripple depends mostly on two parameters: charge transfer between the capacitance values of CFLY and COUT, and the ESR of COUT. The ESR ripple contribution occurs as COUT charges. The charging current creates a negative voltage pulse across the capacitor’s ESR that recedes a ...

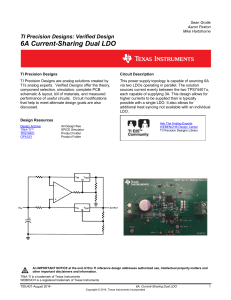

6A, Current-Sharing Dual LDO

... In order to account for the variations in the reference and offset voltage between each LDO, an external control loop must be added to ensure equal distribution of current between the two LDOs. This loop is created by the introduction of an op amp and sense resistors, as shown in Figure 3. The volta ...

... In order to account for the variations in the reference and offset voltage between each LDO, an external control loop must be added to ensure equal distribution of current between the two LDOs. This loop is created by the introduction of an op amp and sense resistors, as shown in Figure 3. The volta ...

Digital Power Monitor with Convert Pin and ALERTB Output ADM1191

... Input Pin. The voltage driven onto this pin is compared with the output of the internal current sense amplifier. The lower the voltage on the SETV, the lower the current level that causes the ALERTB output to assert. I2C Clock Pin. Open-drain input; requires an external resistive pull-up. I2C Data I ...

... Input Pin. The voltage driven onto this pin is compared with the output of the internal current sense amplifier. The lower the voltage on the SETV, the lower the current level that causes the ALERTB output to assert. I2C Clock Pin. Open-drain input; requires an external resistive pull-up. I2C Data I ...

OPA211-HT

... current of only 3.6 mA. This series also offers rail-to-rail output swing, which maximizes dynamic range. The extremely low voltage and low current noise, high speed, and wide output swing of the OPA211 series make these devices an excellent choice as a loop filter amplifier in PLL applications. In ...

... current of only 3.6 mA. This series also offers rail-to-rail output swing, which maximizes dynamic range. The extremely low voltage and low current noise, high speed, and wide output swing of the OPA211 series make these devices an excellent choice as a loop filter amplifier in PLL applications. In ...

MT-088 TUTORIAL Analog Switches and Multiplexers Basics

... DC errors associated with a single CMOS switch in the on state are shown in Figure 6. When the switch is on, dc performance is affected mainly by the switch on-resistance (RON) and leakage current (ILKG). A resistive attenuator is created by the RG-RON-RLOAD combination which produces a gain error. ...

... DC errors associated with a single CMOS switch in the on state are shown in Figure 6. When the switch is on, dc performance is affected mainly by the switch on-resistance (RON) and leakage current (ILKG). A resistive attenuator is created by the RG-RON-RLOAD combination which produces a gain error. ...

Capacitors

... When the capacitor is fully charged • When the capacitor is fully charged the pd measured across the capacitor is equal and opposite to the p.d. across the battery, so there can be no furthur current flow. ...

... When the capacitor is fully charged • When the capacitor is fully charged the pd measured across the capacitor is equal and opposite to the p.d. across the battery, so there can be no furthur current flow. ...

ADS1000 数据资料 dataSheet 下载

... An I2C bus consists of two lines, SDA and SCL. SDA carries data; SCL provides the clock. All data is transmitted across the I2C bus in groups of eight bits. To send a bit on the I2C bus, the SDA line is driven to the bit level while SCL is low (a Low on SDA indicates the bit is '0'; a High indicates ...

... An I2C bus consists of two lines, SDA and SCL. SDA carries data; SCL provides the clock. All data is transmitted across the I2C bus in groups of eight bits. To send a bit on the I2C bus, the SDA line is driven to the bit level while SCL is low (a Low on SDA indicates the bit is '0'; a High indicates ...

UJT

... emitter exceeds V1 the pn junction becomes forward biased.under these conditions holes are injected from the p type material into the n type bar these holes are repelled by positive B2 terminal and they are attracted towards B1 terminal of the bar. This accumulation of holes in the emitter to B1 re ...

... emitter exceeds V1 the pn junction becomes forward biased.under these conditions holes are injected from the p type material into the n type bar these holes are repelled by positive B2 terminal and they are attracted towards B1 terminal of the bar. This accumulation of holes in the emitter to B1 re ...

heatflow_hardware_reference

... The pinout of the thermistor connector (lower board -15) is shown in Table 2-3. This connector is where the thermistor elements are connected. There are 9 regular thermistor channels and 4 combination thermistor/reference channels. To use the regular thermistor channels a thermistor element should b ...

... The pinout of the thermistor connector (lower board -15) is shown in Table 2-3. This connector is where the thermistor elements are connected. There are 9 regular thermistor channels and 4 combination thermistor/reference channels. To use the regular thermistor channels a thermistor element should b ...

Robust RS-485 Transceiver (Rev. A)

... In any of these cases, the differential receiver will output a failsafe logic High state so that the output of the receiver is not indeterminate. Receiver failsafe is accomplished by offsetting the receiver thresholds so that the “input indeterminate” range does not include zero volts differential. ...

... In any of these cases, the differential receiver will output a failsafe logic High state so that the output of the receiver is not indeterminate. Receiver failsafe is accomplished by offsetting the receiver thresholds so that the “input indeterminate” range does not include zero volts differential. ...

Micro Family

... DC input range: 250 – 425 V Isolated output Input surge withstand: 500 V for 100 ms DC output: 2 – 48 V Programmable output: 10 to 110% Regulation: ±0.5% no load to full load Efficiency: Up to 88% Maximum operating temp: 100°C, full load Power density: up to 90 W per cubic inch Height above board: 0 ...

... DC input range: 250 – 425 V Isolated output Input surge withstand: 500 V for 100 ms DC output: 2 – 48 V Programmable output: 10 to 110% Regulation: ±0.5% no load to full load Efficiency: Up to 88% Maximum operating temp: 100°C, full load Power density: up to 90 W per cubic inch Height above board: 0 ...

THS4001 270-MHz HIGH-SPEED AMPLIFIER D

... Ground planes – It is highly recommended that a ground plane be used on the board to provide all components with a low inductive ground connection. However, in the areas of the amplifier inputs and output, the ground plane can be removed to minimize the stray capacitance. Proper power supply decoupl ...

... Ground planes – It is highly recommended that a ground plane be used on the board to provide all components with a low inductive ground connection. However, in the areas of the amplifier inputs and output, the ground plane can be removed to minimize the stray capacitance. Proper power supply decoupl ...

CDCM1802: Clock Buffer w/Programmable Divider, LVPECL I/O +

... Differential input clock. Input stage is sensitive and has a wide common mode range. Therefore, almost any type of differential signal can drive this input (LVPECL, LVDS, CML, HSTL). Since the input is high-impedance, it is recommended to terminate the PCB transmission line before the input (for exa ...

... Differential input clock. Input stage is sensitive and has a wide common mode range. Therefore, almost any type of differential signal can drive this input (LVPECL, LVDS, CML, HSTL). Since the input is high-impedance, it is recommended to terminate the PCB transmission line before the input (for exa ...

Implementation of a Single-Phase Electronic Watt

... consists of up to three 24-bit ΣΔ analog-to-digital converters (ADC) based on a second-order sigma-delta architecture that supports differential inputs. The sigma-delta ADCs (ΣΔ24) operate independently and can output 24-bit results. They can be grouped together for simultaneous sampling of voltage ...

... consists of up to three 24-bit ΣΔ analog-to-digital converters (ADC) based on a second-order sigma-delta architecture that supports differential inputs. The sigma-delta ADCs (ΣΔ24) operate independently and can output 24-bit results. They can be grouped together for simultaneous sampling of voltage ...

BD9A300MUV

... The Current Comp block compares the output ITH terminal voltage of the error amplifier and the slope block signal to determine the switching duty. In the event of over current, the current that flows through the High-Side MOSFET is limited at each cycle of the switching frequency. ...

... The Current Comp block compares the output ITH terminal voltage of the error amplifier and the slope block signal to determine the switching duty. In the event of over current, the current that flows through the High-Side MOSFET is limited at each cycle of the switching frequency. ...

MAX8550A Integrated DDR Power-Supply Solution for General Description Features

... Overvoltage/Undervoltage-Protection Control Input. This four-level logic input enables or disables the overvoltage and/or undervoltage protection. The overvoltage limit is 116% of the nominal output voltage. The undervoltage limit is 70% of the nominal output voltage. Discharge mode is enabled when ...

... Overvoltage/Undervoltage-Protection Control Input. This four-level logic input enables or disables the overvoltage and/or undervoltage protection. The overvoltage limit is 116% of the nominal output voltage. The undervoltage limit is 70% of the nominal output voltage. Discharge mode is enabled when ...

BD35395FJ-M

... In BD35395FJ-M, an independent power input pin is provided for an internal circuit operation of the IC. This is used to drive the amplifier circuit of the IC, and its maximum current rating is 4mA. The power supply voltage is 2.7 to 5.5 volts. It is recommended to connect a bypass capacitor of 1μF o ...

... In BD35395FJ-M, an independent power input pin is provided for an internal circuit operation of the IC. This is used to drive the amplifier circuit of the IC, and its maximum current rating is 4mA. The power supply voltage is 2.7 to 5.5 volts. It is recommended to connect a bypass capacitor of 1μF o ...

1. Introduction - About the journal

... The differential difference current conveyors (DDCC) [1] or differential voltage current conveyors (DVCC) [2] have received considerable attention due to they enjoy the advantages of second-generation current conveyor (CCII) and differential difference amplifier (DDA) such as larger signal bandwidth ...

... The differential difference current conveyors (DDCC) [1] or differential voltage current conveyors (DVCC) [2] have received considerable attention due to they enjoy the advantages of second-generation current conveyor (CCII) and differential difference amplifier (DDA) such as larger signal bandwidth ...

LM2596 SIMPLE SWITCHER Power Converter 150 kHz3A Step

... current column, choose the load current line that is closest to the current needed in your application, for this example, use the 3A line. In the maximum input voltage column, select the line that covers the input voltage needed in your application, in this example, use the 15V line. Continuing on t ...

... current column, choose the load current line that is closest to the current needed in your application, for this example, use the 3A line. In the maximum input voltage column, select the line that covers the input voltage needed in your application, in this example, use the 15V line. Continuing on t ...

Integrating ADC

An integrating ADC is a type of analog-to-digital converter that converts an unknown input voltage into a digital representation through the use of an integrator. In its most basic implementation, the unknown input voltage is applied to the input of the integrator and allowed to ramp for a fixed time period (the run-up period). Then a known reference voltage of opposite polarity is applied to the integrator and is allowed to ramp until the integrator output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times allow for higher resolutions. Likewise, the speed of the converter can be improved by sacrificing resolution.Converters of this type can achieve high resolution, but often do so at the expense of speed. For this reason, these converters are not found in audio or signal processing applications. Their use is typically limited to digital voltmeters and other instruments requiring highly accurate measurements.