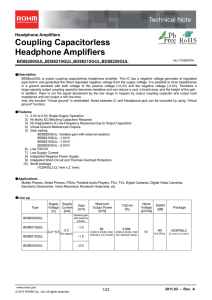

BD88200GUL

... BD88xxxGUL is output coupling capacitorless headphone amplifier. This IC has a negative voltage generator of regulated type built-in and generates the direct regulated negative voltage from the supply voltage. It is possible to drive headphones in a ground standard with both voltage of the positive ...

... BD88xxxGUL is output coupling capacitorless headphone amplifier. This IC has a negative voltage generator of regulated type built-in and generates the direct regulated negative voltage from the supply voltage. It is possible to drive headphones in a ground standard with both voltage of the positive ...

SN54ABT2241, SN74ABT2241 OCTAL BUFFERS AND LINE/MOS DRIVERS WITH 3-STATE OUTPUTS

... Supply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5 V to 7 V Input voltage range, VI (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5 V ...

... Supply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5 V to 7 V Input voltage range, VI (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5 V ...

presentation

... – Open – the path is broken and interrupts current flow – Closed – the path is complete and current flows were it is intended – Short – an unintended low resistance path that divers current ...

... – Open – the path is broken and interrupts current flow – Closed – the path is complete and current flows were it is intended – Short – an unintended low resistance path that divers current ...

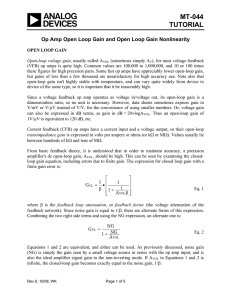

MT-044: Op Amp Open Loop Gain and Open Loop

... introduces a gain uncertainty. In the second example, AVOL drops to 300,000, which produces a gain error of 0.33%. This situation introduces a gain uncertainty of 0.28% in the closed-loop gain. In most applications, when using a good amplifier, the gain resistors of the circuit will be the largest s ...

... introduces a gain uncertainty. In the second example, AVOL drops to 300,000, which produces a gain error of 0.33%. This situation introduces a gain uncertainty of 0.28% in the closed-loop gain. In most applications, when using a good amplifier, the gain resistors of the circuit will be the largest s ...

FAN3100 Single 2A High-Speed, Low-Side Gate Driver

... driven from a range of input logic signal levels for which a voltage over 2V is considered logic high. The driving signal for the TTL inputs should have fast rising and falling edges with a slew rate of 6V/µs or faster, so the rise time from 0 to 3.3V should be 550ns or less. With reduced slew rate, ...

... driven from a range of input logic signal levels for which a voltage over 2V is considered logic high. The driving signal for the TTL inputs should have fast rising and falling edges with a slew rate of 6V/µs or faster, so the rise time from 0 to 3.3V should be 550ns or less. With reduced slew rate, ...

BQ24751B 数据资料 dataSheet 下载

... AC adapter to system-switch driver output. Connect directly to the gate of the ACFET P-channel power MOSFET and the reverse conduction blocking P-channel power MOSFET. Connect both FETs as common-source. Connect the ACFET drain to the system-load side. The PVCC should be connected to the common-sour ...

... AC adapter to system-switch driver output. Connect directly to the gate of the ACFET P-channel power MOSFET and the reverse conduction blocking P-channel power MOSFET. Connect both FETs as common-source. Connect the ACFET drain to the system-load side. The PVCC should be connected to the common-sour ...

MAX1248/MAX1249 +2.7V to +5.25V, Low-Power, 4-Channel, Serial 10-Bit ADCs in QSOP-16 _______________General Description

... The sampling architecture of the ADC’s analog comparator is illustrated in the equivalent input circuit (Figure 4). In single-ended mode, IN+ is internally switched to CH0–CH3, and IN- is switched to COM. In differential mode, IN+ and IN- are selected from two pairs: CH0/CH1 and CH2/CH3. Configure t ...

... The sampling architecture of the ADC’s analog comparator is illustrated in the equivalent input circuit (Figure 4). In single-ended mode, IN+ is internally switched to CH0–CH3, and IN- is switched to COM. In differential mode, IN+ and IN- are selected from two pairs: CH0/CH1 and CH2/CH3. Configure t ...

Preconditioner circuit analysis Nye, Matthew J. Calhoun: The NPS Institutional Archive 2011-09

... Tabulated results for Experiment 1. .................................................................14 Tabulated results for Experiment 2. .................................................................17 Frequencies effect on output waveform. ................................................... ...

... Tabulated results for Experiment 1. .................................................................14 Tabulated results for Experiment 2. .................................................................17 Frequencies effect on output waveform. ................................................... ...

Evaluates: MAX8633–MAX8636 MAX8633 Evaluation Kit General Description Features

... Detailed Description The MAX8633 EV kit operates from a 2.7V to 5.5V input power supply and is configured to evaluate the MAX8633, a pin-programmable LDO linear regulator. The EV kit provides output control through the SHDN jumper (JU1) and output monitoring (OUT2 only) at the RESET output pad. The ...

... Detailed Description The MAX8633 EV kit operates from a 2.7V to 5.5V input power supply and is configured to evaluate the MAX8633, a pin-programmable LDO linear regulator. The EV kit provides output control through the SHDN jumper (JU1) and output monitoring (OUT2 only) at the RESET output pad. The ...

MAX3385E ±15kV ESD-Protected, 3.0V to 5.5V, Low-Power, ________________General Description

... The MAX3385E is a 3V-powered EIA/TIA-232 and V.28/V.24 communications interface with low power requirements, high data-rate capabilities, and enhanced electrostatic discharge (ESD) protection. All transmitter outputs and receiver inputs are protected to ±15kV using IEC 1000-4-2 Air-Gap Discharge, ±8 ...

... The MAX3385E is a 3V-powered EIA/TIA-232 and V.28/V.24 communications interface with low power requirements, high data-rate capabilities, and enhanced electrostatic discharge (ESD) protection. All transmitter outputs and receiver inputs are protected to ±15kV using IEC 1000-4-2 Air-Gap Discharge, ±8 ...

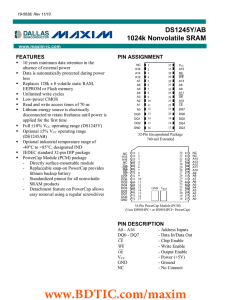

FEATURES PIN ASSIGNMENT

... 9. Each DS1350 has a built-in switch that disconnects the lithium source until the user first applies VCC. The expected tDR is defined as accumulative time in the absence of VCC starting from the time power is first applied by the user. This parameter is assured by component selection, process cont ...

... 9. Each DS1350 has a built-in switch that disconnects the lithium source until the user first applies VCC. The expected tDR is defined as accumulative time in the absence of VCC starting from the time power is first applied by the user. This parameter is assured by component selection, process cont ...

DRM126, Inverter for the Solar Panel using an MC56F8023

... The ADC module has the following features: • 12-bit resolution Dual ADCs per module; three input channels per ADC Maximum ADC clock frequency of 5.33 MHz with a 187 ns period • Sampling rate of up to 1.78 million samples per second • Single conversion time of 8.5 ADC clock cycles (8.5 x 187 ns = 1.5 ...

... The ADC module has the following features: • 12-bit resolution Dual ADCs per module; three input channels per ADC Maximum ADC clock frequency of 5.33 MHz with a 187 ns period • Sampling rate of up to 1.78 million samples per second • Single conversion time of 8.5 ADC clock cycles (8.5 x 187 ns = 1.5 ...

AD5063 数据手册DataSheet 下载

... comes with on-board resistors in a 10-lead MSOP, allowing bipolar signals to be generated with an output amplifier. The part uses a versatile 3-wire serial interface that operates at clock rates up to 30 MHz and that is compatible with standard SPI®, QSPI™, MICROWIRE™, and DSP interface standards. T ...

... comes with on-board resistors in a 10-lead MSOP, allowing bipolar signals to be generated with an output amplifier. The part uses a versatile 3-wire serial interface that operates at clock rates up to 30 MHz and that is compatible with standard SPI®, QSPI™, MICROWIRE™, and DSP interface standards. T ...

MAX19527 Evaluation Kit Evaluates: General Description Features

... manipulating the input clock signal. The PLL Frequency drop-down list programs the clock multiplier for the internal PLL in order to set the sampling frequency range. Ensure that the input clock frequency, applied at the EV kit CLK SMA connector, falls between the selected minimum and maximum freque ...

... manipulating the input clock signal. The PLL Frequency drop-down list programs the clock multiplier for the internal PLL in order to set the sampling frequency range. Ensure that the input clock frequency, applied at the EV kit CLK SMA connector, falls between the selected minimum and maximum freque ...

AD5310 数据手册DataSheet 下载

... The write sequence begins by bringing the SYNC line low. Data from the DIN line is clocked into the 16-bit shift register on the falling edge of SCLK. The serial clock frequency can be as high as 30 MHz making the AD5310 compatible with high speed DSPs. On the sixteenth falling clock edge, the last ...

... The write sequence begins by bringing the SYNC line low. Data from the DIN line is clocked into the 16-bit shift register on the falling edge of SCLK. The serial clock frequency can be as high as 30 MHz making the AD5310 compatible with high speed DSPs. On the sixteenth falling clock edge, the last ...

FEATURES PIN ASSIGNMENT

... is first applied by the user. This parameter is assured by component selection, process control, and design. It is not measured directly during production testing. 10. Each DS1245 has a built-in switch that disconnects the lithium source until VCC is first applied by the user. The expected tDR is de ...

... is first applied by the user. This parameter is assured by component selection, process control, and design. It is not measured directly during production testing. 10. Each DS1245 has a built-in switch that disconnects the lithium source until VCC is first applied by the user. The expected tDR is de ...

AD7262 数据手册DataSheet下载

... The AD7262/AD7262-5 are dual, 12-bit, high speed, low power, successive approximation ADCs that operate from a single 5 V power supply. The AD7262 features throughput rates of up to 1 MSPS per on-chip ADC. The AD7262-5 features throughput rates of up to 500 kSPS. Two complete ADC functions allow sim ...

... The AD7262/AD7262-5 are dual, 12-bit, high speed, low power, successive approximation ADCs that operate from a single 5 V power supply. The AD7262 features throughput rates of up to 1 MSPS per on-chip ADC. The AD7262-5 features throughput rates of up to 500 kSPS. Two complete ADC functions allow sim ...

BU24032GW

... BU24032GW ●General Description BU24032GW is a system Lens Driver that uses μ-step driving to make the configuration of the sophisticated, high precision and low noise lens driver system possible. This IC has a built-in driver for both DC motor and voice coil motor and a μ-step controller that decrea ...

... BU24032GW ●General Description BU24032GW is a system Lens Driver that uses μ-step driving to make the configuration of the sophisticated, high precision and low noise lens driver system possible. This IC has a built-in driver for both DC motor and voice coil motor and a μ-step controller that decrea ...

BD9536FV

... This pin supplies voltage used for driving the high-side FET. Maximum absolute ratings are 23V from GND and 5.5V from SW. BOOT voltage swings between VIN + 5VReg and 5VReg during active operation. ・HG1 (26 pin) / HG2 (17 pin) This pin supplies voltage used for driving the gate of the high-side FET. ...

... This pin supplies voltage used for driving the high-side FET. Maximum absolute ratings are 23V from GND and 5.5V from SW. BOOT voltage swings between VIN + 5VReg and 5VReg during active operation. ・HG1 (26 pin) / HG2 (17 pin) This pin supplies voltage used for driving the gate of the high-side FET. ...

Integrating ADC

An integrating ADC is a type of analog-to-digital converter that converts an unknown input voltage into a digital representation through the use of an integrator. In its most basic implementation, the unknown input voltage is applied to the input of the integrator and allowed to ramp for a fixed time period (the run-up period). Then a known reference voltage of opposite polarity is applied to the integrator and is allowed to ramp until the integrator output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times allow for higher resolutions. Likewise, the speed of the converter can be improved by sacrificing resolution.Converters of this type can achieve high resolution, but often do so at the expense of speed. For this reason, these converters are not found in audio or signal processing applications. Their use is typically limited to digital voltmeters and other instruments requiring highly accurate measurements.