MS Word template for A4 size paper

... This limits the amount of information one can cache or increases the time necessary to find information in the cache. In this paper, we propose the notion of digest caches. The most important property of a digest cache is that it stores only a hash of the flow identifier instead of the entire flow i ...

... This limits the amount of information one can cache or increases the time necessary to find information in the cache. In this paper, we propose the notion of digest caches. The most important property of a digest cache is that it stores only a hash of the flow identifier instead of the entire flow i ...

SiI 0680A Data Sheet REV1 - buffalo.nas

... This document provides technical information for the user. Silicon Image, Inc. reserves the right to modify the information in this document as necessary. The customer should make sure that they have the most recent data sheet version. Silicon Image, Inc. holds no responsibility for any errors that ...

... This document provides technical information for the user. Silicon Image, Inc. reserves the right to modify the information in this document as necessary. The customer should make sure that they have the most recent data sheet version. Silicon Image, Inc. holds no responsibility for any errors that ...

ElastiCon: An Elastic Distributed SDN Controller

... multi-threaded design [21, 2, 4, 8] in recent years. Despite the significant performance improvement over time, the single-controller systems still have limits on scalability and vulnerability. Some research papers have also explored the implementation of distributed controllers across multiple host ...

... multi-threaded design [21, 2, 4, 8] in recent years. Despite the significant performance improvement over time, the single-controller systems still have limits on scalability and vulnerability. Some research papers have also explored the implementation of distributed controllers across multiple host ...

No Slide Title - Columbia University

... Early routers were essentially general purpose computers Today, high-performance routers resemble supercomputers ...

... Early routers were essentially general purpose computers Today, high-performance routers resemble supercomputers ...

ppt

... Early routers were essentially general purpose computers Today, high-performance routers resemble supercomputers ...

... Early routers were essentially general purpose computers Today, high-performance routers resemble supercomputers ...

Memory-centric System Interconnect Design with Hybrid Memory

... Hybrid Memory Cubes (HMC) enable new opportunities for a “memory network” in system interconnect. Distributor-based network proposed to reduce network diameter and efficiently utilize processor bandwidth To improve network performance: – Latency : Pass-through uarch to minimize per-hop latency ...

... Hybrid Memory Cubes (HMC) enable new opportunities for a “memory network” in system interconnect. Distributor-based network proposed to reduce network diameter and efficiently utilize processor bandwidth To improve network performance: – Latency : Pass-through uarch to minimize per-hop latency ...

SDIO101A 1. General description SD/SDIO/MMC/CE-ATA host controller

... transmissions on the SD/SDIO/MMC/CE-ATA port. The SDIO101A offers separate pins for SD/SDIO/MMC/CE-ATA port supply voltage, host interface supply voltage and core supply voltage. The SD/SDIO/MMC/CE-ATA port can operate at a wide voltage range (1.8 V to 3.6 V) which allows the device to interface to ...

... transmissions on the SD/SDIO/MMC/CE-ATA port. The SDIO101A offers separate pins for SD/SDIO/MMC/CE-ATA port supply voltage, host interface supply voltage and core supply voltage. The SD/SDIO/MMC/CE-ATA port can operate at a wide voltage range (1.8 V to 3.6 V) which allows the device to interface to ...

VERA: An Extensible Router Architecture Scott Karlin and Larry Peterson

... and the “device independent” upper level software (typically, an operating system). This allows us to support a variety of hardware configurations without rewriting the operating system. Choosing the appropriate level of abstraction is somewhat of an art. We want to choose the abstraction level so t ...

... and the “device independent” upper level software (typically, an operating system). This allows us to support a variety of hardware configurations without rewriting the operating system. Choosing the appropriate level of abstraction is somewhat of an art. We want to choose the abstraction level so t ...

Design and Implementation of Firewire Device Driver on FreeBSD Katsushi Kobayashi

... all the devices connected are mapped into uni ed memory space. One Firewire network can be connected up to (26 - 1 = 63 ) device nodes. When using a Firewire network bridge device, up to (210 1 = 1023) network can be interconnected. Therefore, in the speci cation, almost 216 device nodes are allowe ...

... all the devices connected are mapped into uni ed memory space. One Firewire network can be connected up to (26 - 1 = 63 ) device nodes. When using a Firewire network bridge device, up to (210 1 = 1023) network can be interconnected. Therefore, in the speci cation, almost 216 device nodes are allowe ...

A Smart HPC interconnect for clusters of Virtual Machines.

... execution, and isolation to a vast number of services. These infrastructures, built on clusters of multicores, offer huge processing power; this feature makes them ideal for mass deployment of compute-intensive applications. However, I/O operations in virtualized environments are usually handled by ...

... execution, and isolation to a vast number of services. These infrastructures, built on clusters of multicores, offer huge processing power; this feature makes them ideal for mass deployment of compute-intensive applications. However, I/O operations in virtualized environments are usually handled by ...

Operating Instructions

... tool. Now just use it, you’ll get twice the result with half the effort. When the power is turned on, the BIOS first would have a strict test with system circuit、memory、keyboard、video、hard disc、floppy drive and so on. It analyzes the system configuration and initializes the base I/O setup. At last w ...

... tool. Now just use it, you’ll get twice the result with half the effort. When the power is turned on, the BIOS first would have a strict test with system circuit、memory、keyboard、video、hard disc、floppy drive and so on. It analyzes the system configuration and initializes the base I/O setup. At last w ...

Farm Issues - Indico

... When the high-water marks of the SFC buffer are reached, a throttle signal is issued via the ECS The worker CPU processes the event and always sends an ...

... When the high-water marks of the SFC buffer are reached, a throttle signal is issued via the ECS The worker CPU processes the event and always sends an ...

AN3126

... When using the DMA, the overall performance of the system is increased by freeing up the core. This is because data is moved from memory to DAC by DMA, without needing any actions by the CPU. This keeps CPU resources free for other operations. ...

... When using the DMA, the overall performance of the system is increased by freeing up the core. This is because data is moved from memory to DAC by DMA, without needing any actions by the CPU. This keeps CPU resources free for other operations. ...

Networking for Embedded Systems

... DMA operation CPU sets DMA registers for start address, length. DMA status register controls the unit. Once DMA is bus master, it transfers automatically. ...

... DMA operation CPU sets DMA registers for start address, length. DMA status register controls the unit. Once DMA is bus master, it transfers automatically. ...

xenSchedLiveMigra

... a data center or cluster. Users need not provide the operator with any OS-level access at all (e.g. a root login to quiesce processes or I/O prior to migration). “ ...

... a data center or cluster. Users need not provide the operator with any OS-level access at all (e.g. a root login to quiesce processes or I/O prior to migration). “ ...

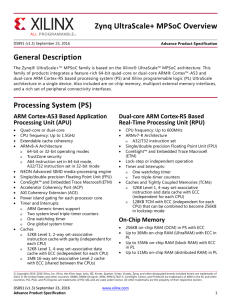

This overview describes the Xilinx Zynq UltraScale+ MPSoCs.

... © Copyright 2015–2016 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight, Cortex, and PrimeCell are tr ...

... © Copyright 2015–2016 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight, Cortex, and PrimeCell are tr ...

Quick Tip: Mitigate Network Downtime by Monitoring CPU Load in

... One of the top reasons for poor network performance is the high CPU load during peak network traffic. Too many network packets can increase the number of system processes that a CPU can handle at any given time. It is imperative that you continuously monitor CPU load for critical network devices an ...

... One of the top reasons for poor network performance is the high CPU load during peak network traffic. Too many network packets can increase the number of system processes that a CPU can handle at any given time. It is imperative that you continuously monitor CPU load for critical network devices an ...

8085 Architecture & Its Assembly language programming

... value of the GRAN bit (0=cache lines, 1=descriptors). When GRAN = 1, all descriptors are written back (even if not requested).” --Intel manual ...

... value of the GRAN bit (0=cache lines, 1=descriptors). When GRAN = 1, all descriptors are written back (even if not requested).” --Intel manual ...

CM-iGLX User Manual

... The instruction set supported by the core is a combination of Intel’s Pentium, the AMD-K6 microprocessor and the Athlon FPU, and the AMD Geode LX processor specific instructions. Specifically, it supports the Pentium, Pentium Pro, 3DNow technology for the AMD-K6 and Athlon processors, and MMX instru ...

... The instruction set supported by the core is a combination of Intel’s Pentium, the AMD-K6 microprocessor and the Athlon FPU, and the AMD Geode LX processor specific instructions. Specifically, it supports the Pentium, Pentium Pro, 3DNow technology for the AMD-K6 and Athlon processors, and MMX instru ...

NICs

... Uploading data: – NIC reads data (bits) from the system bus (parallel) – NIC packages data into frames along with error check codes and address. – NIC ships frames out onto the network medium (serial) • Downloading data: – NIC reads frames from network medium and checks address (serial) – NIC unpack ...

... Uploading data: – NIC reads data (bits) from the system bus (parallel) – NIC packages data into frames along with error check codes and address. – NIC ships frames out onto the network medium (serial) • Downloading data: – NIC reads frames from network medium and checks address (serial) – NIC unpack ...

5. The Motherboard

... Each RAM location has an address and holds one byte of data (eight bits). 000-209 Intro to CS. 5/Mother ...

... Each RAM location has an address and holds one byte of data (eight bits). 000-209 Intro to CS. 5/Mother ...

Introduction to DAQ Architecture - Indico

... • CPU free – send onwards with time-penalty events age in the SFC buffer ...

... • CPU free – send onwards with time-penalty events age in the SFC buffer ...

Profiling - University of Wisconsin–Madison

... commercial videos are not far behind Data may be generated and stored at multiple sites How to efficiently store and process this data ? ...

... commercial videos are not far behind Data may be generated and stored at multiple sites How to efficiently store and process this data ? ...

Direct memory access

Direct memory access (DMA) is a feature of computer systems that allows certain hardware subsystems to access main system (RAM) memory independently of the central processing unit (CPU).Without DMA, when the CPU is using programmed input/output, it is typically fully occupied for the entire duration of the read or write operation, and is thus unavailable to perform other work. With DMA, the CPU first initiates the transfer, then it does other operations while the transfer is in progress, and it finally receives an interrupt from the DMA controller when the operation is done. This feature is useful at any time that the CPU cannot keep up with the rate of data transfer, or when the CPU needs to perform useful work while waiting for a relatively slow I/O data transfer. Many hardware systems use DMA, including disk drive controllers, graphics cards, network cards and sound cards. DMA is also used for intra-chip data transfer in multi-core processors. Computers that have DMA channels can transfer data to and from devices with much less CPU overhead than computers without DMA channels. Similarly, a processing element inside a multi-core processor can transfer data to and from its local memory without occupying its processor time, allowing computation and data transfer to proceed in parallel.DMA can also be used for ""memory to memory"" copying or moving of data within memory. DMA can offload expensive memory operations, such as large copies or scatter-gather operations, from the CPU to a dedicated DMA engine. An implementation example is the I/O Acceleration Technology.