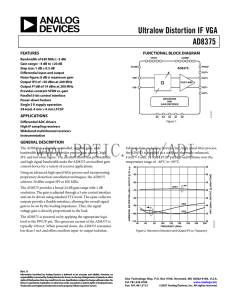

Ultralow Distortion IF VGA AD8375

... The dc voltage level at the inputs of the AD8375 is set by an internal voltage reference circuit to about 2 V. This reference is accessible at VCOM and can be used to source or sink 100 μA. For cases where a common-mode signal is applied to the inputs, such as in a single-ended application, an exter ...

... The dc voltage level at the inputs of the AD8375 is set by an internal voltage reference circuit to about 2 V. This reference is accessible at VCOM and can be used to source or sink 100 μA. For cases where a common-mode signal is applied to the inputs, such as in a single-ended application, an exter ...

DATA SHEET For a complete data sheet, please also download:

... The phase-to-output response characteristic of PC3 (Fig.10) differs from that of PC2 in that the phase angle between SIGIN and COMPIN varies between 0° and 360° and is 180° at the centre frequency. Also PC3 gives a greater voltage swing than PC2 for input phase differences but as a consequence the r ...

... The phase-to-output response characteristic of PC3 (Fig.10) differs from that of PC2 in that the phase angle between SIGIN and COMPIN varies between 0° and 360° and is 180° at the centre frequency. Also PC3 gives a greater voltage swing than PC2 for input phase differences but as a consequence the r ...

ADC16DX370 - Texas Instruments

... Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absol ...

... Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absol ...

MCOTS-C-28-24-HZ-NM - SynQor, Inc.

... Both the first stage and the second stage switch at a fixed frequency details possible circuits for driving the ON/OFF pin. Figure B is a for predictable EMI performance. Rectification of the transformer’s detailed look of the internal ON/OFF circuitry. output is accomplished with synchronous rectif ...

... Both the first stage and the second stage switch at a fixed frequency details possible circuits for driving the ON/OFF pin. Figure B is a for predictable EMI performance. Rectification of the transformer’s detailed look of the internal ON/OFF circuitry. output is accomplished with synchronous rectif ...

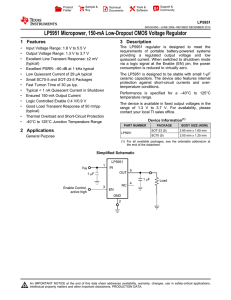

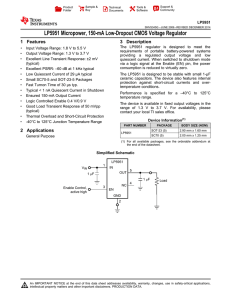

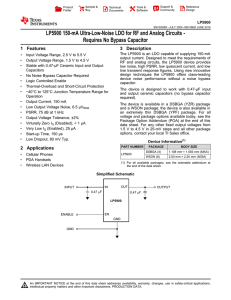

LP5951 - Texas Instruments

... The LP5951 will remain stable and in regulation with no external load. This is an important consideration in some circuits, for example CMOS RAM keep-alive applications. 7.3.2 Enable Operation The LP5951 may be switched ON or OFF by a logic input at the Enable pin, EN. A logic high at this pin will ...

... The LP5951 will remain stable and in regulation with no external load. This is an important consideration in some circuits, for example CMOS RAM keep-alive applications. 7.3.2 Enable Operation The LP5951 may be switched ON or OFF by a logic input at the Enable pin, EN. A logic high at this pin will ...

CDCM1802: Clock Buffer w/Programmable Divider, LVPECL I/O +

... Operating the CDCM1802 LVCMOS output above the maximum frequency will not cause a malfunction to the device, but the Y1 output signal swing will not achieve enough signal swing to meet the output specification. Therefore, the CDCM1802 can be operated at higher frequencies, while the LVCMOS output Y1 ...

... Operating the CDCM1802 LVCMOS output above the maximum frequency will not cause a malfunction to the device, but the Y1 output signal swing will not achieve enough signal swing to meet the output specification. Therefore, the CDCM1802 can be operated at higher frequencies, while the LVCMOS output Y1 ...

LT6108-1/LT6108-2 - High Side Current Sense Amplifier with Reference and Comparator

... control. The high threshold accuracy of the comparator, combined with the ability to latch the comparator, ensures the LT6108 can capture high speed events. The LT6108 is fully specified for operation from –40°C to 125°C, making it suitable for industrial and automotive applications. The LT6108 is a ...

... control. The high threshold accuracy of the comparator, combined with the ability to latch the comparator, ensures the LT6108 can capture high speed events. The LT6108 is fully specified for operation from –40°C to 125°C, making it suitable for industrial and automotive applications. The LT6108 is a ...

TAS5102 数据资料 dataSheet 下载

... PVDD_X = 18 V, SE mode, RL = 4 Ω, ROC = 22 kΩ, CBST = 33-nF, audio frequency = 1 kHz, AES17 filter, FPWM = 384 kHz, ambient temperature = 25°C (unless otherwise noted). Audio performance is recorded as a chipset, using TAS5086 PWM processor with an effective modulation index limit of 96.1%. All perf ...

... PVDD_X = 18 V, SE mode, RL = 4 Ω, ROC = 22 kΩ, CBST = 33-nF, audio frequency = 1 kHz, AES17 filter, FPWM = 384 kHz, ambient temperature = 25°C (unless otherwise noted). Audio performance is recorded as a chipset, using TAS5086 PWM processor with an effective modulation index limit of 96.1%. All perf ...

Predictive Comparators with Adaptive Control

... time before comparator tripping, including waveforms such as triangle waves or sinusoids. The comparator achieves its best performance when there is a high degree of cycle-to-cycle correlation in the input (which need not be periodic). Our circuit consists of an asynchronous comparator and a continu ...

... time before comparator tripping, including waveforms such as triangle waves or sinusoids. The comparator achieves its best performance when there is a high degree of cycle-to-cycle correlation in the input (which need not be periodic). Our circuit consists of an asynchronous comparator and a continu ...

Classification of Sequential Logic

... flop". So a Gated Bistable SR Flip-flop operates as a standard bistable latch but the outputs are only activated when a logic "1" is applied to its EN input and deactivated by a logic "0". In the next tutorial about Sequential Logic Circuits, we will look at another type of simple edge-triggered fli ...

... flop". So a Gated Bistable SR Flip-flop operates as a standard bistable latch but the outputs are only activated when a logic "1" is applied to its EN input and deactivated by a logic "0". In the next tutorial about Sequential Logic Circuits, we will look at another type of simple edge-triggered fli ...

High-Efficiency, 8A, Current-Mode Synchronous Step-Down Switching Regulator MAX15108 General Description Features

... power switches delivers up to 8A of output current. The regulator operates from 2.7V to 5.5V and provides an output voltage from 0.6V up to 95% of the input voltage, making the device ideal for distributed power systems, portable devices, and preregulation applications. The IC utilizes a current-mod ...

... power switches delivers up to 8A of output current. The regulator operates from 2.7V to 5.5V and provides an output voltage from 0.6V up to 95% of the input voltage, making the device ideal for distributed power systems, portable devices, and preregulation applications. The IC utilizes a current-mod ...

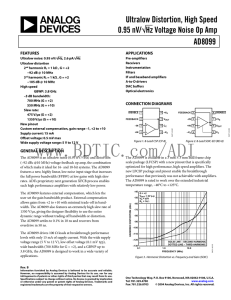

AD8099

... Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. N ...

... Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. N ...

HIGH-SPEED FULLY DIFFERENTIAL I/O AMPLIFIERS THS4120 THS4121 FEATURES

... Driving capacitive loads with high-performance amplifiers is not a problem as long as certain precautions are taken. The first is to realize that the THS412x has been internally compensated to maximize its bandwidth and slew rate performance. When the amplifier is compensated in this manner, capacit ...

... Driving capacitive loads with high-performance amplifiers is not a problem as long as certain precautions are taken. The first is to realize that the THS412x has been internally compensated to maximize its bandwidth and slew rate performance. When the amplifier is compensated in this manner, capacit ...

TPS62750 数据资料 dataSheet 下载

... USB powered portable applications. It can provide up to 1300mA average input current and is ideal for applications connected to a USB host. With an input voltage range of 2.9 V to 6.0V, the device supports batteries with extended voltage range and is ideal for powering USB applications where USB com ...

... USB powered portable applications. It can provide up to 1300mA average input current and is ideal for applications connected to a USB host. With an input voltage range of 2.9 V to 6.0V, the device supports batteries with extended voltage range and is ideal for powering USB applications where USB com ...

MCOTS-C-28-28-HZ-NMF - SynQor, Inc.

... Both the first stage and the second stage switch at a fixed frequency details possible circuits for driving the ON/OFF pin. Figure B is a for predictable EMI performance. Rectification of the transformer’s detailed look of the internal ON/OFF circuitry. output is accomplished with synchronous rectif ...

... Both the first stage and the second stage switch at a fixed frequency details possible circuits for driving the ON/OFF pin. Figure B is a for predictable EMI performance. Rectification of the transformer’s detailed look of the internal ON/OFF circuitry. output is accomplished with synchronous rectif ...

AN2834 Application note STM32L1 Series devices

... ADC simplified schematic of input stage - sample and hold circuit. . . . . . . . . . . . . . . . . . . 36 ADC input pin noise spikes from internal charge during sampling process . . . . . . . . . . . . 36 Effect of sampling time extension . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

... ADC simplified schematic of input stage - sample and hold circuit. . . . . . . . . . . . . . . . . . . 36 ADC input pin noise spikes from internal charge during sampling process . . . . . . . . . . . . 36 Effect of sampling time extension . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

OP27

... (Continued from Page 1) PSRR and CMRR exceed 120 dB. These characteristics, coupled with long-term drift of 0.2 μV/month, allow the circuit designer to achieve performance levels previously attained only by discrete designs. Low cost, high volume production of OP27 is achieved by using an on-chip Ze ...

... (Continued from Page 1) PSRR and CMRR exceed 120 dB. These characteristics, coupled with long-term drift of 0.2 μV/month, allow the circuit designer to achieve performance levels previously attained only by discrete designs. Low cost, high volume production of OP27 is achieved by using an on-chip Ze ...

Oscilloscope history

This article discusses the history and development of oscilloscope technology.