BDTIC

... active L-level during UVLO (undervoltage lockout) and a limitation of the max. H-level at 11V during normal operation. Turning on the MOSFET softly (with reduced diDRAIN/dt), the Gate drive voltage rises within 220ns from L-level to H-level. The fall time of the Gate drive voltage is less than 50ns ...

... active L-level during UVLO (undervoltage lockout) and a limitation of the max. H-level at 11V during normal operation. Turning on the MOSFET softly (with reduced diDRAIN/dt), the Gate drive voltage rises within 220ns from L-level to H-level. The fall time of the Gate drive voltage is less than 50ns ...

TDA8953 2 × 210 W class-D power amplifier

... and at the same time discharges the capacitor on pin PROT. When CPROT is fully discharged, the amplifier shuts down completely and an internal timer is started. The value of the protection capacitor (CPROT) connected to pin PROT can be between 10 pF and 220 pF (typically 47 pF). While OCP is activat ...

... and at the same time discharges the capacitor on pin PROT. When CPROT is fully discharged, the amplifier shuts down completely and an internal timer is started. The value of the protection capacitor (CPROT) connected to pin PROT can be between 10 pF and 220 pF (typically 47 pF). While OCP is activat ...

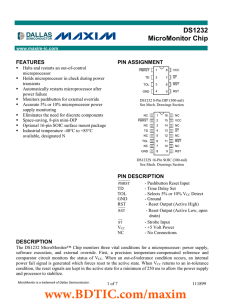

DS1232 MicroMonitor Chip FEATURES

... A watchdog timer function forces RST and RST signals to the active state when the ST input is not stimulated for a predetermined time period. The time period is set by the TD input to be typically 150 ms with TD connected to ground, 600 ms with TD left unconnected, and 1.2 seconds with TD connected ...

... A watchdog timer function forces RST and RST signals to the active state when the ST input is not stimulated for a predetermined time period. The time period is set by the TD input to be typically 150 ms with TD connected to ground, 600 ms with TD left unconnected, and 1.2 seconds with TD connected ...

Multi-mode controller for SMPS

... single-switch input-current-shaping converters (single-stage PFC) for applications supposed to comply with EN61000-3-2 or JEITA-MITI regulations. Both fixed-frequency (FF) and quasi-resonant (QR) operation are supported. The user can pick either of the two depending on application needs. The device ...

... single-switch input-current-shaping converters (single-stage PFC) for applications supposed to comply with EN61000-3-2 or JEITA-MITI regulations. Both fixed-frequency (FF) and quasi-resonant (QR) operation are supported. The user can pick either of the two depending on application needs. The device ...

RT8205L/M

... and also features fixed 5V/3.3V linear regulators. Each linear regulator provides up to 100mA output current with automatic linear regulator bootstrapping to the PWM outputs. An optional external charge pump can be monitored through SECFB (RT8205M). The RT8205L/M includes on-board power up sequencin ...

... and also features fixed 5V/3.3V linear regulators. Each linear regulator provides up to 100mA output current with automatic linear regulator bootstrapping to the PWM outputs. An optional external charge pump can be monitored through SECFB (RT8205M). The RT8205L/M includes on-board power up sequencin ...

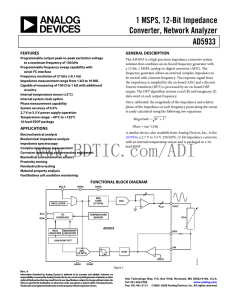

AD5933 英文数据手册DataSheet 下载

... Changes to System Description Section .......................................13 Changes to Figure 19 ......................................................................14 Changes to Figure 24 ......................................................................18 ...

... Changes to System Description Section .......................................13 Changes to Figure 19 ......................................................................14 Changes to Figure 24 ......................................................................18 ...

(ii) Is a faster form of transmission than parallel communication

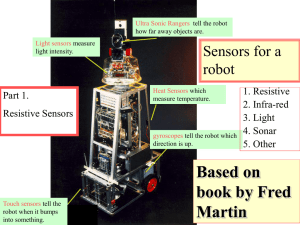

... (a) counting boxes moving along a conveyor belt, (b) verifying the level of milk in a plastic bottle moving along a conveyor belt, (c) determining when the piston in a cylinder has reached a particular point in its extension; (d) determining when a metal plate has reached the right position under a ...

... (a) counting boxes moving along a conveyor belt, (b) verifying the level of milk in a plastic bottle moving along a conveyor belt, (c) determining when the piston in a cylinder has reached a particular point in its extension; (d) determining when a metal plate has reached the right position under a ...

Phys241ManualUnit4

... Discuss at length the three time dependent voltage equations that describe the AC-driven RC circuit. Be sure to explain: ...

... Discuss at length the three time dependent voltage equations that describe the AC-driven RC circuit. Be sure to explain: ...

Analog-to-digital converter

An analog-to-digital converter (ADC, A/D, or A to D) is a device that converts a continuous physical quantity (usually voltage) to a digital number that represents the quantity's amplitude.The conversion involves quantization of the input, so it necessarily introduces a small amount of error. Furthermore, instead of continuously performing the conversion, an ADC does the conversion periodically, sampling the input. The result is a sequence of digital values that have been converted from a continuous-time and continuous-amplitude analog signal to a discrete-time and discrete-amplitude digital signal.An ADC is defined by its bandwidth (the range of frequencies it can measure) and its signal to noise ratio (how accurately it can measure a signal relative to the noise it introduces). The actual bandwidth of an ADC is characterized primarily by its sampling rate, and to a lesser extent by how it handles errors such as aliasing. The dynamic range of an ADC is influenced by many factors, including the resolution (the number of output levels it can quantize a signal to), linearity and accuracy (how well the quantization levels match the true analog signal) and jitter (small timing errors that introduce additional noise). The dynamic range of an ADC is often summarized in terms of its effective number of bits (ENOB), the number of bits of each measure it returns that are on average not noise. An ideal ADC has an ENOB equal to its resolution. ADCs are chosen to match the bandwidth and required signal to noise ratio of the signal to be quantized. If an ADC operates at a sampling rate greater than twice the bandwidth of the signal, then perfect reconstruction is possible given an ideal ADC and neglecting quantization error. The presence of quantization error limits the dynamic range of even an ideal ADC, however, if the dynamic range of the ADC exceeds that of the input signal, its effects may be neglected resulting in an essentially perfect digital representation of the input signal.An ADC may also provide an isolated measurement such as an electronic device that converts an input analog voltage or current to a digital number proportional to the magnitude of the voltage or current. However, some non-electronic or only partially electronic devices, such as rotary encoders, can also be considered ADCs. The digital output may use different coding schemes. Typically the digital output will be a two's complement binary number that is proportional to the input, but there are other possibilities. An encoder, for example, might output a Gray code.The inverse operation is performed by a digital-to-analog converter (DAC).