Slides - Agenda INFN

... The design of the analog front-end for monolithic and hybrid pixels in a 130 nm vertically integrated CMOS technology is almost completed (some work still to be done on DACs for threshold correction) Both MAPS and hybrid pixels can gain significant benefits from going 3D increase in charge collectio ...

... The design of the analog front-end for monolithic and hybrid pixels in a 130 nm vertically integrated CMOS technology is almost completed (some work still to be done on DACs for threshold correction) Both MAPS and hybrid pixels can gain significant benefits from going 3D increase in charge collectio ...

DS90LV047A 3V LVDS Quad CMOS Differential Line Driver DS90L V047A

... much more likely to appear as common-mode which is rejected by the receiver. Match electrical lengths between traces to reduce skew. Skew between the signals of a pair means a phase difference between signals which destroys the magnetic field cancellation benefits of differential signals and EMI wil ...

... much more likely to appear as common-mode which is rejected by the receiver. Match electrical lengths between traces to reduce skew. Skew between the signals of a pair means a phase difference between signals which destroys the magnetic field cancellation benefits of differential signals and EMI wil ...

a CMOS, 240 MHz 10-Bit High Speed Video DAC ADV7127

... BLANK pixel and control inputs. It is typically the pixel clock rate of the video system. CLOCK should be driven by a dedicated TTL buffer. Data Inputs (TTL Compatible). Data is latched on the rising edge of CLOCK. D0 is the least significant data bit. Unused data inputs should be connected to eithe ...

... BLANK pixel and control inputs. It is typically the pixel clock rate of the video system. CLOCK should be driven by a dedicated TTL buffer. Data Inputs (TTL Compatible). Data is latched on the rising edge of CLOCK. D0 is the least significant data bit. Unused data inputs should be connected to eithe ...

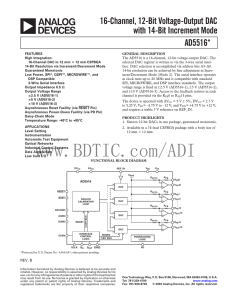

AD5516: 英文产品数据手册下载

... Serial Clock Input. Data is clocked into the shift register on the falling edge of SCLK. This operates at clock speeds up to 20 MHz. Serial Data Input. Data must be valid on the falling edge of SCLK. Serial Data Output. DOUT can be used for daisy-chaining a number of devices together or for reading ...

... Serial Clock Input. Data is clocked into the shift register on the falling edge of SCLK. This operates at clock speeds up to 20 MHz. Serial Data Input. Data must be valid on the falling edge of SCLK. Serial Data Output. DOUT can be used for daisy-chaining a number of devices together or for reading ...

FAN2512, FAN2513 150 mA CMOS LDO Regulators with Fast Start Enable Features

... design approach offers significantly reduced sensitivity to ESR (Effective Series Resistance), which degrades regulator loop stability in older designs. While the improvements featured in the FAN2512/13 family greatly simplify the design task, capacitor quality still must be considered if the design ...

... design approach offers significantly reduced sensitivity to ESR (Effective Series Resistance), which degrades regulator loop stability in older designs. While the improvements featured in the FAN2512/13 family greatly simplify the design task, capacitor quality still must be considered if the design ...

Buck Current/Voltage Fed Push-Pull PWM

... 5Soft-start pin requires a capacitor to GND. During soft-start the output of the voltage error amplifier is clamped to the soft-start capacitor voltage which is slowly charged by an internal current source. In UVLO, SS is held low. ...

... 5Soft-start pin requires a capacitor to GND. During soft-start the output of the voltage error amplifier is clamped to the soft-start capacitor voltage which is slowly charged by an internal current source. In UVLO, SS is held low. ...

Amplitude Modulator and Demodulator Circuits

... Q1 and very little of the signal appears between the emitter and collector of Q2, and so at 100 %modulation, Q2 dissipates very little power. When the audio at negative peak. The voltage emitter of Q2 is reduced to 12V, so another 12V appears between emitter and collector Q2. Efficiency drop to less ...

... Q1 and very little of the signal appears between the emitter and collector of Q2, and so at 100 %modulation, Q2 dissipates very little power. When the audio at negative peak. The voltage emitter of Q2 is reduced to 12V, so another 12V appears between emitter and collector Q2. Efficiency drop to less ...

MAX9179 Quad LVDS Receiver with Hysteresis General Description Features

... Without a fail-safe circuit, when the input is undriven, noise at the input may switch the output and it may appear to the system that data is being sent. Open or undriven terminated input conditions can occur when a cable is disconnected or cut, or when a driver output is in high impedance. A short ...

... Without a fail-safe circuit, when the input is undriven, noise at the input may switch the output and it may appear to the system that data is being sent. Open or undriven terminated input conditions can occur when a cable is disconnected or cut, or when a driver output is in high impedance. A short ...

AD7910 数据手册DataSheet下载

... speed, low power, successive approximation ADCs. The parts operate from a single 2.35 V to 5.25 V power supply and feature throughput rates up to 250 kSPS. The parts contain a low noise, wide bandwidth track-and-hold amplifier that can handle input frequencies in excess of 13 MHz. ...

... speed, low power, successive approximation ADCs. The parts operate from a single 2.35 V to 5.25 V power supply and feature throughput rates up to 250 kSPS. The parts contain a low noise, wide bandwidth track-and-hold amplifier that can handle input frequencies in excess of 13 MHz. ...

4 pole electrolytic capacitor

... The importance of attenuation and high frequency behaviour No matter how fast the amplifiers signal processing circuits are, you cannot utilize that speed if your power supply is too slow to follow rapid signal changes. The power supply's reservoir capacitor constitutes a vital element in the amplif ...

... The importance of attenuation and high frequency behaviour No matter how fast the amplifiers signal processing circuits are, you cannot utilize that speed if your power supply is too slow to follow rapid signal changes. The power supply's reservoir capacitor constitutes a vital element in the amplif ...

Midas Venice Operators Manual

... CAUTION: These servicing instructions are for use by qualified personnel only. To reduce the risk of electric shock, do not perform any servicing other than that contained in the Operating Instructions unless you are qualified to do so. Refer all servicing to qualified service personnel. 1. Security ...

... CAUTION: These servicing instructions are for use by qualified personnel only. To reduce the risk of electric shock, do not perform any servicing other than that contained in the Operating Instructions unless you are qualified to do so. Refer all servicing to qualified service personnel. 1. Security ...

STEVAL-ILD005V1: Trailing edge phase control rotary wall dimmer

... switch which opens the circuit at the minimum setting. Control of the board is achieved with a triple 3input NOR gate (pin-to-pin compatible with ST's HCF4025BE 14-lead dual in-line CMOS gate logic device in a plastic SO-14 micropackage), which acts as a gate driving voltage signal source and perfor ...

... switch which opens the circuit at the minimum setting. Control of the board is achieved with a triple 3input NOR gate (pin-to-pin compatible with ST's HCF4025BE 14-lead dual in-line CMOS gate logic device in a plastic SO-14 micropackage), which acts as a gate driving voltage signal source and perfor ...

Low Cost, Low Power 12-Bit Differential ADC Driver AD8137

... The power dissipated in the package (PD) is the sum of the quiescent power dissipation and the power dissipated in the package due to the load drive for all outputs. The quiescent power is the voltage between the supply pins (VS) times the quiescent current (IS). The load current consists of differe ...

... The power dissipated in the package (PD) is the sum of the quiescent power dissipation and the power dissipated in the package due to the load drive for all outputs. The quiescent power is the voltage between the supply pins (VS) times the quiescent current (IS). The load current consists of differe ...

Analog-to-digital converter

An analog-to-digital converter (ADC, A/D, or A to D) is a device that converts a continuous physical quantity (usually voltage) to a digital number that represents the quantity's amplitude.The conversion involves quantization of the input, so it necessarily introduces a small amount of error. Furthermore, instead of continuously performing the conversion, an ADC does the conversion periodically, sampling the input. The result is a sequence of digital values that have been converted from a continuous-time and continuous-amplitude analog signal to a discrete-time and discrete-amplitude digital signal.An ADC is defined by its bandwidth (the range of frequencies it can measure) and its signal to noise ratio (how accurately it can measure a signal relative to the noise it introduces). The actual bandwidth of an ADC is characterized primarily by its sampling rate, and to a lesser extent by how it handles errors such as aliasing. The dynamic range of an ADC is influenced by many factors, including the resolution (the number of output levels it can quantize a signal to), linearity and accuracy (how well the quantization levels match the true analog signal) and jitter (small timing errors that introduce additional noise). The dynamic range of an ADC is often summarized in terms of its effective number of bits (ENOB), the number of bits of each measure it returns that are on average not noise. An ideal ADC has an ENOB equal to its resolution. ADCs are chosen to match the bandwidth and required signal to noise ratio of the signal to be quantized. If an ADC operates at a sampling rate greater than twice the bandwidth of the signal, then perfect reconstruction is possible given an ideal ADC and neglecting quantization error. The presence of quantization error limits the dynamic range of even an ideal ADC, however, if the dynamic range of the ADC exceeds that of the input signal, its effects may be neglected resulting in an essentially perfect digital representation of the input signal.An ADC may also provide an isolated measurement such as an electronic device that converts an input analog voltage or current to a digital number proportional to the magnitude of the voltage or current. However, some non-electronic or only partially electronic devices, such as rotary encoders, can also be considered ADCs. The digital output may use different coding schemes. Typically the digital output will be a two's complement binary number that is proportional to the input, but there are other possibilities. An encoder, for example, might output a Gray code.The inverse operation is performed by a digital-to-analog converter (DAC).