BOde 100 User Manual

... 1 Introduction 1.1 Overview The Bode 100 is a multifunctional test & measurement instrument designed for professionals such as scientists, engineers and teachers engaged in the field of electronics. Its concept – universal hardware controlled by the Bode Analyzer Suite software running on a computer ...

... 1 Introduction 1.1 Overview The Bode 100 is a multifunctional test & measurement instrument designed for professionals such as scientists, engineers and teachers engaged in the field of electronics. Its concept – universal hardware controlled by the Bode Analyzer Suite software running on a computer ...

The American University in Cairo School of Science and Engineering

... Table 1: DC Operating Point Simulation at Mid rail operating point for TSMC 250nm Technology ............................................................... 47 Table 2: Results for Amplifier’s Total Output Resistance at Mid-rail Operating Point for TSMC 250nm Technology ............................. ...

... Table 1: DC Operating Point Simulation at Mid rail operating point for TSMC 250nm Technology ............................................................... 47 Table 2: Results for Amplifier’s Total Output Resistance at Mid-rail Operating Point for TSMC 250nm Technology ............................. ...

Student Biographies

... Consider a toy slot car race track with a battery powered car. The car could go any where if put on a wide open surface but when placed on the track it is constrained to follow the course. The car will only be found on the course (the track constraint) and the motor will determine where on the cours ...

... Consider a toy slot car race track with a battery powered car. The car could go any where if put on a wide open surface but when placed on the track it is constrained to follow the course. The car will only be found on the course (the track constraint) and the motor will determine where on the cours ...

The Performance of Passive Lumped

... Figure A.24 Quality factor of 15 pF capacitor...................................................................... 53 Figure A.25 Capacitance and phase of impedance ............................................................... 54 Figure A.26 Quality factor of 33 pF capacitor...................... ...

... Figure A.24 Quality factor of 15 pF capacitor...................................................................... 53 Figure A.25 Capacitance and phase of impedance ............................................................... 54 Figure A.26 Quality factor of 33 pF capacitor...................... ...

handsets_design_Oct to customers

... the analog output during switching. Caused by stray capacitance associated with the NMOS and PMOS transistors For both NMOS and PMOS to have same Ron, PMOS is approx three times the area of NMOS hence cap of PMOS= 3x cap of NMOS Balanced NMOS and PMOS => low Qinj ...

... the analog output during switching. Caused by stray capacitance associated with the NMOS and PMOS transistors For both NMOS and PMOS to have same Ron, PMOS is approx three times the area of NMOS hence cap of PMOS= 3x cap of NMOS Balanced NMOS and PMOS => low Qinj ...

ADP2114 Configurable, Dual 2 A/Single 4 A, Synchronous Step-Down DC-to-DC Regulator

... Tie SW3 to SW4 and then connect the output LC filter between SW and the output voltage. Switch Node Output. The drain of the P-channel power switch and N-channel synchronous rectifier of Channel 2. Tie SW3 to SW4 and then connect the output LC filter between SW and the output voltage. Power Ground. ...

... Tie SW3 to SW4 and then connect the output LC filter between SW and the output voltage. Switch Node Output. The drain of the P-channel power switch and N-channel synchronous rectifier of Channel 2. Tie SW3 to SW4 and then connect the output LC filter between SW and the output voltage. Power Ground. ...

Harmonic Analysis of Static var Compensator

... voltages is 5% [14], thus HDu = 0 · · · 5%. The harmonic currents and complex power to be compensated were calculated for SV C1 and SV C2 considering all the odd harmonic orders between the 3rd and 51st . Also, these calculations were repeated for a set of 51 values of TCR conduction angles into the ...

... voltages is 5% [14], thus HDu = 0 · · · 5%. The harmonic currents and complex power to be compensated were calculated for SV C1 and SV C2 considering all the odd harmonic orders between the 3rd and 51st . Also, these calculations were repeated for a set of 51 values of TCR conduction angles into the ...

REFERENCE MEASURING METHODS

... 2 Overview of CD disc specifications and items that could be measured ................... 6 2.1 Disc Geometry............................................................................................................. 6 2.1.1 Optical requirements .................................................... ...

... 2 Overview of CD disc specifications and items that could be measured ................... 6 2.1 Disc Geometry............................................................................................................. 6 2.1.1 Optical requirements .................................................... ...

calculation of tms320c5x power dissipation

... System Design for Minimum Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 System Clock and Signal Switching Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Capacitive Loading of Signals . . . . . . . . . . . ...

... System Design for Minimum Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 System Clock and Signal Switching Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Capacitive Loading of Signals . . . . . . . . . . . ...

$doc.title

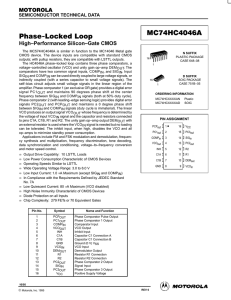

... outputs; with pullup resistors, they are compatible with LSTTL outputs. The HC4046A phase–locked loop contains three phase comparators, a voltage–controlled oscillator (VCO) and unity gain op–amp DEM OUT. The comparators have two common signal inputs, COMP IN, and SIG IN. Input SIG IN and COMP IN ca ...

... outputs; with pullup resistors, they are compatible with LSTTL outputs. The HC4046A phase–locked loop contains three phase comparators, a voltage–controlled oscillator (VCO) and unity gain op–amp DEM OUT. The comparators have two common signal inputs, COMP IN, and SIG IN. Input SIG IN and COMP IN ca ...

LTC6655 - 0.25ppm Noise, Low Drift Precision References

... The LTC6655 can be powered from as little as 500mV above the output voltage to as much as 13.2V. Superior load regulation with source and sink capability, coupled with exceptional line rejection, ensures consistent performance over a wide range of operating conditions. A shutdown mode is provided fo ...

... The LTC6655 can be powered from as little as 500mV above the output voltage to as much as 13.2V. Superior load regulation with source and sink capability, coupled with exceptional line rejection, ensures consistent performance over a wide range of operating conditions. A shutdown mode is provided fo ...