Memory interfaces

... DDR (Double Data Rate) memory, the most common memory standard shipping today, uses a clocking technique whereby two data bits are transferred per clock cycle, or once every clock edge, to significantly improve speed. Registers and PLLs are used in the Registered DIMMs commonly used in servers and o ...

... DDR (Double Data Rate) memory, the most common memory standard shipping today, uses a clocking technique whereby two data bits are transferred per clock cycle, or once every clock edge, to significantly improve speed. Registers and PLLs are used in the Registered DIMMs commonly used in servers and o ...

MAX1680/MAX1681 125mA, Frequency-Selectable, Switched-Capacitor Voltage Converters _______________General Description

... up to 125mA output current. These devices operate at one of two selectable frequencies: 125kHz/250kHz (MAX1680) and 500kHz/1MHz (MAX1681). This provides the flexibility to optimize capacitor size, operating supply current, and overall circuit efficiency. Frequency selection also allows for minimizin ...

... up to 125mA output current. These devices operate at one of two selectable frequencies: 125kHz/250kHz (MAX1680) and 500kHz/1MHz (MAX1681). This provides the flexibility to optimize capacitor size, operating supply current, and overall circuit efficiency. Frequency selection also allows for minimizin ...

$doc.title

... The input common-mode range extends from (V–) – 0.1 V to (V+) – 1.5 V. For normal operation, the inputs must be limited to this range. The common-mode rejection ratio is only valid within the valid input common-mode range. A lower supply voltage results in lower input common-mode range; therefore, a ...

... The input common-mode range extends from (V–) – 0.1 V to (V+) – 1.5 V. For normal operation, the inputs must be limited to this range. The common-mode rejection ratio is only valid within the valid input common-mode range. A lower supply voltage results in lower input common-mode range; therefore, a ...

Causes for Amplitude Compression

... function of the real electric input power supplied to the speaker and the convection cooling depending on movement of the coil. Clearly at the resonance where the input impedance is maximal the heating of the coil is minimal. The second source of amplitude compression of the fundamental component ar ...

... function of the real electric input power supplied to the speaker and the convection cooling depending on movement of the coil. Clearly at the resonance where the input impedance is maximal the heating of the coil is minimal. The second source of amplitude compression of the fundamental component ar ...

MAX1206 40Msps, 12-Bit ADC General Description Features

... The MAX1206 is a 3.3V, 12-bit analog-to-digital converter (ADC) featuring a fully differential wideband track-andhold (T/H) input, driving the internal quantizer. The MAX1206 is optimized for low power, small size, and high dynamic performance. This ADC operates from a single 3.0V to 3.6V supply, co ...

... The MAX1206 is a 3.3V, 12-bit analog-to-digital converter (ADC) featuring a fully differential wideband track-andhold (T/H) input, driving the internal quantizer. The MAX1206 is optimized for low power, small size, and high dynamic performance. This ADC operates from a single 3.0V to 3.6V supply, co ...

AD9649 - Analog Devices

... The AD9649 operates from a single 1.8 V analog power supply and features a separate digital output driver supply to accommodate 1.8 V to 3.3 V logic families. The sample-and-hold circuit maintains excellent performance for input frequencies up to 200 MHz and is designed for low cost, low power, and ...

... The AD9649 operates from a single 1.8 V analog power supply and features a separate digital output driver supply to accommodate 1.8 V to 3.3 V logic families. The sample-and-hold circuit maintains excellent performance for input frequencies up to 200 MHz and is designed for low cost, low power, and ...

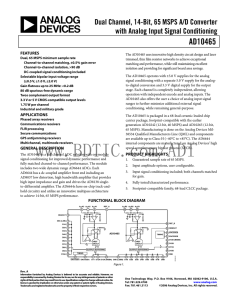

AD10465 数据手册DataSheet 下载

... The AD10465 is a full channel ADC solution with on-module signal conditioning for improved dynamic performance and fully matched channel-to-channel performance. The module includes two wide dynamic range AD6644 ADCs. Each AD6644 has a dc-coupled amplifier front end including an AD8037 low distortion ...

... The AD10465 is a full channel ADC solution with on-module signal conditioning for improved dynamic performance and fully matched channel-to-channel performance. The module includes two wide dynamic range AD6644 ADCs. Each AD6644 has a dc-coupled amplifier front end including an AD8037 low distortion ...

Digital Electronics - Test bank of Questions and Problems In order to

... 76. A TTL gate with a high output would typically be about _______ Volts a. 0.2 b. 0.9 c. 2.2 d. 3.6 77. Unwanted voltages induced in the connecting wires and the printed circuit board traces of a digital system that might possibly affect its operation are called a. Junk b. Noise c. Flux d. Clutter ...

... 76. A TTL gate with a high output would typically be about _______ Volts a. 0.2 b. 0.9 c. 2.2 d. 3.6 77. Unwanted voltages induced in the connecting wires and the printed circuit board traces of a digital system that might possibly affect its operation are called a. Junk b. Noise c. Flux d. Clutter ...

BDTIC www.BDTIC.com/infineon Wireless Control Components ASK / FSK Single Conversion Receivers

... As can be seen from the block diagram in Figure 2-1, the basic concept of the TDA5210 is a single conversion receiver with an on-chip fully integrated PLL frequency synthesizer and an IF of nominally 10.7MHz. The 10.7MHz IF was selected because of the availability of low-cost ceramic filters in a va ...

... As can be seen from the block diagram in Figure 2-1, the basic concept of the TDA5210 is a single conversion receiver with an on-chip fully integrated PLL frequency synthesizer and an IF of nominally 10.7MHz. The 10.7MHz IF was selected because of the availability of low-cost ceramic filters in a va ...

BDTIC T D A 5 2 2 0

... figure is determined by the external matching networks situated ahead of LNA and between the LNA output LNO (Pin 6) and the Mixer Inputs MI and MIX (Pins 8 and 9). The noise figure of the LNA is approximately 3dB, the current consumption is 500µA. The gain can be reduced by approximately 18dB. The s ...

... figure is determined by the external matching networks situated ahead of LNA and between the LNA output LNO (Pin 6) and the Mixer Inputs MI and MIX (Pins 8 and 9). The noise figure of the LNA is approximately 3dB, the current consumption is 500µA. The gain can be reduced by approximately 18dB. The s ...

AD633 (Rev. K)

... product that is cost effective and easy to apply. No external components or expensive user calibration are required to apply the AD633. Monolithic construction and laser calibration make the device stable and reliable. High (10 MΩ) input resistances make signal source loading negligible. Power suppl ...

... product that is cost effective and easy to apply. No external components or expensive user calibration are required to apply the AD633. Monolithic construction and laser calibration make the device stable and reliable. High (10 MΩ) input resistances make signal source loading negligible. Power suppl ...

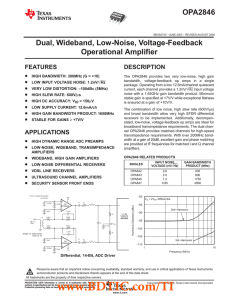

FEATURES DESCRIPTION D

... Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied. ...

... Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied. ...