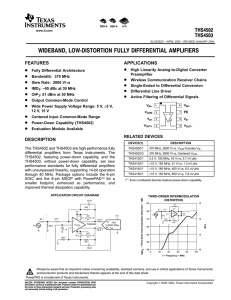

Wideband, Low-Distortion Fully Differential Amplifiers (Rev. D)

... may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied. (2) The THS450x may incorporate a PowerPAD on the underside of the chip. This acts as a heatsink and must be connected to a th ...

... may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied. (2) The THS450x may incorporate a PowerPAD on the underside of the chip. This acts as a heatsink and must be connected to a th ...

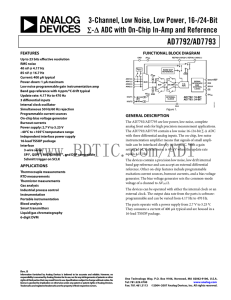

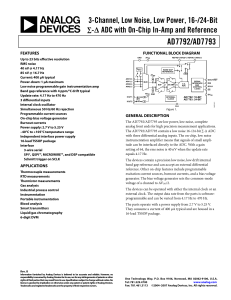

AD7792 数据手册DataSheet下载

... Change to Functional Block Diagram ........................................... 1 Changes to Specifications Section.................................................. 3 Changes to Specifications Endnote 1............................................. 5 Changes to Table 5, Table 6, and Table 7 ......... ...

... Change to Functional Block Diagram ........................................... 1 Changes to Specifications Section.................................................. 3 Changes to Specifications Endnote 1............................................. 5 Changes to Table 5, Table 6, and Table 7 ......... ...

MAX5099 Dual, 2.2MHz, Automotive Synchronous Buck Converter with 80V Load-Dump Protection General Description

... to make trade-offs between the size, efficiency, and cost. The high switching frequency also allows these devices to operate outside the AM band for automotive applications. These regulators can be protected against high voltage transients such as a load-dump condition by using the integrated overvo ...

... to make trade-offs between the size, efficiency, and cost. The high switching frequency also allows these devices to operate outside the AM band for automotive applications. These regulators can be protected against high voltage transients such as a load-dump condition by using the integrated overvo ...

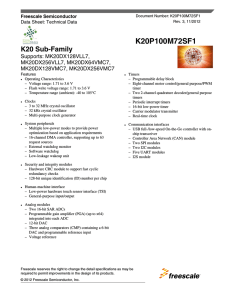

K20 Sub-Family - RS Components International

... 2. input pins • have their passive filter disabled (PORTx_PCRn[PFE]=0) ...

... 2. input pins • have their passive filter disabled (PORTx_PCRn[PFE]=0) ...

MMA7260QT ±1.5g - 6g Three Axis Low-g

... circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for an ...

... circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for an ...

±1.5g - 6g Three Axis Low-g Micromachined Accelerometer

... circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for an ...

... circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for an ...

The GA is a high-performance/low noise general

... Fmax.≧FA>FB≧FMIN. (Cn-02) (Cn-04) (Cn-05) (Cn-07) ...

... Fmax.≧FA>FB≧FMIN. (Cn-02) (Cn-04) (Cn-05) (Cn-07) ...

AS1363

... between the two voltages (reference and sample) creates an output from the error amplifier that drives the series control element to reduce the difference to a minimum. The error amplifier incorporates additional buffering to drive the relatively large gate capacitance of the series pass Pchannel MO ...

... between the two voltages (reference and sample) creates an output from the error amplifier that drives the series control element to reduce the difference to a minimum. The error amplifier incorporates additional buffering to drive the relatively large gate capacitance of the series pass Pchannel MO ...

TPC development on the right track. The development - UvA-DARE

... Figure 4.1: Simulation of an avalanche and ion drift in an Ar/iC4 H10 80/20 gas mixture. The graphs show the amount of charge as a function of the distance to the anode at four different times. At t=0 the avalanche starts with one electron, starting 50 µm from the anode, and ends with approximately 4 ...

... Figure 4.1: Simulation of an avalanche and ion drift in an Ar/iC4 H10 80/20 gas mixture. The graphs show the amount of charge as a function of the distance to the anode at four different times. At t=0 the avalanche starts with one electron, starting 50 µm from the anode, and ends with approximately 4 ...

UCC28060 数据资料 dataSheet 下载

... efficiency with low-cost components—to higher power ratings than previously possible. By utilizing a Natural Interleaving technique, both channels operate as masters (that is, there is no slave channel) synchronized to the same frequency. This approach delivers inherently strong matching, faster res ...

... efficiency with low-cost components—to higher power ratings than previously possible. By utilizing a Natural Interleaving technique, both channels operate as masters (that is, there is no slave channel) synchronized to the same frequency. This approach delivers inherently strong matching, faster res ...

TPA2031D1 数据资料 dataSheet 下载

... consists of a differential amplifier and a common-mode amplifier. The differential amplifier ensures that the amplifier outputs a differential voltage on the output that is equal to the differential input times the gain. The common-mode feedback ensures that the common-mode voltage at the output is ...

... consists of a differential amplifier and a common-mode amplifier. The differential amplifier ensures that the amplifier outputs a differential voltage on the output that is equal to the differential input times the gain. The common-mode feedback ensures that the common-mode voltage at the output is ...

4.5V to 28V Input, Synchronous PWM Buck Controllers

... power-management solution for DDR memory. The MAX8553 generates 1/2 VREFIN voltage for VTT and VTTR. The VTT and VTTR tracking voltages are maintained within 1% of 1/2 VREFIN. The MAX8554 is a 4.5V to 28V input voltage, nontracking step-down controller with a low 0.6V feedback threshold voltage. The ...

... power-management solution for DDR memory. The MAX8553 generates 1/2 VREFIN voltage for VTT and VTTR. The VTT and VTTR tracking voltages are maintained within 1% of 1/2 VREFIN. The MAX8554 is a 4.5V to 28V input voltage, nontracking step-down controller with a low 0.6V feedback threshold voltage. The ...

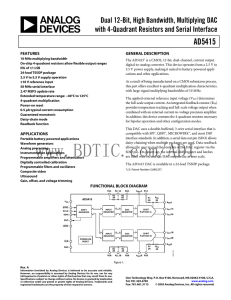

AD5415 数据手册DataSheet 下载

... automatic or synchronous update mode is selected, whereby the DAC is updated on the 16th clock falling edge when the device is in standalone mode, or on the rising edge of SYNC when in daisy-chain mode. Serial Clock Input. By default, data is clocked into the input shift register on the falling edge ...

... automatic or synchronous update mode is selected, whereby the DAC is updated on the 16th clock falling edge when the device is in standalone mode, or on the rising edge of SYNC when in daisy-chain mode. Serial Clock Input. By default, data is clocked into the input shift register on the falling edge ...

MAX15046 40V, High-Performance, Synchronous Buck Controller EVALUATION KIT AVAILABLE

... The MAX15046 synchronous step-down controller operates from a 4.5V to 40V input-voltage range and generates an adjustable output voltage from 85% of the inputvoltage down to 0.6V while supporting loads up to 25A. As long as the device supply voltage is within 5.0V to 5.5V, the input power bus (VIN) ...

... The MAX15046 synchronous step-down controller operates from a 4.5V to 40V input-voltage range and generates an adjustable output voltage from 85% of the inputvoltage down to 0.6V while supporting loads up to 25A. As long as the device supply voltage is within 5.0V to 5.5V, the input power bus (VIN) ...

TS2DDR2811 数据资料 dataSheet 下载

... DESCRIPTION/ORDERING INFORMATION The TS2DDR2811 is a 8-channel single-pole single-throw (SPST) signal switch capable of switching signals with bandwidth in excess of 1 GHz. The device includes a select pin (SEL) that is used to select any 1 of the 8 channel inputs. This select pin controls the data ...

... DESCRIPTION/ORDERING INFORMATION The TS2DDR2811 is a 8-channel single-pole single-throw (SPST) signal switch capable of switching signals with bandwidth in excess of 1 GHz. The device includes a select pin (SEL) that is used to select any 1 of the 8 channel inputs. This select pin controls the data ...

Subharmonic Mixers in CMOS Microwave Integrated Circuits Bradley Richard Jackson

... This thesis explores the design and applications of subharmonic mixers in CMOS microwave integrated circuits. First, a 2× down-converting subharmonic mixer is demonstrated with a measured conversion gain of 8 dB using a 2.1 GHz RF signal. Extending the concept of the 2× subharmonic mixer, a 4× subha ...

... This thesis explores the design and applications of subharmonic mixers in CMOS microwave integrated circuits. First, a 2× down-converting subharmonic mixer is demonstrated with a measured conversion gain of 8 dB using a 2.1 GHz RF signal. Extending the concept of the 2× subharmonic mixer, a 4× subha ...

BD8203EFV

... Figure LC filter chart ④In addition, there is a method of adding the capacitor of about 2200pF (arbitrary capacity) between each output and GNT in the PWM driver (Sled). In this case, the wiring for GNT must not have common impedances with other signals. ...

... Figure LC filter chart ④In addition, there is a method of adding the capacitor of about 2200pF (arbitrary capacity) between each output and GNT in the PWM driver (Sled). In this case, the wiring for GNT must not have common impedances with other signals. ...

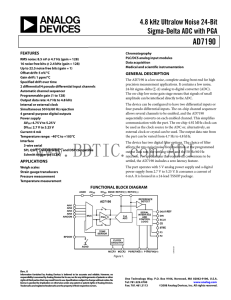

AD7190 数据手册DataSheet下载

... 24-bit sigma-delta (∑-Δ) analog to digital converter (ADC). The on-chip low noise gain stage means that signals of small amplitude can be interfaced directly to the ADC. The device can be configured to have two differential inputs or four pseudo differential inputs. The on-chip channel sequencer all ...

... 24-bit sigma-delta (∑-Δ) analog to digital converter (ADC). The on-chip low noise gain stage means that signals of small amplitude can be interfaced directly to the ADC. The device can be configured to have two differential inputs or four pseudo differential inputs. The on-chip channel sequencer all ...

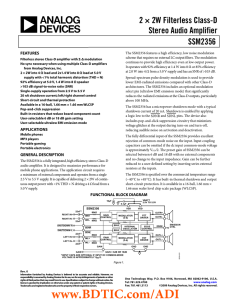

2 × 2W Filterless Class-D Stereo Audio Amplifier SSM2356

... The fully differential input of the SSM2356 provides excellent rejection of common-mode noise on the input. Input coupling capacitors can be omitted if the dc input common-mode voltage is approximately VDD/2. The preset gain of SSM2356 can be selected between 6 dB and 18 dB with no external componen ...

... The fully differential input of the SSM2356 provides excellent rejection of common-mode noise on the input. Input coupling capacitors can be omitted if the dc input common-mode voltage is approximately VDD/2. The preset gain of SSM2356 can be selected between 6 dB and 18 dB with no external componen ...

LTC6406 - 3GHz, Low Noise, Rail-to-Rail Input

... Note 11: Because the LTC6406 is a feedback amplifier with low output impedance, a resistive load is not required when driving an ADC. Therefore, typical output power can be very small in many applications. In order to compare the LTC6406 with RF style amplifiers that require 50Ω load, the output volta ...

... Note 11: Because the LTC6406 is a feedback amplifier with low output impedance, a resistive load is not required when driving an ADC. Therefore, typical output power can be very small in many applications. In order to compare the LTC6406 with RF style amplifiers that require 50Ω load, the output volta ...

... The amplifier is designed with the process D01MH from OMMIC whose characteristics have been analyzed in Chapter IV. The first step in the design process is to select the suitable transistor size to fulfill the circuit specifications; this size should be large enough to provide the required gain but ...