LTC6993-1/LTC6993-2/LTC6993-3/LTC6993-4

... L, LT, LTC, LTM, Linear Technology, TimerBlox and the Linear logo are registered trademarks and ThinSOT is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. ...

... L, LT, LTC, LTM, Linear Technology, TimerBlox and the Linear logo are registered trademarks and ThinSOT is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. ...

N3 Instruction Manual

... longer of time), the inverter does not have enough storage power to control the circuit; Therefore, when power is regenerated, the operation of the inverter is based on the setup of B000 / A015 and the condition of external switch, this is considered to be 「restart」in the following paragraphs. z Whe ...

... longer of time), the inverter does not have enough storage power to control the circuit; Therefore, when power is regenerated, the operation of the inverter is based on the setup of B000 / A015 and the condition of external switch, this is considered to be 「restart」in the following paragraphs. z Whe ...

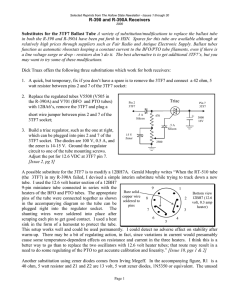

R-390 and R-390A Receivers + - Triac Substitutes for the 3TF7

... Substitutes for the 3TF7 Ballast Tube A variety of substitution/modifications to replace the ballast tube in both the R-390 and R-390A have been put forth in HSN. Spares for this tube are available although at relatively high prices through suppliers such as Fair Radio and Antique Electronic Supply. ...

... Substitutes for the 3TF7 Ballast Tube A variety of substitution/modifications to replace the ballast tube in both the R-390 and R-390A have been put forth in HSN. Spares for this tube are available although at relatively high prices through suppliers such as Fair Radio and Antique Electronic Supply. ...

HMC990LP4E 数据资料DataSheet下载

... wideband limiting LO amplifiers to achieve an unprecedented RF bandwidth of 700 MHz to 3500 MHz. Unlike conventional narrow-band downconverter RFICs, the HMC990LP4E supports both high-side and low-side LO injection over the entire RF frequency band. The RF and LO input ports are internally matched t ...

... wideband limiting LO amplifiers to achieve an unprecedented RF bandwidth of 700 MHz to 3500 MHz. Unlike conventional narrow-band downconverter RFICs, the HMC990LP4E supports both high-side and low-side LO injection over the entire RF frequency band. The RF and LO input ports are internally matched t ...

Aalborg Universitet Optimal Design of High-Order Passive-Damped Filters for Grid-Connected Applications

... is required for the grid current control, if the LCL filter resonance frequency is higher than the critical resonance frequency, which is one-sixth of the control frequency [11]. If the converter current is controlled, then, opposite result is obtained [12]. However, the stability condition of the p ...

... is required for the grid current control, if the LCL filter resonance frequency is higher than the critical resonance frequency, which is one-sixth of the control frequency [11]. If the converter current is controlled, then, opposite result is obtained [12]. However, the stability condition of the p ...

Section 4: Sensor Signal Conditioning

... In each case, the value of the fixed bridge resistor “R” is chosen to be equal to the nominal value of the variable resistor(s). The deviation of the variable resistor(s) about the nominal value is assumed to be proportional to the quantity being measured, such as strain (in the case of a strain gag ...

... In each case, the value of the fixed bridge resistor “R” is chosen to be equal to the nominal value of the variable resistor(s). The deviation of the variable resistor(s) about the nominal value is assumed to be proportional to the quantity being measured, such as strain (in the case of a strain gag ...

ADC12D800/500RF 12-Bit, 1.6/1.0 GSPS RF

... RF Performance ............................................................................................................. 9 ...

... RF Performance ............................................................................................................. 9 ...

file (7.8 MB, pdf)

... • The parallel R-C circuit time constant is typically 100 times the time period corresponding to the minimum frequency of operation. • The R-C time constant also controls the response time. • Slew rate is the primary specification that needs to be looked into while choosing the right opamp for the c ...

... • The parallel R-C circuit time constant is typically 100 times the time period corresponding to the minimum frequency of operation. • The R-C time constant also controls the response time. • Slew rate is the primary specification that needs to be looked into while choosing the right opamp for the c ...

MC9S08QA4 Series - Data Sheet

... 2 All functional non-supply pins are internally clamped to V SS and VDD. 3 Power supply must maintain regulation within operating V DD range during instantaneous and operating maximum current conditions. If positive injection current (VIn > VDD) is greater than IDD, the injection current may flow ou ...

... 2 All functional non-supply pins are internally clamped to V SS and VDD. 3 Power supply must maintain regulation within operating V DD range during instantaneous and operating maximum current conditions. If positive injection current (VIn > VDD) is greater than IDD, the injection current may flow ou ...

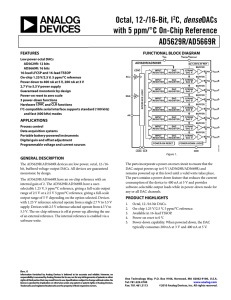

Octal, 12-/16-Bit, I2C, denseDACs with 5 ppm/°C On-Chip

... remains powered up at this level until a valid write takes place. The part contains a power-down feature that reduces the current consumption of the device to 400 nA at 5 V and provides software-selectable output loads while in power-down mode for any or all DAC channels. ...

... remains powered up at this level until a valid write takes place. The part contains a power-down feature that reduces the current consumption of the device to 400 nA at 5 V and provides software-selectable output loads while in power-down mode for any or all DAC channels. ...

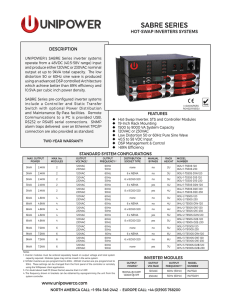

S280-77-10

... If voltage is restored before the loss of voltage transfer delay time elapses (delay interval is programmed on the inside back panel dip switch bank labeled TD1), the LCD’s ...

... If voltage is restored before the loss of voltage transfer delay time elapses (delay interval is programmed on the inside back panel dip switch bank labeled TD1), the LCD’s ...

LTC5564 - UltraFast 7ns Response Time 15GHz RF Power Detector with Comparator.

... The LTC®5564 is a precision, RF power detector for applications in the 600MHz to 15GHz frequency range. The LTC5564 operates with input power levels from –24dBm to 16dBm. A temperature compensated Schottky diode peak detector, gain-selectable operational amplifier, and fast comparator are combined i ...

... The LTC®5564 is a precision, RF power detector for applications in the 600MHz to 15GHz frequency range. The LTC5564 operates with input power levels from –24dBm to 16dBm. A temperature compensated Schottky diode peak detector, gain-selectable operational amplifier, and fast comparator are combined i ...

AD5629R: 英文产品数据手册下载

... Pulsing this pin low allows any or all DAC registers to be updated if the input registers have new data. This allows all DAC outputs to simultaneously update. Alternatively, this pin can be tied permanently low. Address Input. Sets the least significant bit of the 7-bit slave address. Power Supply I ...

... Pulsing this pin low allows any or all DAC registers to be updated if the input registers have new data. This allows all DAC outputs to simultaneously update. Alternatively, this pin can be tied permanently low. Address Input. Sets the least significant bit of the 7-bit slave address. Power Supply I ...

ADCMP341 数据手册DataSheet 下载

... Correct layout is very important to increase noise immunity. Long tracks from the input resistors to the device can lead to noise being coupled onto the inputs. To avoid this, it is best to place the input resistors as close as possible to the device. It is also recommended that a GND plane is used ...

... Correct layout is very important to increase noise immunity. Long tracks from the input resistors to the device can lead to noise being coupled onto the inputs. To avoid this, it is best to place the input resistors as close as possible to the device. It is also recommended that a GND plane is used ...

Dual 0.275% Comparators and Reference with Programmable Hysteresis ADCMP341/ADCMP343

... Correct layout is very important to increase noise immunity. Long tracks from the input resistors to the device can lead to noise being coupled onto the inputs. To avoid this, it is best to place the input resistors as close as possible to the device. It is also recommended that a GND plane is used ...

... Correct layout is very important to increase noise immunity. Long tracks from the input resistors to the device can lead to noise being coupled onto the inputs. To avoid this, it is best to place the input resistors as close as possible to the device. It is also recommended that a GND plane is used ...

74ALVT162823 1. General description 18-bit bus-interface D-type flip-flop with reset and enable with

... The registers are fully edge-triggered. The state of each D input, one set-up time before the LOW-to-HIGH clock transition is transferred to the corresponding Q output of the flip-flop. The 74ALVT162823 is designed with 30 Ω series resistance in both the pull-up and pull-down output structures. This ...

... The registers are fully edge-triggered. The state of each D input, one set-up time before the LOW-to-HIGH clock transition is transferred to the corresponding Q output of the flip-flop. The 74ALVT162823 is designed with 30 Ω series resistance in both the pull-up and pull-down output structures. This ...