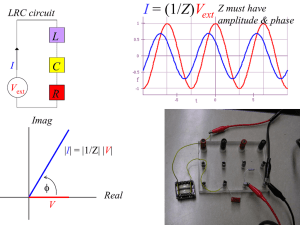

Series-Parallel ac Networks

... provides an excellent opportunity to practice our Mathcad skills with complex numbers. Remember that the j must follow the numerical value of the imaginary part and is not multiplied by the numerical value. Simply type in the numerical value and then j. Also recall that unless you make a global chan ...

... provides an excellent opportunity to practice our Mathcad skills with complex numbers. Remember that the j must follow the numerical value of the imaginary part and is not multiplied by the numerical value. Simply type in the numerical value and then j. Also recall that unless you make a global chan ...

MAX14811 Dual, Unipolar/Bipolar, High

... output impedance for the high-voltage outputs and a 27I impedance for the active clamp. The high-voltage outputs are guaranteed to provide 2.0A (typ) output current. All the pulser outputs and clamp outputs have overvoltage protection. The device uses three logic inputs per channel to control the po ...

... output impedance for the high-voltage outputs and a 27I impedance for the active clamp. The high-voltage outputs are guaranteed to provide 2.0A (typ) output current. All the pulser outputs and clamp outputs have overvoltage protection. The device uses three logic inputs per channel to control the po ...

AD7798 数据手册DataSheet下载

... Alternatively, this pin can function as a general-purpose output bit referenced between AVDD and GND Analog Input/Digital Output Pin. AIN3(−) is the negative terminal of the differential analog input pair AIN3(+)/AIN3(−). Alternatively, this pin can function as a general-purpose output bit reference ...

... Alternatively, this pin can function as a general-purpose output bit referenced between AVDD and GND Analog Input/Digital Output Pin. AIN3(−) is the negative terminal of the differential analog input pair AIN3(+)/AIN3(−). Alternatively, this pin can function as a general-purpose output bit reference ...

Jitter Reduction on High-Speed Clock Signals

... As clocking speeds increase, it becomes more and more important to be able to generate ”clean”, low-jitter clock signals. Traditionally, PLLs have been one of the most commonly used signal cleaning methods, but as higher frequencies are being used, the limits imposed by both the design complexity an ...

... As clocking speeds increase, it becomes more and more important to be able to generate ”clean”, low-jitter clock signals. Traditionally, PLLs have been one of the most commonly used signal cleaning methods, but as higher frequencies are being used, the limits imposed by both the design complexity an ...

ELECTROMAGNETIC INTERFERENCE (EMI) RESISTING ANALOG

... fabricated in NCSU 0.5um CMOS technology. Experimental results are presented when an EMI disturbance signal of 400mV and 800mV amplitude was injected at the input terminals, and compared with a conventional and an existing topology. The tested maximal EMI-induced input offset voltage corresponds to ...

... fabricated in NCSU 0.5um CMOS technology. Experimental results are presented when an EMI disturbance signal of 400mV and 800mV amplitude was injected at the input terminals, and compared with a conventional and an existing topology. The tested maximal EMI-induced input offset voltage corresponds to ...

MAX5422/MAX5423/MAX5424 256-Tap, Nonvolatile, SPI-Interface, Digital Potentiometers General Description

... Note 1: The DNL and INL are measured with the potentiometer configured as a voltage-divider with H = VDD and L = GND. The wiper terminal is unloaded and measured with a high-input-impedance voltmeter. Note 2: The DNL and INL are measured with the potentiometer configured as a variable resistor. H is ...

... Note 1: The DNL and INL are measured with the potentiometer configured as a voltage-divider with H = VDD and L = GND. The wiper terminal is unloaded and measured with a high-input-impedance voltmeter. Note 2: The DNL and INL are measured with the potentiometer configured as a variable resistor. H is ...

the basic principle of the ac generator is a direct consequence

... charged and discharged twice during each cycle: Charge is delivered to the capacitor during two quarters of the cycle and is returned to the voltage source during the remaining two quarters. Therefore, the average power supplied by the source is zero. In other words, no power losses occur in a capac ...

... charged and discharged twice during each cycle: Charge is delivered to the capacitor during two quarters of the cycle and is returned to the voltage source during the remaining two quarters. Therefore, the average power supplied by the source is zero. In other words, no power losses occur in a capac ...

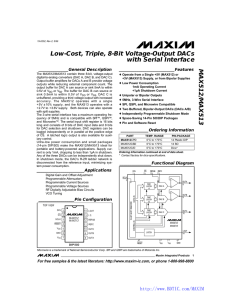

MAX512/MAX513 Low-Cost, Triple, 8-Bit Voltage-Output DACs with Serial Interface _______________General Description

... The voltage at REF_ sets the full-scale output of the DACs. The input impedance of the REF_ inputs is code dependent. The lowest value, approximately 12kΩ for REFC (8kΩ for REFAB), occurs when the input code is 01010101 (55hex). The maximum value of infinity occurs when the input code is zero. In sh ...

... The voltage at REF_ sets the full-scale output of the DACs. The input impedance of the REF_ inputs is code dependent. The lowest value, approximately 12kΩ for REFC (8kΩ for REFAB), occurs when the input code is 01010101 (55hex). The maximum value of infinity occurs when the input code is zero. In sh ...

RC Circuits

... When the switch is open, there is a potential difference of Q/C across the capacitor and 0 V across the resistor since I = 0 A. If the switch is closed at time t = 0 s, the capacitor begins to discharge through the resistor and a current flows through the circuit. At some time during the dischar ...

... When the switch is open, there is a potential difference of Q/C across the capacitor and 0 V across the resistor since I = 0 A. If the switch is closed at time t = 0 s, the capacitor begins to discharge through the resistor and a current flows through the circuit. At some time during the dischar ...

Timer and switching relay

... Rated output Motor at 50 Hz and UN (AC) Rated output inductor at 50 Hz and UN (AC) Nominal frequency Operating voltage range Timing circuit Time setting / Quantity of time domains Available time domains Standby reactivation interval Minimum power-on time Fallback value Parallel consumer loads permis ...

... Rated output Motor at 50 Hz and UN (AC) Rated output inductor at 50 Hz and UN (AC) Nominal frequency Operating voltage range Timing circuit Time setting / Quantity of time domains Available time domains Standby reactivation interval Minimum power-on time Fallback value Parallel consumer loads permis ...

User’s Guide THS4141 EVM User's Guide for HighĆSpeed FullyĆDifferential Amplifier

... high-speed operational amplifier applications. It is a complete circuit for the high-speed operational amplifier. The EVM is made of the THS4141 high-speed operational amplifier, a number of passive components, and various features and footprints that enable the user to experiment, test, and verify ...

... high-speed operational amplifier applications. It is a complete circuit for the high-speed operational amplifier. The EVM is made of the THS4141 high-speed operational amplifier, a number of passive components, and various features and footprints that enable the user to experiment, test, and verify ...

−48 V Hot Swap Controller and Digital ADM1075 Data Sheet

... the part is flexible due to the shunt regulator, and the part can be powered directly by a 10 V rail to save shunt power dissipation (see the Powering the ADM1075 section for more details). A full-scale current limit of 25 mV or 50 mV can be selected by choosing the appropriate model. The maximum cu ...

... the part is flexible due to the shunt regulator, and the part can be powered directly by a 10 V rail to save shunt power dissipation (see the Powering the ADM1075 section for more details). A full-scale current limit of 25 mV or 50 mV can be selected by choosing the appropriate model. The maximum cu ...

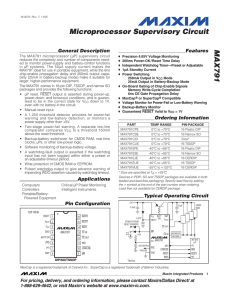

MAX791 Microprocessor Supervisory Circuit General Description Features

... to VOUT - 0.6V, if it is not already connected to VOUT (for internal timeouts). It also disables the chip-enable function, setting the Chip-Enable Output (CE OUT) to a high state. The RESET output remains active as long as MR is held low, and the reset-timeout period begins after MR returns high (Fi ...

... to VOUT - 0.6V, if it is not already connected to VOUT (for internal timeouts). It also disables the chip-enable function, setting the Chip-Enable Output (CE OUT) to a high state. The RESET output remains active as long as MR is held low, and the reset-timeout period begins after MR returns high (Fi ...

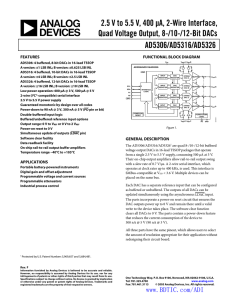

AD5306 数据手册DataSheet 下载

... write to the device takes place. The software clear function clears all DACs to 0 V. The parts contain a power-down feature that reduces the current consumption of the device to 300 nA @ 5 V (90 nA @ 3 V). All three parts have the same pinout, which allows users to select the amount of resolution ap ...

... write to the device takes place. The software clear function clears all DACs to 0 V. The parts contain a power-down feature that reduces the current consumption of the device to 300 nA @ 5 V (90 nA @ 3 V). All three parts have the same pinout, which allows users to select the amount of resolution ap ...

Lab - Rose

... wire!” This means a completely labeled schematic that includes all element values, all sources, and all pins of integrated circuits labeled. A proper schematic diagram is not a depiction of the physical layout of a circuit. It is what its name says, a scheme that shows the electrical, not the physic ...

... wire!” This means a completely labeled schematic that includes all element values, all sources, and all pins of integrated circuits labeled. A proper schematic diagram is not a depiction of the physical layout of a circuit. It is what its name says, a scheme that shows the electrical, not the physic ...