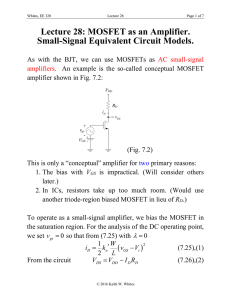

Lecture 28: MOSFET as an Amplifier. Small

... Notice the direct connection between the gate and both the dependent current source and 1/gm. While this model is correct, we’ve added the explicit boundary condition that ig = 0 to this small-signal model. It isn’t necessary to do this because the currents in the two vertical branches are both equa ...

... Notice the direct connection between the gate and both the dependent current source and 1/gm. While this model is correct, we’ve added the explicit boundary condition that ig = 0 to this small-signal model. It isn’t necessary to do this because the currents in the two vertical branches are both equa ...

21 circuits, bioelectricity, and dc instruments

... • Compare and contrast the voltage and the electromagnetic force of an electric power source. • Describe what happens to the terminal voltage, current, and power delivered to a load as internal resistance of the voltage source increases (due to aging of batteries, for example). • Explain why it is b ...

... • Compare and contrast the voltage and the electromagnetic force of an electric power source. • Describe what happens to the terminal voltage, current, and power delivered to a load as internal resistance of the voltage source increases (due to aging of batteries, for example). • Explain why it is b ...

File - Physics with Miss OO

... – There must be a source of potential difference – What is Ohm’s Law? ...

... – There must be a source of potential difference – What is Ohm’s Law? ...

MAX5251 +3V, Quad, 10-Bit Voltage-Output DAC with Serial Interface __________________General Description

... The DACs are inverted R-2R ladder networks that convert a digital input (10 data bits plus 2 sub-bits) into equivalent analog output voltages in proportion to the applied reference voltage inputs. DACs A and B share the REFAB reference input, while DACs C and D share the REFCD reference input. The t ...

... The DACs are inverted R-2R ladder networks that convert a digital input (10 data bits plus 2 sub-bits) into equivalent analog output voltages in proportion to the applied reference voltage inputs. DACs A and B share the REFAB reference input, while DACs C and D share the REFCD reference input. The t ...

LTC4060 - Standalone Linear NiMH/NiCd Fast Battery Charger

... Note 5: Assumes that the external PNP pass transistor has negligible B-C reverse leakage current when the collector is biased at 2.8V (VBAT for two charged cells in series) and the base is biased at VCC. Note 6: Assumes that the external PNP pass transistor has negligible B-E reverse leakage current ...

... Note 5: Assumes that the external PNP pass transistor has negligible B-C reverse leakage current when the collector is biased at 2.8V (VBAT for two charged cells in series) and the base is biased at VCC. Note 6: Assumes that the external PNP pass transistor has negligible B-E reverse leakage current ...

(A) I(t)

... So, the current peaks ahead in time (earlier) of the voltage There is a difference in phase of /2 (900) why? When there is not much charge on the capacitor it readily accepts more and current easily flows. However, the E-field and potential between the plates increase and consequently it becomes mo ...

... So, the current peaks ahead in time (earlier) of the voltage There is a difference in phase of /2 (900) why? When there is not much charge on the capacitor it readily accepts more and current easily flows. However, the E-field and potential between the plates increase and consequently it becomes mo ...

1 - Concordia University

... the master and ф2 feeding the slave of the register. A reduction in the number of clock lines can be accommodated if only n-MOS design is used. Two effects occur in the configuration. First, the ‘1’ level transferred to the input of the inverter is degraded to approximately Vdd-Vtn. This has the eff ...

... the master and ф2 feeding the slave of the register. A reduction in the number of clock lines can be accommodated if only n-MOS design is used. Two effects occur in the configuration. First, the ‘1’ level transferred to the input of the inverter is degraded to approximately Vdd-Vtn. This has the eff ...

OpenStax Physics Text for 2B - Chapter 4

... The derivations of the expressions for series and parallel resistance are based on the laws of conservation of energy and conservation of charge, which state that total charge and total energy are constant in any process. These two laws are directly involved in all electrical phenomena and will be i ...

... The derivations of the expressions for series and parallel resistance are based on the laws of conservation of energy and conservation of charge, which state that total charge and total energy are constant in any process. These two laws are directly involved in all electrical phenomena and will be i ...

AD7873

... high impedance when CS is high. BUSY Output. Logic output. This output is high impedance when CS is high. Data In. Logic Input. Data to be written to the AD7873 control register is provided on this input and is clocked into the register on the rising edge of DCLK (see the Control Register section). ...

... high impedance when CS is high. BUSY Output. Logic output. This output is high impedance when CS is high. Data In. Logic Input. Data to be written to the AD7873 control register is provided on this input and is clocked into the register on the rising edge of DCLK (see the Control Register section). ...

Multiplying DACs Flexible Building Blocks

... For applications where a relatively high speed ac or arbitrary signal needs to be multiplied, a high bandwidth/high slew rate op amp is required to prevent the op amp from degrading the output signal. The gain bandwidth product of an op amp will be limited by the feedback load it sees with the feedb ...

... For applications where a relatively high speed ac or arbitrary signal needs to be multiplied, a high bandwidth/high slew rate op amp is required to prevent the op amp from degrading the output signal. The gain bandwidth product of an op amp will be limited by the feedback load it sees with the feedb ...

GE 80A GigaDLynx : Non-Isolated DC-DC Power Modules Preliminary Data Sheet

... modules operate over a wide range of input voltage (VIN =4.5Vdc - 14Vdc) and provide a precisely regulated output voltage from 0.6Vdc to 2Vdc, programmable via an external resistor and/or PMBus control. Features include a digital interface using the PMBus protocol, remote On/Off, adjustable output v ...

... modules operate over a wide range of input voltage (VIN =4.5Vdc - 14Vdc) and provide a precisely regulated output voltage from 0.6Vdc to 2Vdc, programmable via an external resistor and/or PMBus control. Features include a digital interface using the PMBus protocol, remote On/Off, adjustable output v ...

A 40 MHz 70 dB Gain Variable Gain Amplifier Design

... noise and output offset, the gm/ID ratio of the negative feedback transistors was set to be the same as the input differential pair, where the DC gain is about 0 dB. The lowpass filter cutoff frequency was set to be around 40 MHz; • The transistor lengths L are determined by a tradeoff between area ...

... noise and output offset, the gm/ID ratio of the negative feedback transistors was set to be the same as the input differential pair, where the DC gain is about 0 dB. The lowpass filter cutoff frequency was set to be around 40 MHz; • The transistor lengths L are determined by a tradeoff between area ...

RZM002P02

... No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd. The content specified herein is subject to change for improvement without notice. The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products" ...

... No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd. The content specified herein is subject to change for improvement without notice. The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products" ...

LMX2306/LMX2316/LMX2326 PLLatinum Low Power Frequency

... F1. The Counter Reset enable mode bit F1, when activated, allows the reset of both N and R counters. Upon powering up, the F1 bit needs to be disabled, then the N counter resumes counting in ‘‘close’’ alignment with the R counter. (The maximum error is one prescalar cycle). F2. Refer to POWERDOWN OP ...

... F1. The Counter Reset enable mode bit F1, when activated, allows the reset of both N and R counters. Upon powering up, the F1 bit needs to be disabled, then the N counter resumes counting in ‘‘close’’ alignment with the R counter. (The maximum error is one prescalar cycle). F2. Refer to POWERDOWN OP ...

MC33094, Ignition Control

... The MC33094DW is designed for engine compartment use in 12 V automotive ignition applications to provide high performance control of the ignition coil when used with an appropriate Freescale Power Darlington Transistor. Engine control systems utilizing these devices for ignition coil control exhibit ...

... The MC33094DW is designed for engine compartment use in 12 V automotive ignition applications to provide high performance control of the ignition coil when used with an appropriate Freescale Power Darlington Transistor. Engine control systems utilizing these devices for ignition coil control exhibit ...

DIFFERENT TYPES OF LOGIC GATES

... will become 0.2V. If A, B are the inputs at one TTL NAND gate and C, D are inputs at another, NOR the output will be as follows: • F = (A + B). (C + D) = (A + B + C + D) Ch06L4-"Digital Principles and Design", Raj Kamal, Pearson Education, 2006 ...

... will become 0.2V. If A, B are the inputs at one TTL NAND gate and C, D are inputs at another, NOR the output will be as follows: • F = (A + B). (C + D) = (A + B + C + D) Ch06L4-"Digital Principles and Design", Raj Kamal, Pearson Education, 2006 ...

W

... the master and ф2 feeding the slave of the register. A reduction in the number of clock lines can be accommodated if only n-MOS design is used. Two effects occur in the configuration. First, the ‘1’ level transferred to the input of the inverter is degraded to approximately Vdd-Vtn. This has the eff ...

... the master and ф2 feeding the slave of the register. A reduction in the number of clock lines can be accommodated if only n-MOS design is used. Two effects occur in the configuration. First, the ‘1’ level transferred to the input of the inverter is degraded to approximately Vdd-Vtn. This has the eff ...

A student investigated how current varies with potential difference

... A student plans to investigate how the resistance of a light-dependent resistor (LDR) changes with light intensity. The student starts with the apparatus shown in Figure 2 but makes three changes to the ...

... A student plans to investigate how the resistance of a light-dependent resistor (LDR) changes with light intensity. The student starts with the apparatus shown in Figure 2 but makes three changes to the ...

Atmel LED Driver-MSL2162 Datasheet Brief EEPROM, and SPI Bus

... A unique combination of regulation current control and pulse width dimming management offers simple, full-screen brightness control, versatile area dimming, and a consistent white point. A current sense resistor sets LED current for each string, offering the flexibility to drive each string with a d ...

... A unique combination of regulation current control and pulse width dimming management offers simple, full-screen brightness control, versatile area dimming, and a consistent white point. A current sense resistor sets LED current for each string, offering the flexibility to drive each string with a d ...