Fine-Grained DVFS Using On-Chip Regulators - UGent

... the voltage and frequency upon individual off-chip memory accesses. We also find through our limit study that optimal energy saving is achieved for DVFS scaling speeds of 20mV/ns which is conceivable with today’s on-chip voltage regulators. The potential energy saving for memory-intensive workloads ...

... the voltage and frequency upon individual off-chip memory accesses. We also find through our limit study that optimal energy saving is achieved for DVFS scaling speeds of 20mV/ns which is conceivable with today’s on-chip voltage regulators. The potential energy saving for memory-intensive workloads ...

S260-80-2

... If the batteries are found to be at a level of health too poor to operate the motor operator, the motor inhibit function will assert accompanied by illumination of the ALARM, LOW BATTERY VOLTAGE, and MOTOR INHIBIT LEDs. Operation of the motor operator will be inhibited indefinitely until the healt ...

... If the batteries are found to be at a level of health too poor to operate the motor operator, the motor inhibit function will assert accompanied by illumination of the ALARM, LOW BATTERY VOLTAGE, and MOTOR INHIBIT LEDs. Operation of the motor operator will be inhibited indefinitely until the healt ...

SynQor 3-Phase PFC Terminal Commands Command Formats

... Commercial data converters are available to translate these levels to RS232 or USB. The serial port uses 9600 baud, 8 data bits, no parity, and one stop bit. Commands can be sent, and output viewed, with any standard terminal emulator. The interface is case sensitive. To view user text, set the term ...

... Commercial data converters are available to translate these levels to RS232 or USB. The serial port uses 9600 baud, 8 data bits, no parity, and one stop bit. Commands can be sent, and output viewed, with any standard terminal emulator. The interface is case sensitive. To view user text, set the term ...

1. Introduction - About the journal

... the input ports cannot be electronically adjusted. So in some circuits design, there is a requirement for additional resistors to be associated with or multiple CDTA merged together which is not suitable to create an integrator circuit. Later, the modified version of CDTA wherein the parasitic resis ...

... the input ports cannot be electronically adjusted. So in some circuits design, there is a requirement for additional resistors to be associated with or multiple CDTA merged together which is not suitable to create an integrator circuit. Later, the modified version of CDTA wherein the parasitic resis ...

Diapositive 1

... and couple the results to HFSS simulations • The TM like mode at 18.2 GHz has been identified and well studied in time domain. It will be used as classical cavity BPM dipole mode with 180° recombination • We proposed a simple design of the WFM RF transition which should meet the long list of require ...

... and couple the results to HFSS simulations • The TM like mode at 18.2 GHz has been identified and well studied in time domain. It will be used as classical cavity BPM dipole mode with 180° recombination • We proposed a simple design of the WFM RF transition which should meet the long list of require ...

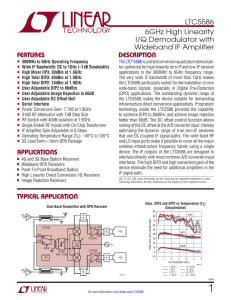

LTC5586 - 6GHz High Linearity I/Q

... Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime. The voltage on all pins should not exceed VCC + 0.3V or be less than –0.3V, ...

... Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime. The voltage on all pins should not exceed VCC + 0.3V or be less than –0.3V, ...

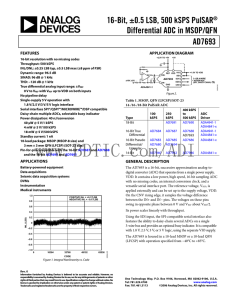

AD7693 数据手册DataSheet下载

... code transition. Positive full scale is defined as a level 1½ LSB beyond the last code transition. The deviation is measured from the middle of each code to the true straight line (see Figure 26). Differential Nonlinearity Error (DNL) In an ideal ADC, code transitions are 1 LSB apart. DNL is the max ...

... code transition. Positive full scale is defined as a level 1½ LSB beyond the last code transition. The deviation is measured from the middle of each code to the true straight line (see Figure 26). Differential Nonlinearity Error (DNL) In an ideal ADC, code transitions are 1 LSB apart. DNL is the max ...

MOVITRAC® B / System Manuals / 2006-06

... 9.2 General startup instructions .................................................................. 137 9.3 Preliminary work and resources basic unit............................................ 137 9.4 Preliminary work and resources for MOVITRAC® B with keypad ......... 137 ...

... 9.2 General startup instructions .................................................................. 137 9.3 Preliminary work and resources basic unit............................................ 137 9.4 Preliminary work and resources for MOVITRAC® B with keypad ......... 137 ...

A Digitally Controlled Oscillator System for SAW

... operating the DCO at a 4 GSM low-band frequency followed by and frequency dividers, the requirement of on-chip inductor the amount of gate oxide stress are relaxed. It was found that a dynamic divider is needed for stringent TX output phase noise while a source-coupled-logic divider can be used for ...

... operating the DCO at a 4 GSM low-band frequency followed by and frequency dividers, the requirement of on-chip inductor the amount of gate oxide stress are relaxed. It was found that a dynamic divider is needed for stringent TX output phase noise while a source-coupled-logic divider can be used for ...

Comanche Peak Nuclear Power Plant, Units 3 & 4 COL Application

... Add the following information after the last sentence of the second paragraph in DCD Subsection 8.2.1.2. Neither the grid stability analysis in Subsection 8.2.2.2 nor the failure modes and effects analysis (FMEA) in Subsection 8.2.1.2.1.1 identified the non-safety related offsite power system as ris ...

... Add the following information after the last sentence of the second paragraph in DCD Subsection 8.2.1.2. Neither the grid stability analysis in Subsection 8.2.2.2 nor the failure modes and effects analysis (FMEA) in Subsection 8.2.1.2.1.1 identified the non-safety related offsite power system as ris ...

MAX4558/MAX4559/MAX4560 ±15kV ESD-Protected, Low-Voltage, CMOS Analog Multiplexers/Switches General Description

... diode clamp could cause a significant spike in the supplies, which might damage or compromise the reliability of any other chip powered by those same supplies. In addition to the SCRs at the ESD-protected pins, these devices provide internal diodes connected to the supplies. Resistors placed in seri ...

... diode clamp could cause a significant spike in the supplies, which might damage or compromise the reliability of any other chip powered by those same supplies. In addition to the SCRs at the ESD-protected pins, these devices provide internal diodes connected to the supplies. Resistors placed in seri ...

Application Note TLE8110EE

... In specific application cases, such as driving a unipolar stepper motor, it is possible that reverse currents will flow through a channel. Reverse current occurs when there is a current out of the output instead into the output. This behavior could be when you have an application with inductive load ...

... In specific application cases, such as driving a unipolar stepper motor, it is possible that reverse currents will flow through a channel. Reverse current occurs when there is a current out of the output instead into the output. This behavior could be when you have an application with inductive load ...

BDTIC www.BDTIC.com/infineon Wireless Control Components ASK / FSK Single Conversion Receivers

... TDA5210 is a single conversion receiver with an on-chip fully integrated PLL frequency synthesizer and an IF of nominally 10.7MHz. The 10.7MHz IF was selected because of the availability of low-cost ceramic filters in a variety of bandwidths between 60kHz and 280kHz. The user is free to select other ...

... TDA5210 is a single conversion receiver with an on-chip fully integrated PLL frequency synthesizer and an IF of nominally 10.7MHz. The 10.7MHz IF was selected because of the availability of low-cost ceramic filters in a variety of bandwidths between 60kHz and 280kHz. The user is free to select other ...

Buck converter

A buck converter is a voltage step down and current step up converter.The simplest way to reduce the voltage of a DC supply is to use a linear regulator (such as a 7805), but linear regulators waste energy as they operate by dissipating excess power as heat. Buck converters, on the other hand, can be remarkably efficient (95% or higher for integrated circuits), making them useful for tasks such as converting the main voltage in a computer (12V in a desktop, 12-24V in a laptop) down to the 0.8-1.8V needed by the processor.