ADSP-2148x - Analog Devices

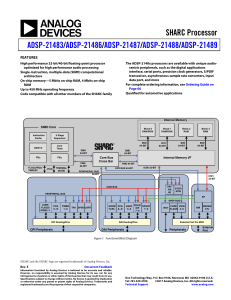

... The ADSP-2148x SHARC® processors are members of the SIMD SHARC family of DSPs that feature Analog Devices’ Super Harvard Architecture. The processors are source code compatible with the ADSP-2126x, ADSP-2136x, ADSP-2137x, ADSP-2146x, ADSP-2147x and ADSP-2116x DSPs, as well as with first generation A ...

... The ADSP-2148x SHARC® processors are members of the SIMD SHARC family of DSPs that feature Analog Devices’ Super Harvard Architecture. The processors are source code compatible with the ADSP-2126x, ADSP-2136x, ADSP-2137x, ADSP-2146x, ADSP-2147x and ADSP-2116x DSPs, as well as with first generation A ...

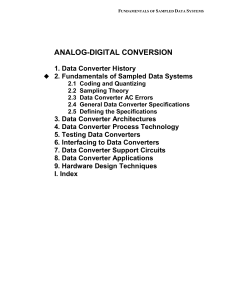

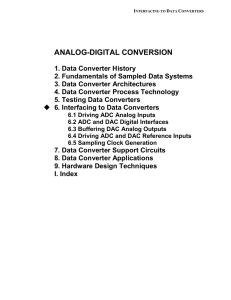

Chapter 2: Fundamentals of Sampled Data Systems

... corresponding error after conversion to binary code is only one least significant bit (LSB). In the case of mid-scale, note that only the MSB changes. It is interesting to note that this same phenomenon can occur in modern comparator-based flash converters due to comparator metastability. With small ...

... corresponding error after conversion to binary code is only one least significant bit (LSB). In the case of mid-scale, note that only the MSB changes. It is interesting to note that this same phenomenon can occur in modern comparator-based flash converters due to comparator metastability. With small ...

TJA1020

... threshold with hysteresis and an integrated filter to suppress bus line noise. The transmit data stream of the protocol controller at the TXD input is converted by the transmitter into a bus signal with controlled slew rate and wave shaping to minimize EME. The LIN bus output pin is pulled HIGH via ...

... threshold with hysteresis and an integrated filter to suppress bus line noise. The transmit data stream of the protocol controller at the TXD input is converted by the transmitter into a bus signal with controlled slew rate and wave shaping to minimize EME. The LIN bus output pin is pulled HIGH via ...

MAX3816A.pdf

... and VGA cables. A single MAX3816A placed at the display side of the link restores signal integrity bidirectionally for both DDC clock and data over 0 to 60 meters of cable. The MAX3816A features compensation for cable capacitance with a guaranteed range up to 3000pF, typically beyond 5000pF. The MAX ...

... and VGA cables. A single MAX3816A placed at the display side of the link restores signal integrity bidirectionally for both DDC clock and data over 0 to 60 meters of cable. The MAX3816A features compensation for cable capacitance with a guaranteed range up to 3000pF, typically beyond 5000pF. The MAX ...

... link of a star-shape network, the only destination address is the central station. When the central station receives IP data, it will send the IP data to the end user according to the IP address contained in the IP data packet. Based on this idea, for IP data transmission via remote station return l ...

TJA1028

... The TJA1028 is a LIN 2.0/2.1/SAE J2602 transceiver with an integrated low-drop voltage regulator. The voltage regulator can deliver up to 70 mA and is available in 3.3 V and 5.0 V variants. TJA1028 facilitates the development of compact nodes in Local Interconnect Network (LIN) bus systems. To suppo ...

... The TJA1028 is a LIN 2.0/2.1/SAE J2602 transceiver with an integrated low-drop voltage regulator. The voltage regulator can deliver up to 70 mA and is available in 3.3 V and 5.0 V variants. TJA1028 facilitates the development of compact nodes in Local Interconnect Network (LIN) bus systems. To suppo ...

Low Noise Amplifiers

... Zopt for the transistor is far from 50 ohms and the noise parameters at cryogenic temperatures are desired. • An alternative is to measure the S parameters and DC characteristics of the transistor as a function of frequency and find the equivalent circuit of the transistor from these S parameters. T ...

... Zopt for the transistor is far from 50 ohms and the noise parameters at cryogenic temperatures are desired. • An alternative is to measure the S parameters and DC characteristics of the transistor as a function of frequency and find the equivalent circuit of the transistor from these S parameters. T ...

MMSI_Internet_Jaringan-Komputer_1

... The number of bits that travel down the channel in a given interval. The number is given in signal changes per second, not necessarily bits per second. ...

... The number of bits that travel down the channel in a given interval. The number is given in signal changes per second, not necessarily bits per second. ...

K4J55323QF

... The mode register stores the data for controlling the various operating modes of GDDR3 SDRAM. It programs CAS latency, addressing mode, test mode and various vendor specific options to make GDDR3 SDRAM useful for variety of different applications. The default value of the mode register is not define ...

... The mode register stores the data for controlling the various operating modes of GDDR3 SDRAM. It programs CAS latency, addressing mode, test mode and various vendor specific options to make GDDR3 SDRAM useful for variety of different applications. The default value of the mode register is not define ...

LVDS Signaling Using APEX Device I/O Pins Introduction

... trademarks of other organizations for their respective products or services mentioned in this document. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to curren ...

... trademarks of other organizations for their respective products or services mentioned in this document. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to curren ...

3-V to 5.5-V, 12-Bit, 200-KSPS, 4-/8-Channel

... When FS is not used (FS = 1 at the falling edge of CS), the MSB (D15) is presented to the SDO pin after the CS falling edge, and successive data are available at the rising edge of SCLK. When FS is used (FS = 0 at the falling edge of CS), the MSB (D15) is presented to SDO after the falling edge of C ...

... When FS is not used (FS = 1 at the falling edge of CS), the MSB (D15) is presented to the SDO pin after the CS falling edge, and successive data are available at the rising edge of SCLK. When FS is used (FS = 0 at the falling edge of CS), the MSB (D15) is presented to SDO after the falling edge of C ...

3-V to 5.5-V, 12-Bit, 200-KSPS, 4-/8-Channel

... When FS is not used (FS = 1 at the falling edge of CS), the MSB (D15) is presented to the SDO pin after the CS falling edge, and successive data are available at the rising edge of SCLK. When FS is used (FS = 0 at the falling edge of CS), the MSB (D15) is presented to SDO after the falling edge of C ...

... When FS is not used (FS = 1 at the falling edge of CS), the MSB (D15) is presented to the SDO pin after the CS falling edge, and successive data are available at the rising edge of SCLK. When FS is used (FS = 0 at the falling edge of CS), the MSB (D15) is presented to SDO after the falling edge of C ...

ADuC824 数据手册DataSheet 下载

... microcontroller core is an 8052 and therefore 8051-instructionset-compatible. The microcontroller core machine cycle consists of 12 core clock periods of the selected core operating frequency. 8 Kbytes of nonvolatile Flash/EE program memory are provided on-chip. 640 bytes of nonvolatile Flash/EE dat ...

... microcontroller core is an 8052 and therefore 8051-instructionset-compatible. The microcontroller core machine cycle consists of 12 core clock periods of the selected core operating frequency. 8 Kbytes of nonvolatile Flash/EE program memory are provided on-chip. 640 bytes of nonvolatile Flash/EE dat ...

LPC2377/78

... Two independent power domains allow fine-tuning of power consumption based on needed features. Each peripheral has its own clock divider for further power saving. Brownout detect with separate thresholds for interrupt and forced reset. On-chip power-on reset. LPC2377_78 ...

... Two independent power domains allow fine-tuning of power consumption based on needed features. Each peripheral has its own clock divider for further power saving. Brownout detect with separate thresholds for interrupt and forced reset. On-chip power-on reset. LPC2377_78 ...

Noise Parameters

... termination to the DUT. When the diode is biased in the on state, the avalanche breakdown creates considerable electrical noise, over and above that provided by a room-temperature termination. This amount of extra noise is characterized as an “excess noise ratio” or ENR. Typical ENR values are 5 dB ...

... termination to the DUT. When the diode is biased in the on state, the avalanche breakdown creates considerable electrical noise, over and above that provided by a room-temperature termination. This amount of extra noise is characterized as an “excess noise ratio” or ENR. Typical ENR values are 5 dB ...

Single-Chip Low Cost Low Power RF

... implantable cardiac rhythm management systems, including without limitation pacemakers, defibrillators and cardiac resynchronization devices, external cardiac rhythm management systems that communicate directly with one or more implantable medical devices; or other devices used to monitor or treat c ...

... implantable cardiac rhythm management systems, including without limitation pacemakers, defibrillators and cardiac resynchronization devices, external cardiac rhythm management systems that communicate directly with one or more implantable medical devices; or other devices used to monitor or treat c ...

IGM SLM24xxProductSpecV1_23 - Industrial-Grade

... The modem is assembled in a 40-pin Dual-in-Line (DIP) form factor and thus can be referred to as a “DIP modem”. The footprint of Wintec’s “DIP” modem is only 2”x1” and is one of the most concise embedded modems that meet global telephone line standards. The DIP pins are placed on the common 0.1” gri ...

... The modem is assembled in a 40-pin Dual-in-Line (DIP) form factor and thus can be referred to as a “DIP modem”. The footprint of Wintec’s “DIP” modem is only 2”x1” and is one of the most concise embedded modems that meet global telephone line standards. The DIP pins are placed on the common 0.1” gri ...

Chapter 6: Interfacing to Data Converters

... when the applied common-mode voltage changes, the amplifier input offset voltage and input bias current does also. In fact, when both current sources remain active throughout most of the entire input common-mode range, amplifier input offset voltage is the average offset voltage of the two pairs. In ...

... when the applied common-mode voltage changes, the amplifier input offset voltage and input bias current does also. In fact, when both current sources remain active throughout most of the entire input common-mode range, amplifier input offset voltage is the average offset voltage of the two pairs. In ...

MPR121 datasheet

... For example, with C=10pF, when setting I and T so that the ADC reading counts is 1000, the sensing resolution for this capacitance at this reading counts will be 0.01pF. The conclusion is that to get the maximum sensing resolution, the capacitance shall be charged close to the upper counts limit. Th ...

... For example, with C=10pF, when setting I and T so that the ADC reading counts is 1000, the sensing resolution for this capacitance at this reading counts will be 0.01pF. The conclusion is that to get the maximum sensing resolution, the capacitance shall be charged close to the upper counts limit. Th ...

PTN3360A 1. General description Enhanced performance HDMI/DVI level shifter with inverting

... AC-coupled differential input signals to DVI v1.0 and HDMI v1.3a compliant open-drain current-steering differential output signals, up to 2.5 Gbit/s per lane. Each of these lanes provides a level-shifting differential buffer to translate from low-swing AC-coupled differential signaling on the source ...

... AC-coupled differential input signals to DVI v1.0 and HDMI v1.3a compliant open-drain current-steering differential output signals, up to 2.5 Gbit/s per lane. Each of these lanes provides a level-shifting differential buffer to translate from low-swing AC-coupled differential signaling on the source ...

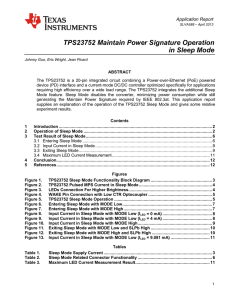

TPS23752 Maintain Power Signature Operation

... TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warra ...

... TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warra ...

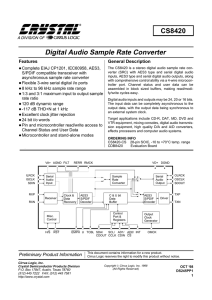

CS8420 Digital Audio Sample Rate Converter Features General Description

... l 8 kHz to 96 kHz sample rate range l 1:3 and 3:1 maximum input to output sample rate ratio l 120 dB dynamic range l -117 dB THD+N at 1 kHz l Excellent clock jitter rejection l 24 bit i/o words l Pin and microcontroller read/write access to Channel Status and User Data l Microcontroller and stand-al ...

... l 8 kHz to 96 kHz sample rate range l 1:3 and 3:1 maximum input to output sample rate ratio l 120 dB dynamic range l -117 dB THD+N at 1 kHz l Excellent clock jitter rejection l 24 bit i/o words l Pin and microcontroller read/write access to Channel Status and User Data l Microcontroller and stand-al ...

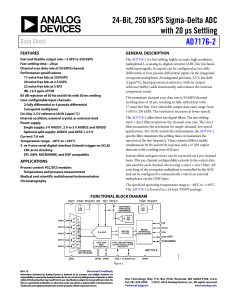

24-Bit, 250 kSPS Sigma-Delta ADC with 20 µs Settling AD7176-2

... multiplexed Σ-Δ analog-to-digital converter (ADC) for low bandwidth input signals. Its inputs can be configured as two fully differential or four pseudo differential inputs via the integrated crosspoint multiplexer. An integrated precision, 2.5 V, low drift (2 ppm/°C), band gap internal reference (w ...

... multiplexed Σ-Δ analog-to-digital converter (ADC) for low bandwidth input signals. Its inputs can be configured as two fully differential or four pseudo differential inputs via the integrated crosspoint multiplexer. An integrated precision, 2.5 V, low drift (2 ppm/°C), band gap internal reference (w ...

Features

... Data Command contains a field that selects the CPR register to be used, so frame wait time is independently configured on each command. If different timeout settings are written to each CPRx register, then the application developer can use an appropriate timeout for each TX Data Command sent, minimi ...

... Data Command contains a field that selects the CPR register to be used, so frame wait time is independently configured on each command. If different timeout settings are written to each CPRx register, then the application developer can use an appropriate timeout for each TX Data Command sent, minimi ...

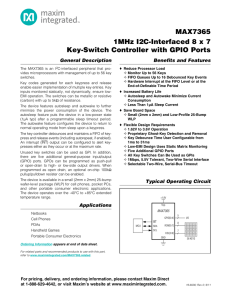

MAX7365 1MHz I2C-Interfaced 8 x 7 Key-Switch Controller with GPIO Ports General Description

... The Configuration register controls the I2C bus timeout feature, enables the key-release indicator, enables autowake, and determines how INT is deasserted. Write to bit D7 to put the device into sleep or operating mode. Autosleep and autowake, when enabled, also change the status of D7 (Table 7). Ke ...

... The Configuration register controls the I2C bus timeout feature, enables the key-release indicator, enables autowake, and determines how INT is deasserted. Write to bit D7 to put the device into sleep or operating mode. Autosleep and autowake, when enabled, also change the status of D7 (Table 7). Ke ...