In-System Programming ProASIC PLUS Devices App Note

... responding to clock pulses that are 2.8 ns wide even though the programmer is only clocking the JTAG bus at 4 MHz (FlashPro TCK rate). This means that reflections or glitches that are only 2.8 ns wide will still be seen by the device's TAP controller. If the slave controller sees a 2.8 ns clock glit ...

... responding to clock pulses that are 2.8 ns wide even though the programmer is only clocking the JTAG bus at 4 MHz (FlashPro TCK rate). This means that reflections or glitches that are only 2.8 ns wide will still be seen by the device's TAP controller. If the slave controller sees a 2.8 ns clock glit ...

Nexys 3™ FPGA Board Reference Manual Overview

... the Nexys 3 FPGA. A number of bytes (specified by the Length value) can be streamed into a specified register address from a file or out of a specified register address into a file. During upload and download, the file start location can be specified in terms of bytes. As with the Register I/O tab, ...

... the Nexys 3 FPGA. A number of bytes (specified by the Length value) can be streamed into a specified register address from a file or out of a specified register address into a file. During upload and download, the file start location can be specified in terms of bytes. As with the Register I/O tab, ...

TUSB9261 数据资料 dataSheet 下载

... configuration required to load a firmware image from an attached SPI flash memory to local RAM. In the absence of an attached SPI flash memory or a valid image in the SPI flash memory, the firmware will idle and wait for a connection from a USB host through its HID interface which is also configured ...

... configuration required to load a firmware image from an attached SPI flash memory to local RAM. In the absence of an attached SPI flash memory or a valid image in the SPI flash memory, the firmware will idle and wait for a connection from a USB host through its HID interface which is also configured ...

AT91SAM7XC512/256/128

... The embedded Flash memory can be programmed in-system via the JTAG-ICE interface or via a parallel interface on a production programmer prior to mounting. Built-in lock bits and a security bit protect the firmware from accidental overwrite and preserve its confidentiality. The AT91SAM7XC512/256/128 ...

... The embedded Flash memory can be programmed in-system via the JTAG-ICE interface or via a parallel interface on a production programmer prior to mounting. Built-in lock bits and a security bit protect the firmware from accidental overwrite and preserve its confidentiality. The AT91SAM7XC512/256/128 ...

This overview describes the Xilinx Zynq UltraScale+ MPSoCs.

... © Copyright 2015–2016 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight, Cortex, and PrimeCell are tr ...

... © Copyright 2015–2016 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight, Cortex, and PrimeCell are tr ...

Run-Time Robustness

... • NMI Solution: generate non-maskable interrupt for debug – Use NMI ISR to save picture of CPU and thread state – Can then examine what happened with debugger or in-circuit emulator ...

... • NMI Solution: generate non-maskable interrupt for debug – Use NMI ISR to save picture of CPU and thread state – Can then examine what happened with debugger or in-circuit emulator ...

SCAN92LV090 9 Channel Bus LVDS

... differential Bus LVDS (BLVDS) output levels. This allows for high speed operation, while consuming minimal power with reduced EMI. In addition, the differential signaling provides common mode noise rejection of ±1V. The receiver threshold is less than ±100 mV over a ±1V common mode range and transla ...

... differential Bus LVDS (BLVDS) output levels. This allows for high speed operation, while consuming minimal power with reduced EMI. In addition, the differential signaling provides common mode noise rejection of ±1V. The receiver threshold is less than ±100 mV over a ±1V common mode range and transla ...

ATLAS Level-1 Calorimeter Trigger Upgrade Backplane Tester Module Project Specification

... multiples of the LHC bunch clock, up to 320 Mb/s. Most signals enter and leave the module through rear edge connectors via the backplane. The module is connected to the backplane through more than 800 signal and ground pins, plus three high-current power pins. The backplane tester is a 9U (366mm) mo ...

... multiples of the LHC bunch clock, up to 320 Mb/s. Most signals enter and leave the module through rear edge connectors via the backplane. The module is connected to the backplane through more than 800 signal and ground pins, plus three high-current power pins. The backplane tester is a 9U (366mm) mo ...

Pseudo-Random Sequence Generator

... • Save power by not switching certain wires. • System with many clocked elements may require a large number of serpentine routes, leading to high area and capacitance for the clock network. • Clock spines have large skews between nearby elements driven by different serpentines. ...

... • Save power by not switching certain wires. • System with many clocked elements may require a large number of serpentine routes, leading to high area and capacitance for the clock network. • Clock spines have large skews between nearby elements driven by different serpentines. ...

ZigBit 2.4GHz Amplified Wireless Modules RevB

... custom RF/MCU solution, a module-based solution offers considerable savings in development time and NRE cost per unit during the design, prototyping, and mass production phases of product development. All ZigBits are preloaded with a Bootloader when they are sold as Modules, either in Single units o ...

... custom RF/MCU solution, a module-based solution offers considerable savings in development time and NRE cost per unit during the design, prototyping, and mass production phases of product development. All ZigBits are preloaded with a Bootloader when they are sold as Modules, either in Single units o ...

Hardware Design Guide

... Whichever connector is chosen, "keep-out" areas may be required by some tools. Consult the preferred tool vendor to determine any area that must remain clear around the debug connector. Some tool vendors may include an extension cable to minimize "keep-out" areas, but use of an extension will degrad ...

... Whichever connector is chosen, "keep-out" areas may be required by some tools. Consult the preferred tool vendor to determine any area that must remain clear around the debug connector. Some tool vendors may include an extension cable to minimize "keep-out" areas, but use of an extension will degrad ...

User Manual

... Analog inputs Ax support voltages from 0V to 2.5V which is the maximum allowable voltage per the MAX 10 FPGA integrated analog-to-digital converter. Ax lines may work as a digital lines (GPIO) – please notice that there are 1kΩ resistors connected in series. ...

... Analog inputs Ax support voltages from 0V to 2.5V which is the maximum allowable voltage per the MAX 10 FPGA integrated analog-to-digital converter. Ax lines may work as a digital lines (GPIO) – please notice that there are 1kΩ resistors connected in series. ...

Mounting the STK503

... JTAG connector: This is the connection that lets you upload and debug your application with the JTAGICE mk II. See JTAG programming and JTAG debugging. ISP connector: By mounting a cable between this connector and the programming connector on STK500, you can easily upload new programs to the AVR. Se ...

... JTAG connector: This is the connection that lets you upload and debug your application with the JTAGICE mk II. See JTAG programming and JTAG debugging. ISP connector: By mounting a cable between this connector and the programming connector on STK500, you can easily upload new programs to the AVR. Se ...

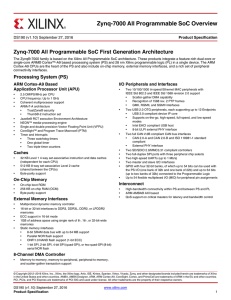

Zynq-7000 All Programmable SoC Overview (DS190)

... third-party tools and IP providers in combination with Xilinx’s existing PL ecosystem. The inclusion of an application processor enables high-level operating system support, e.g., Linux. Other standard operating systems used with the Cortex-A9 processor are also available for the Zynq-7000 family. T ...

... third-party tools and IP providers in combination with Xilinx’s existing PL ecosystem. The inclusion of an application processor enables high-level operating system support, e.g., Linux. Other standard operating systems used with the Cortex-A9 processor are also available for the Zynq-7000 family. T ...

Using a Dallas/Maxim DS1811 in the Reset Section. There is also

... Note the 1k pull-up resistor is needed for additional current draw for all devices needing reset. If not installed, the MPU board can be intermittent on powerup because the DS1811 can't source enough current to bring the reset signal high by itself. As Neil explains, replacing resistor R11 is a goo ...

... Note the 1k pull-up resistor is needed for additional current draw for all devices needing reset. If not installed, the MPU board can be intermittent on powerup because the DS1811 can't source enough current to bring the reset signal high by itself. As Neil explains, replacing resistor R11 is a goo ...

BS2 Tutorial - Welcome to Computer Science

... program from EEPROM and executes the instructions reading and controlling I/O pins. The program will remain in EEPROM indefinitely with or without power applied. ...

... program from EEPROM and executes the instructions reading and controlling I/O pins. The program will remain in EEPROM indefinitely with or without power applied. ...

Digilent Nexys2 Board Reference Manual

... cable can supply, an external power supply should be used. The Nexys2 board uses a six layer PCB, with the inner layers dedicated to VCC and GND planes. The FPGA and the other ICs on the board all have a large complement of bypass capacitors placed as close as possible to each VCC pin. The power sup ...

... cable can supply, an external power supply should be used. The Nexys2 board uses a six layer PCB, with the inner layers dedicated to VCC and GND planes. The FPGA and the other ICs on the board all have a large complement of bypass capacitors placed as close as possible to each VCC pin. The power sup ...

Functions - staff.uni

... chains will be joined via a common connector. The CPLD will be flashed through its JTAG interface. The FPGA can be configured via JTAG as well, if required for firmware development. FPGAs are RAM-based programmable logic circuits that need to be configured after power-up. The default configuration m ...

... chains will be joined via a common connector. The CPLD will be flashed through its JTAG interface. The FPGA can be configured via JTAG as well, if required for firmware development. FPGAs are RAM-based programmable logic circuits that need to be configured after power-up. The default configuration m ...

AT91SAM7A3 数据手册DataSheet 下载

... peripherals, including two 2.0B full CAN controllers, and a complete set of system functions minimizing the number of external components. The device is an ideal migration path for 8-bit microcontroller users looking for additional performance and extended memory. The embedded Flash memory can be pr ...

... peripherals, including two 2.0B full CAN controllers, and a complete set of system functions minimizing the number of external components. The device is an ideal migration path for 8-bit microcontroller users looking for additional performance and extended memory. The embedded Flash memory can be pr ...

TWR-KM34Z75M Tower Module User`s Guide

... The CPU software can enable the RTC oscillator connected to (EXTAL0/XTAL0) if desired, or use the second high frequency oscillator connected to (EXTAL1/XTAL1). The RTC crystal oscillator range is: 31.25 kHz to 39.0625 kHz (typ. 32.768 kHz). The high frequency crystal oscillator range: 1 to 32 MHz. O ...

... The CPU software can enable the RTC oscillator connected to (EXTAL0/XTAL0) if desired, or use the second high frequency oscillator connected to (EXTAL1/XTAL1). The RTC crystal oscillator range is: 31.25 kHz to 39.0625 kHz (typ. 32.768 kHz). The high frequency crystal oscillator range: 1 to 32 MHz. O ...