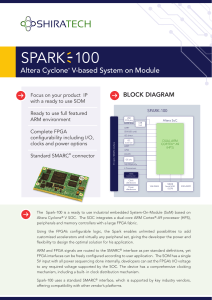

Altera Cyclone® V-based System on Module

... flexibility to design the optimal solution for his application. ARM and FPGA signals are routed to the SMARC® interface as per standard definitions, yet FPGA interfaces can be freely configured according to user application. The SOM has a single 5V input with all power sequencing done internally, de ...

... flexibility to design the optimal solution for his application. ARM and FPGA signals are routed to the SMARC® interface as per standard definitions, yet FPGA interfaces can be freely configured according to user application. The SOM has a single 5V input with all power sequencing done internally, de ...

We choose Xilinx (Virtex V family, with hard PCIe core)

... Direct connection to the mezzanine connector Direct access to 2 independent SRAM blocks and DRAM ...

... Direct connection to the mezzanine connector Direct access to 2 independent SRAM blocks and DRAM ...

FPGA SPARTAN 3 an Evaluation Kit

... USART stands for Universal Synchronous Asynchronous Receiver Transmitter. FPGASP3AN Kit provides an RS232 port that can be driven by the Spartan-3AN FPGA. A subset of the RS232 signals is used on the Spartan 3AN kit to implement this interface (RxD and TxD signals). ...

... USART stands for Universal Synchronous Asynchronous Receiver Transmitter. FPGASP3AN Kit provides an RS232 port that can be driven by the Spartan-3AN FPGA. A subset of the RS232 signals is used on the Spartan 3AN kit to implement this interface (RxD and TxD signals). ...

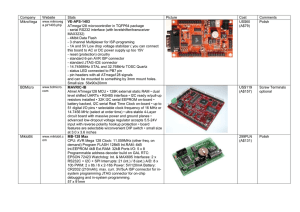

Company - AVR Freaks

... - status LED connected to PB7 pin - pin headers with all ATmega128 signals and can be mounted to something by 3mm mount holes. Small size 56x90x20mm MAVRIC-IB Atmel ATmega128 MCU • 128K external static RAM • dual level shifted UARTs • RS485 interface • I2C ready w/pull-up resistors installed • 32K I ...

... - status LED connected to PB7 pin - pin headers with all ATmega128 signals and can be mounted to something by 3mm mount holes. Small size 56x90x20mm MAVRIC-IB Atmel ATmega128 MCU • 128K external static RAM • dual level shifted UARTs • RS485 interface • I2C ready w/pull-up resistors installed • 32K I ...

ATLAS pixel chip upgrade

... DHP – Signal Rates & Data Flow 1024 r/o lines from DEPFET matrix 256 inputs per DCD ...

... DHP – Signal Rates & Data Flow 1024 r/o lines from DEPFET matrix 256 inputs per DCD ...

Design for Testability Guidelines

... • If boundary scan is the dominant function for the pins but it is possible that other functions may be required then optional fit resistors allow the configuration pins to be either high or low with a minor board change. • If there is a requirement to be able to switch easily between functions then ...

... • If boundary scan is the dominant function for the pins but it is possible that other functions may be required then optional fit resistors allow the configuration pins to be either high or low with a minor board change. • If there is a requirement to be able to switch easily between functions then ...

Features:

... All 8 pins of Port C may be used to run the LCD connector. When using the LCD, do NOT attempt to use Port C for any other function. The LCD connector provides all the necessary inputs and supply voltages for standard character LCDs. The contrast is changed using the potentiometer. The connector also ...

... All 8 pins of Port C may be used to run the LCD connector. When using the LCD, do NOT attempt to use Port C for any other function. The LCD connector provides all the necessary inputs and supply voltages for standard character LCDs. The contrast is changed using the potentiometer. The connector also ...

i By David Krakauer, Product Line Manager Debugging a complex system often requires direct access to the FPGA or embedded controller

... have invested considerable time and energy building your system, the last thing you want to do is to destroy it and then have to explain that to your supervisor! Designers often use optocouplers to isolate the diagnostic interface, but these can be difficult to work with or even ...

... have invested considerable time and energy building your system, the last thing you want to do is to destroy it and then have to explain that to your supervisor! Designers often use optocouplers to isolate the diagnostic interface, but these can be difficult to work with or even ...

MSP-FET430 FLASH Emulation Tool (for use with IAR Version 3.x

... The JTAG pins provide access to the Flash memory of the MSP430Fxxx devices. On some devices, these pins are shared with the device port pins, and this sharing of pins can complicate a design (or it may simply not be possible to do so). As an alternative to using the JTAG pins, most MSP430Fxxx device ...

... The JTAG pins provide access to the Flash memory of the MSP430Fxxx devices. On some devices, these pins are shared with the device port pins, and this sharing of pins can complicate a design (or it may simply not be possible to do so). As an alternative to using the JTAG pins, most MSP430Fxxx device ...

Debugging a Dead Board

... • JTAG provides the capability to test interconnects on a PC-board without physical test probes or test fixtures • Does not require the board to be in a bootable state for fault diagnostics • JTAG allows In-System Programming of devices such as Flash, CPLDs, FPGAs and Serial EEPROMs ...

... • JTAG provides the capability to test interconnects on a PC-board without physical test probes or test fixtures • Does not require the board to be in a bootable state for fault diagnostics • JTAG allows In-System Programming of devices such as Flash, CPLDs, FPGAs and Serial EEPROMs ...

Datasheet - Adafruit

... Description The ST-LINK/V2 is an in-circuit debugger and programmer for the STM8 and STM32 microcontroller families. The single wire interface module (SWIM) and JTAG/serial wire debugging (SWD) interfaces are used to communicate with any STM8 or STM32 microcontroller located on an application board. ...

... Description The ST-LINK/V2 is an in-circuit debugger and programmer for the STM8 and STM32 microcontroller families. The single wire interface module (SWIM) and JTAG/serial wire debugging (SWD) interfaces are used to communicate with any STM8 or STM32 microcontroller located on an application board. ...

MDTMonConPres

... Analog and digital power supply voltage regulators: 2 floating wire pairs to CSM: measure 3.3V levels Temperature on the Mezzanine card: 1 temp sensor (Dallas DS1722) digital with simple serial bus, readout via JTAG b) How often must the sensors be read out (e.g. continuously, each run, daily et ...

... Analog and digital power supply voltage regulators: 2 floating wire pairs to CSM: measure 3.3V levels Temperature on the Mezzanine card: 1 temp sensor (Dallas DS1722) digital with simple serial bus, readout via JTAG b) How often must the sensors be read out (e.g. continuously, each run, daily et ...

Advanced JTAG Configuration Tips for Xilinx FPGAs

... Route the JTAG signals together and away from other high-frequency signals. Provide a ground path return and route the signals using defined impedance routes. Consider terminating the JTAG signals to avoid ringing, particularly TCK. Several types of terminations can be used, but note that the Platfo ...

... Route the JTAG signals together and away from other high-frequency signals. Provide a ground path return and route the signals using defined impedance routes. Consider terminating the JTAG signals to avoid ringing, particularly TCK. Several types of terminations can be used, but note that the Platfo ...

Customer story “JTAG Technologies helped develop the opti

... test coverage of circa 75% would still be possible. The solution devised was a dedicated test card that mates with the 200-pin edge connector of the processor card. The test card has two JTAG headers – one to access the Atmel device, the other to control boundary-scan devices that connect to the edg ...

... test coverage of circa 75% would still be possible. The solution devised was a dedicated test card that mates with the 200-pin edge connector of the processor card. The test card has two JTAG headers – one to access the Atmel device, the other to control boundary-scan devices that connect to the edg ...