AD7910 数据手册DataSheet下载

... speed, low power, successive approximation ADCs. The parts operate from a single 2.35 V to 5.25 V power supply and feature throughput rates up to 250 kSPS. The parts contain a low noise, wide bandwidth track-and-hold amplifier that can handle input frequencies in excess of 13 MHz. ...

... speed, low power, successive approximation ADCs. The parts operate from a single 2.35 V to 5.25 V power supply and feature throughput rates up to 250 kSPS. The parts contain a low noise, wide bandwidth track-and-hold amplifier that can handle input frequencies in excess of 13 MHz. ...

MAX5098A Dual, 2.2MHz, Automotive Buck or Boost Converter with 80V Load-Dump Protection

... series protection MOSFET absorbs the high voltage transient to prevent damage to lower voltage components. The DC-DC converters operate over a wide operating voltage range from 4.5V to 19V. The MAX5098A operates 180° out-of-phase with an adjustable switching frequency to minimize external components ...

... series protection MOSFET absorbs the high voltage transient to prevent damage to lower voltage components. The DC-DC converters operate over a wide operating voltage range from 4.5V to 19V. The MAX5098A operates 180° out-of-phase with an adjustable switching frequency to minimize external components ...

Mehedi Hasan Tusher

... Every Electronic circuit is assumed to operate some supply voltage which is usually assumed to be constant in nature. A voltage regulator is a power electronic circuit that maintains a constant output voltage irrespective of change in load current or line voltage. Many different types of voltage reg ...

... Every Electronic circuit is assumed to operate some supply voltage which is usually assumed to be constant in nature. A voltage regulator is a power electronic circuit that maintains a constant output voltage irrespective of change in load current or line voltage. Many different types of voltage reg ...

Analytical and Practical Analysis of Switched-Capacitor DC

... power levels. These functions include doubling, halving and inverting the input voltage, and can be combined to achieve other conversion ratios. Typical applications include RS232 level converters and FLASH memory programming voltage generators. These standard converters are often unregulated or sup ...

... power levels. These functions include doubling, halving and inverting the input voltage, and can be combined to achieve other conversion ratios. Typical applications include RS232 level converters and FLASH memory programming voltage generators. These standard converters are often unregulated or sup ...

AD7982 数据手册DataSheet下载

... when CNV is low. In chain mode, the data should be read when CNV is high. Serial Data Output. The conversion result is output on this pin. It is synchronized to SCK. Serial Data Clock Input. When the part is selected, the conversion result is shifted out by this clock. Serial Data Input. This input ...

... when CNV is low. In chain mode, the data should be read when CNV is high. Serial Data Output. The conversion result is output on this pin. It is synchronized to SCK. Serial Data Clock Input. When the part is selected, the conversion result is shifted out by this clock. Serial Data Input. This input ...

Article - Power Electronics and Drives

... balance dynamics is improved by the use of modified PS-PWM. The method proposed in [33] is based on a switch-state sequences modification and can be achieved using carriers. Aside from the PS PWM technique, other PWM strategies can be attractive from the standpoint of output voltage harmonic content ...

... balance dynamics is improved by the use of modified PS-PWM. The method proposed in [33] is based on a switch-state sequences modification and can be achieved using carriers. Aside from the PS PWM technique, other PWM strategies can be attractive from the standpoint of output voltage harmonic content ...

UNIT-V DAC: Principles – weighted-resistor network, R

... output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times all ...

... output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times all ...

AD7911 数据手册DataSheet下载

... Data In. Logic input. The channel to be converted is provided on this input and is clocked into an internal register on the falling edge of SCLK. Serial Clock. Logic input. SCLK provides the serial clock for accessing data from the part. This clock input is also used as the clock source for the AD79 ...

... Data In. Logic input. The channel to be converted is provided on this input and is clocked into an internal register on the falling edge of SCLK. Serial Clock. Logic input. SCLK provides the serial clock for accessing data from the part. This clock input is also used as the clock source for the AD79 ...

Adaptive predictive error filter-based maximum power point tracking

... that should tolerate these internal uncertainties or external disturbances such that the voltage fluctuation in vpv can be reduced in view of obtaining a controller for harvesting maximum available power in a PV system. It is observed that PI and proportional integral and derivative (PID)controller a ...

... that should tolerate these internal uncertainties or external disturbances such that the voltage fluctuation in vpv can be reduced in view of obtaining a controller for harvesting maximum available power in a PV system. It is observed that PI and proportional integral and derivative (PID)controller a ...

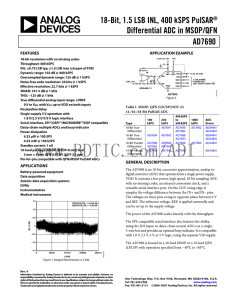

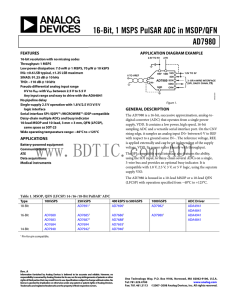

18-Bit, 1.5 LSB INL, 400 kSPS PulSAR Differential ADC in MSOP/QFN AD7690

... ADA4941 ADA4841 ADA4941 ADA4841 ADA4841 ...

... ADA4941 ADA4841 ADA4941 ADA4841 ADA4841 ...

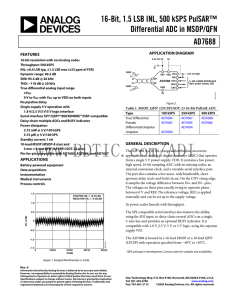

AD7688 数据手册DataSheet下载

... The AD7688 is a 16-bit, charge redistribution, successive approximation, analog-to-digital converter (ADC) that operates from a single 5 V power supply, VDD. It contains a low power, high speed, 16-bit sampling ADC with no missing codes, an internal conversion clock, and a versatile serial interface ...

... The AD7688 is a 16-bit, charge redistribution, successive approximation, analog-to-digital converter (ADC) that operates from a single 5 V power supply, VDD. It contains a low power, high speed, 16-bit sampling ADC with no missing codes, an internal conversion clock, and a versatile serial interface ...

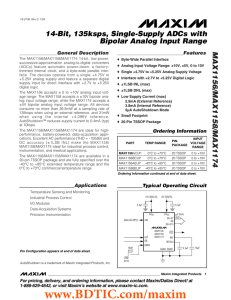

MAX1156/MAX1158/MAX1174 14-Bit, 135ksps, Single-Supply ADCs with Bipolar Analog Input Range General Description

... Figure 1. Load Circuits ...

... Figure 1. Load Circuits ...

MAX1179/MAX1187/MAX1189 16-Bit, 135ksps, Single-Supply ADCs with Bipolar Analog Input Range General Description

... The MAX1179/MAX1187/MAX1189 use a successiveapproximation (SAR) conversion technique with an inherent track-and-hold (T/H) stage to convert an analog input into a 16-bit digital output. Parallel outputs provide a high-speed interface to microprocessors (µPs). The Functional Diagram at the end of the ...

... The MAX1179/MAX1187/MAX1189 use a successiveapproximation (SAR) conversion technique with an inherent track-and-hold (T/H) stage to convert an analog input into a 16-bit digital output. Parallel outputs provide a high-speed interface to microprocessors (µPs). The Functional Diagram at the end of the ...

A 6.25 Gb/s Voltage-Time Conversion Based Fractionally Spaced

... 6.25 Gb/s rate, 3.6 mW/Gb/s efficiency and over 4 bits of linearity. Index Terms—Fractionally spaced linear receive equalization, high-speed links, modified sign-sign LMS algorithm, voltage-time conversion technique. ...

... 6.25 Gb/s rate, 3.6 mW/Gb/s efficiency and over 4 bits of linearity. Index Terms—Fractionally spaced linear receive equalization, high-speed links, modified sign-sign LMS algorithm, voltage-time conversion technique. ...

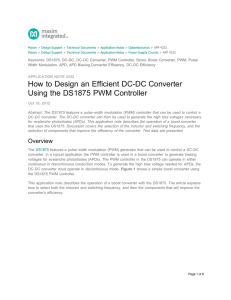

Maxim Design Support Technical Documents Application Notes

... The first method is to reduce the inductor current, thus reducing the resistive losses of the inductor and transistor. The second method is to reduce the switching period of the system. Inductor current can be reduced in a DC-DC converter by increasing the size of the inductor and the duty cycle at ...

... The first method is to reduce the inductor current, thus reducing the resistive losses of the inductor and transistor. The second method is to reduce the switching period of the system. Inductor current can be reduced in a DC-DC converter by increasing the size of the inductor and the duty cycle at ...

Contents 1 How to Read this Design Guide IVS 102 Design Guide

... In no event shall Armstrong be liable for direct, indirect, special, incidental, or consequential damages arising out of the use, or the inability to use information contained in this manual, even if advised of the possibility of such damages. In particular, Armstrong is not responsible for any cost ...

... In no event shall Armstrong be liable for direct, indirect, special, incidental, or consequential damages arising out of the use, or the inability to use information contained in this manual, even if advised of the possibility of such damages. In particular, Armstrong is not responsible for any cost ...

ADS8201 数据资料 dataSheet 下载

... converter linearity to not meet its stated specifications. To minimize noise, use low bandwidth input signals with low-pass filters. Care should also be taken to ensure that the output impedance of the sources driving the +IN and –IN inputs are matched. If this matching is not observed, the two inpu ...

... converter linearity to not meet its stated specifications. To minimize noise, use low bandwidth input signals with low-pass filters. Care should also be taken to ensure that the output impedance of the sources driving the +IN and –IN inputs are matched. If this matching is not observed, the two inpu ...

AD7980 数据手册DataSheet下载

... In chain mode, the data should be read when CNV is high. Serial Data Output. The conversion result is output on this pin. It is synchronized to SCK. Serial Data Clock Input. When the part is selected, the conversion result is shifted out by this clock. Serial Data Input. This input provides multiple ...

... In chain mode, the data should be read when CNV is high. Serial Data Output. The conversion result is output on this pin. It is synchronized to SCK. Serial Data Clock Input. When the part is selected, the conversion result is shifted out by this clock. Serial Data Input. This input provides multiple ...

AD7475 数据手册DataSheet下载

... The AD7475/AD74951 are 12-bit, high speed, low power, successive-approximation ADCs that operate from a single 2.7 V to 5.25 V power supply with throughput rates up to 1 MSPS. They contain a low noise, wide bandwidth track-andhold amplifier that can handle input frequencies above 1 MHz. The conversi ...

... The AD7475/AD74951 are 12-bit, high speed, low power, successive-approximation ADCs that operate from a single 2.7 V to 5.25 V power supply with throughput rates up to 1 MSPS. They contain a low noise, wide bandwidth track-andhold amplifier that can handle input frequencies above 1 MHz. The conversi ...

Chapter 9 Zero-Voltage or Zero-Current Switchings

... – Voltage over switch is limited to the supply voltage ...

... – Voltage over switch is limited to the supply voltage ...

SIMULATION OF A SERIES HALF BRIDGE LLC RESONANT CIRCUIT

... dissipation as the circuit above. For detailed information on this conversion, please refer to International Rectifier’s application note AN-1160. ...

... dissipation as the circuit above. For detailed information on this conversion, please refer to International Rectifier’s application note AN-1160. ...

Power Factor Improvement Using Single Phase Bridgeless Cuk

... Converter (SEPIC) topology [9] have been also introduced but it has its own disadvantage of discontinuous output current resulting in a relatively high output ripple. The next topology used for the low input applications is the Cuk converter. It offers several advantages in PFC applications, such as ...

... Converter (SEPIC) topology [9] have been also introduced but it has its own disadvantage of discontinuous output current resulting in a relatively high output ripple. The next topology used for the low input applications is the Cuk converter. It offers several advantages in PFC applications, such as ...

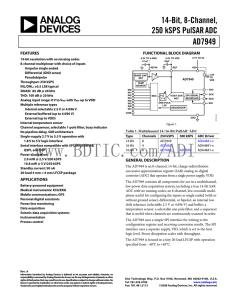

AD7949 数据手册DataSheet下载

... See the Terminology section. These specifications include full temperature range variation but not the error contribution from the external reference. ...

... See the Terminology section. These specifications include full temperature range variation but not the error contribution from the external reference. ...

Test bed for Selecting Optimum Sequences for

... properties, sharp synchronization peaks and lower false detection probability. In 1990, M Grayson and M Darnell reported that bipolar sequences developed by R H Barker posses excellent autocorrelation functions which are either zero or negative at all time shifts except zero and can be considered as ...

... properties, sharp synchronization peaks and lower false detection probability. In 1990, M Grayson and M Darnell reported that bipolar sequences developed by R H Barker posses excellent autocorrelation functions which are either zero or negative at all time shifts except zero and can be considered as ...