Final Exam 2015/2016 i File - e

... |AVD,diff| = |(vo1 – vo2)/(vi1 – vi2)| = 5. For all transistors, channel length L = 2 μm. In all calculations, ignore body effect and channel length modulation. (a) Determine W5, the channel width for M5, to set ISS = 100 μA. Assume overdrive voltage for M5 is 0.25 V. ...

... |AVD,diff| = |(vo1 – vo2)/(vi1 – vi2)| = 5. For all transistors, channel length L = 2 μm. In all calculations, ignore body effect and channel length modulation. (a) Determine W5, the channel width for M5, to set ISS = 100 μA. Assume overdrive voltage for M5 is 0.25 V. ...

UNISONIC TECHNOLOGIES CO., LTD LMH358

... operational amplifier.This circuit consists of two independent, high gain, internally frequency compensated operational amplifiers. The input common mode range of the UTC LMH358 can be beyond the rails. The UTC LMH358 are with rail-to-rails output voltage swing. The quiescent current is 500µA per am ...

... operational amplifier.This circuit consists of two independent, high gain, internally frequency compensated operational amplifiers. The input common mode range of the UTC LMH358 can be beyond the rails. The UTC LMH358 are with rail-to-rails output voltage swing. The quiescent current is 500µA per am ...

Unit 2

... – Referred to as metric units of measure • Part of the SI (System Internationale) system ...

... – Referred to as metric units of measure • Part of the SI (System Internationale) system ...

NOT gate

... whereas adders manipulate inputs to produce outputs, memory circuits must maintain values over time the simplest circuit for storing a value is known as a flip-flop it can be set to store a 1 by applying current on an input wire it can be reset to store a 0 by applying current on another input w ...

... whereas adders manipulate inputs to produce outputs, memory circuits must maintain values over time the simplest circuit for storing a value is known as a flip-flop it can be set to store a 1 by applying current on an input wire it can be reset to store a 0 by applying current on another input w ...

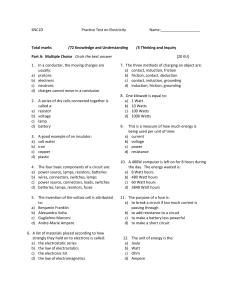

Practice Unit Test - hhs-snc1d

... the day. The energy wasted is: a) 8 Watt hours b) 480 Watt hours c) 60 Watt hours d) 3840 Watt hours 11. The purpose of a fuse is: a) to break a circuit if too much current is passing through b) to add resistance to a circuit c) to make a battery less powerful d) to make a short circuit ...

... the day. The energy wasted is: a) 8 Watt hours b) 480 Watt hours c) 60 Watt hours d) 3840 Watt hours 11. The purpose of a fuse is: a) to break a circuit if too much current is passing through b) to add resistance to a circuit c) to make a battery less powerful d) to make a short circuit ...

the original file

... symmetrical rising and falling edges. There is also a phase shift to the right (latent output signal) of the opamp feedback circuit. The tradeoffs are higher frequency and in phase signal response but slightly lower gain, clipping level and non-symmetrical distortion for the non-opamp circuit. On th ...

... symmetrical rising and falling edges. There is also a phase shift to the right (latent output signal) of the opamp feedback circuit. The tradeoffs are higher frequency and in phase signal response but slightly lower gain, clipping level and non-symmetrical distortion for the non-opamp circuit. On th ...

EEEE 482 Lab2_Rev2015_2 - RIT - People

... voltage gain and its common mode rejection. This is typically followed by a common emitter stage (high voltage gain) to allow for a much larger overall gain. The final stage is acommon collector output stage that is used as an impedance buffer. Although it has approximately unity voltage gain, it is ...

... voltage gain and its common mode rejection. This is typically followed by a common emitter stage (high voltage gain) to allow for a much larger overall gain. The final stage is acommon collector output stage that is used as an impedance buffer. Although it has approximately unity voltage gain, it is ...

JFET Single Stage Amplifier Phys 3610/6610 Lab 21 Student: TA:

... Task 1: Use the 2N5485 n-channel JFET as in fig.1 to make a simple amplifier. The circuit should use VDD = +12 V, VSS = −12 V, VD = (6 ± 1) V, and ID = (1.0 ± 0.2) mA. Design the biasing needed for these parameters, calculate the circuit gain for your circuit design, and compare with the measured va ...

... Task 1: Use the 2N5485 n-channel JFET as in fig.1 to make a simple amplifier. The circuit should use VDD = +12 V, VSS = −12 V, VD = (6 ± 1) V, and ID = (1.0 ± 0.2) mA. Design the biasing needed for these parameters, calculate the circuit gain for your circuit design, and compare with the measured va ...

A Very–High Impedance Current Mirror

... voltage allows designing analog circuits that can operate around 1 V. However, the shrinking of the supply voltage combined with the low output resistance of transistors in these deep sub-micron CMOS processes make it very difficult to implement current mirrors (CMs) and current sources or sinks tha ...

... voltage allows designing analog circuits that can operate around 1 V. However, the shrinking of the supply voltage combined with the low output resistance of transistors in these deep sub-micron CMOS processes make it very difficult to implement current mirrors (CMs) and current sources or sinks tha ...

A Simple Pressure Sensor Signal Conditioning Circuit

... As seen in Table 1, a large deviation from the optimum feedback resistance of 100 k is tolerable while maintaining transducer interchangeability. For the optimum feedback resistance (100 k), calibration accuracy is a function of the accuracy of the excitation current, feedback resistors and sensor t ...

... As seen in Table 1, a large deviation from the optimum feedback resistance of 100 k is tolerable while maintaining transducer interchangeability. For the optimum feedback resistance (100 k), calibration accuracy is a function of the accuracy of the excitation current, feedback resistors and sensor t ...