Liebert eXL Installation Manual – 625-800kVA, 1.0PF, 60Hz, Three-Phase, Single-Module ®

... This UPS has several circuits that are energized with high DC as well as AC voltages. Check for voltage with both AC and DC voltmeters before working within the UPS. Check for voltage with both AC and DC voltmeters before making contact. Only properly trained and qualified personnel wearing appropri ...

... This UPS has several circuits that are energized with high DC as well as AC voltages. Check for voltage with both AC and DC voltmeters before working within the UPS. Check for voltage with both AC and DC voltmeters before making contact. Only properly trained and qualified personnel wearing appropri ...

IU-JEEE

... need of knowledge of line parameters, assuming synchronization problem is solved. Obvious next step is to develop a fault location algorithm without requirement of synchronization and line parameters setting. Short lines unsymmetrical faults have been covered by the method presented in [7]. More com ...

... need of knowledge of line parameters, assuming synchronization problem is solved. Obvious next step is to develop a fault location algorithm without requirement of synchronization and line parameters setting. Short lines unsymmetrical faults have been covered by the method presented in [7]. More com ...

Old Company Name in Catalogs and Other Documents

... technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Ele ...

... technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Ele ...

Power Optimization for Ripple Carry Adder with Reduced

... Addition process can be used as a basic block for combination of all arithmetic setups. The binary adder becomes an essential hardware component. Even though many researches related with the binary adder structures are selected, their studies showed their comparative performance, area, power analysi ...

... Addition process can be used as a basic block for combination of all arithmetic setups. The binary adder becomes an essential hardware component. Even though many researches related with the binary adder structures are selected, their studies showed their comparative performance, area, power analysi ...

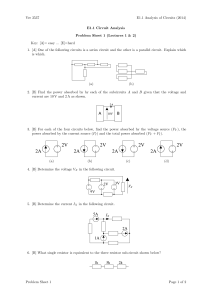

E1.1 Circuit Analysis Problem Sheet 1

... 2. For subcircuit B the voltage and current correspond to the passive sign convention (i.e. the current arrow in the opposite direction to the voltage arrow) and so the power absorbed by B is given by V × I = 20 W. For device A we need to reverse the direction of the current to conform to the passiv ...

... 2. For subcircuit B the voltage and current correspond to the passive sign convention (i.e. the current arrow in the opposite direction to the voltage arrow) and so the power absorbed by B is given by V × I = 20 W. For device A we need to reverse the direction of the current to conform to the passiv ...

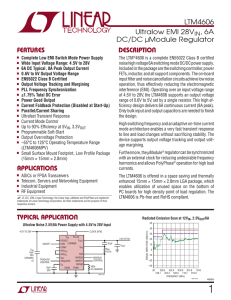

LTM4606 - High Efficiency Buck-Boost DC/DC uModule

... VOUT (Bank 3): Power Output Pins. Apply output load between these pins and PGND pins. Recommend placing output decoupling capacitance directly between these pins and PGND pins (see figure below). PGND (Bank 2): Power Ground Pins for Both Input and Output Returns. VD (Pins B7, C7): Top FET Drain Pins ...

... VOUT (Bank 3): Power Output Pins. Apply output load between these pins and PGND pins. Recommend placing output decoupling capacitance directly between these pins and PGND pins (see figure below). PGND (Bank 2): Power Ground Pins for Both Input and Output Returns. VD (Pins B7, C7): Top FET Drain Pins ...

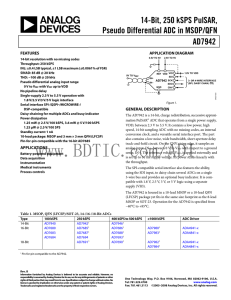

AD7942 数据手册DataSheet下载

... and selects the interface mode of the part: chain mode or CS mode. In CS mode, CNV enables the SDO pin when low. In chain mode, the data should be read when CNV is high. Serial Data Output. The conversion result is output on this pin. It is synchronized to SCK. Serial Data Clock Input. When the part ...

... and selects the interface mode of the part: chain mode or CS mode. In CS mode, CNV enables the SDO pin when low. In chain mode, the data should be read when CNV is high. Serial Data Output. The conversion result is output on this pin. It is synchronized to SCK. Serial Data Clock Input. When the part ...

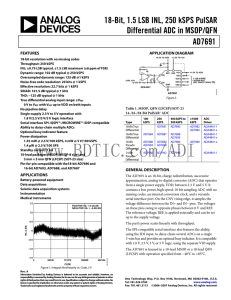

18-Bit, 1.5 LSB INL, 250 kSPS PulSAR Differential ADC in MSOP/QFN AD7691

... Deleted QFN Package in Development References .......Universal Changes to Features, Applications, Figure 1 and Figure 2 .......... 1 Changes to Accuracy, Table 2.......................................................... 3 Changes to Power Dissipation, Table 3......................................... ...

... Deleted QFN Package in Development References .......Universal Changes to Features, Applications, Figure 1 and Figure 2 .......... 1 Changes to Accuracy, Table 2.......................................................... 3 Changes to Power Dissipation, Table 3......................................... ...

Chapter 3 Special-Purpose Diodes

... to point C, the reverse-bias voltage from gate to drain (VGD) produces a depletion region large enough to offset the increase in VDS, thus keeping ID relatively constant. The drain characteristic curve of a JFET for VGS = 0 showing pinch-off. ...

... to point C, the reverse-bias voltage from gate to drain (VGD) produces a depletion region large enough to offset the increase in VDS, thus keeping ID relatively constant. The drain characteristic curve of a JFET for VGS = 0 showing pinch-off. ...

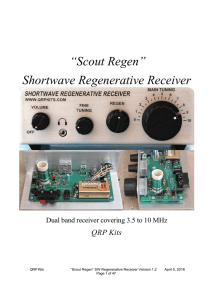

“Scout Regen” Shortwave Regenerative Receiver

... Figure 21. Lead forming for R7 and R10 ...........................................................................................................17 Figure 22. Resistor bodies R7, R10 flush with the PC board...........................................................................17 Figure 23. Ori ...

... Figure 21. Lead forming for R7 and R10 ...........................................................................................................17 Figure 22. Resistor bodies R7, R10 flush with the PC board...........................................................................17 Figure 23. Ori ...

ADM690 数据手册DataSheet 下载

... layer capacitors, can also be used for short-term memory back up. A small charging current of typically 10 nA (0.1 µA max) flows out of the VBATT terminal. This current is useful for maintaining rechargeable batteries in a fully charged condition. This extends the life of the back up battery by comp ...

... layer capacitors, can also be used for short-term memory back up. A small charging current of typically 10 nA (0.1 µA max) flows out of the VBATT terminal. This current is useful for maintaining rechargeable batteries in a fully charged condition. This extends the life of the back up battery by comp ...

LTM4611 - Ultralow VIN, 15A DC/DC uModule Regulator

... The LTM®4611 is a high density 15A output, switch mode DC/DC buck converter power supply capable of operating from very low voltage input supplies. Included in the package are the buck switching controller, power FETs, inductor and loop-compensation components. The LTM4611 delivers up to 15A continu ...

... The LTM®4611 is a high density 15A output, switch mode DC/DC buck converter power supply capable of operating from very low voltage input supplies. Included in the package are the buck switching controller, power FETs, inductor and loop-compensation components. The LTM4611 delivers up to 15A continu ...

MAX509/MAX510 Quad, Serial 8-Bit DACs with Rail-to-Rail Outputs _______________General Description

... REF_....................................................(VSS - 0.3V), (VDD + 0.3V) OUT_..............................................................................VDD, VSS Maximum Current into Any Pin............................................50mA Continuous Power Dissipation (TA = +70°C) 16-Pin ...

... REF_....................................................(VSS - 0.3V), (VDD + 0.3V) OUT_..............................................................................VDD, VSS Maximum Current into Any Pin............................................50mA Continuous Power Dissipation (TA = +70°C) 16-Pin ...

MAX9381 Lowest Power 3.0GHz ECL/PECL Differential Data and Clock D Flip-Flop General Description

... clock, provided the minimum setup and hold times are met. By interchanging the CLK and CLK inputs, the flipflop functions as a falling-edge triggered flip-flop. The input signals (D, D and CLK, CLK) are differential and have a maximum differential input voltage of 3.0V or VCC - VEE, whichever is les ...

... clock, provided the minimum setup and hold times are met. By interchanging the CLK and CLK inputs, the flipflop functions as a falling-edge triggered flip-flop. The input signals (D, D and CLK, CLK) are differential and have a maximum differential input voltage of 3.0V or VCC - VEE, whichever is les ...

Down-Conversion Receiver with Continuous-Time EA Modulation

... This thesis describes the design and implementation of an optical-electrical subsampling down-conversion receiver that employs EA modulation. Accurate subsampling of an electrical RF signal in the optical domain is achieved by using a low-jitter mode-locked-laser and a high-bandwidth interferometer. ...

... This thesis describes the design and implementation of an optical-electrical subsampling down-conversion receiver that employs EA modulation. Accurate subsampling of an electrical RF signal in the optical domain is achieved by using a low-jitter mode-locked-laser and a high-bandwidth interferometer. ...

$doc.title

... Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditi ...

... Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditi ...

PCAL9535A 1. General description Low-voltage 16-bit I

... In addition to providing a flexible set of GPIOs, the wide VDD range of 1.65 V to 5.5 V allows the PCAL9535A to interface with next-generation microprocessors and microcontrollers where supply levels are dropping down to conserve power. The PCAL9535A contains the PCA9535 register set of four pairs o ...

... In addition to providing a flexible set of GPIOs, the wide VDD range of 1.65 V to 5.5 V allows the PCAL9535A to interface with next-generation microprocessors and microcontrollers where supply levels are dropping down to conserve power. The PCAL9535A contains the PCA9535 register set of four pairs o ...